Escolar Documentos

Profissional Documentos

Cultura Documentos

Evolução Das CPUs - Dual e Quad Core

Enviado por

Josenilton De Aragão LimaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Evolução Das CPUs - Dual e Quad Core

Enviado por

Josenilton De Aragão LimaDireitos autorais:

Formatos disponíveis

Evoluo das CPUs: Dual e Quad Core

Cesar Sposito Mrio J. Filho Rodrigo Ferrassa

EACH

... os computadores sequenciais esto se aproximando do limite fsico fundamental em sua energia potencial computacional. Tal limite a velocidade da luz... Angel L. DeCegama

EACH

Introduo Limite: Pentium IV

Desafio: Aumento frequncia de clock. Corrida por clock (Intel X AMD). Athlon Thunderbird X Pentium III. Intel: Movimento arriscado. Investimento em um processador com um longo pipeline. Pentium IV.

EACH

Pentium IV: longo pipeline

Pipeline uma tcnica de hardware que permite que a CPU realize a busca de uma ou mais instrues alm da prxima a ser executada. Pentium III: 10 estgios. Pentium IV: 20 estgios a 31 estgios. Dobrar o nmero de estgios no processador como dobrar o nmero de funcionrios de uma empresa.

EACH

Longo pipeline: Consequencias

Com mais estgios, o processador seria capaz de atingir freqncias mais altas. Adicionar mais estgios tornou o processador menos eficiente, pois as instrues precisavam do dobro do nmero de ciclos do processador para serem processadas. Possuir o dobro de estgios significa tambm possuir aproximadamente o dobro de transistores e consumir o dobro da eletricidade.

EACH

Mais consumo Maior aquecimento

Maior consumo gera maiores desperdcios. Maior desperdicio gera maiores aquecimentos. A dissipao trmica (W/cm^2) de um Pentium 4, prximo do ncleo de um reator nuclear. Se a produo de processadores continuasse da mesma forma, num futuro no muito distante, teramos um processador com dissipao trmica prxima a da superfcie solar.

EACH

Aquecimento

Fonte: http://blogs.intel.com

EACH

A barreira dos 3.4 GHZ

Desde 1983 at 2002, as taxas de frequncia de clock aumentaram de 5 MHz para 3 GHz. Aumento do clock 600 X em 19 anos. Na poca, a Intel previa alcanar 5.2 GHz no final de 2004 e planos para 10 GHz no final de 2005. Porm, nada disso aconteceu. Os 3.4 GHz se tornaram uma barreira difcil de transpor. Fim da Lei de Moore?

Hyper Treading: Inicio do processamento paralelo

EACH

Hyper Treading: simula em um nico processador fsico dois processadores lgicos. Pode melhorar desempenho de at 30% Utiliza as partes ociosas dos recursos para simular dois ncleos.

EACH

Evoluo

Elevando, por exemplo, em 20% a freqncia do processador, aumentamos apenas em 13% o seu desempenho e como efeito colateral, tambm passa a consumir 73% mais energia. Recproca verdadeira.

EACH

Estratgia

Reduzindo a freqncia em 20%, perdemos apenas 13% de desempenho e reduzimos em 49% o consumo de energia. Se reduzssemos em 20% o clock e colocssemos dentro da mesma pastilha dois processadores?

EACH

Estratgia: Multiplos Ncleos

Teramos um processador de dois ncleos com 73% mais desempenho e consumindo praticamente a mesma coisa (~2% mais energia). Processadores multicore podem simultaneamente executar mltiplas tarefas computacionais.

EACH

Single-Core X Dual-Core

Fonte: http://blogs.intel.com

EACH

Nova Arquitetura

Caminhou bastante, porm para o lado e no para a frente (National Instruments).

NetBurst Core Pentium D Quad Core

Core 2 Duo Pentium IV

Pentium III

EACH

Arquitetura Core

Somando-se a estratgia de lanar processadores de mltiplos ncleos, a nova arquitetura interna do processador tambm foi importante. Maior eficincia de execuo de instrues por ciclo de CPU. Maior desempenho e menor consumo. A arquitetura Core consegue desempenho superior aos da microarquitetura Netburst (anterior) com o clock muito inferior.

EACH

Arquitetura Core

Derivada do Pentium III Pentium M. Pipeline de 14 estgios. Cache de memria L2 compartilhado. Pr-buscas so compartilhadas, se o controlador de cache carregar um bloco de dados para ser usado pelo primeiro ncleo, o segundo ncleo tambm pode usar o dado j carregado. Aprimoramento da unidade de pr-busca do processador (Melhor Chute).

EACH

Arquitetura Core

Quanto menor o nmero de instrues a serem executadas, mais rpido o computador realizar a execuo da tarefa alm de consumir menos. O decodificador de instrues do Pentium IV pode decodificar trs instrues por pulso de clock, j o do Core 2 Duo (Arquitetura Core) 4.

EACH

Arquitetura Core

Novo conceito: Fuso de instrues

load eax, [mem1] cmp eax, [mem2] jne target

load eax, [mem1] cmp eax, [mem2] + jne target

Graas ao conceito de fuso de instrues o decodificador de instrues da arquitetura Core consegue fundir 2 instruoes enviar 5 por pulso de clock.

EACH

Arquitetura Core

E mais! Unidade de ponto flutuante (FPU) e uma unidade lgica e aritmtica (ALU) extras. Caminho de dados real de 128 bits. Desambiguao de memria. Chaveamento Eltrico Avanado. Etc.

EACH

Quad Core

EACH

Quad Core

- uma das verses de processadores da Intel mais recente apresentada com ncleos Kentsfield(65nm) e Yorkfield(45nm). - O clock pode alcanar at 3.33Ghz. Em overclocking, com cooler de ar, at 4.0Ghz, e na gua at 5Ghz. - Exemplos: Core 2 Quad, Core 2 Extreme: quad-core, Quad-Core Xeon.

EACH

Quad Core

- Multi-Chip: Duas pastilhas de silcio (1 ncleo em cada) encapsuladas junto: Comunicao externa . - Monoltica: Uma pastilha de silcio integra 2 ncleos encapsulados: Comunicao interna. - Monoltica Multi-Chip: Duas pastilhas de silcio (2 ncleos em cada) encapsuladas: Comunicao interna e externa.

EACH

Quad Core

EACH

Quad Core Jogos

EACH

Quad Core Jogos

EACH

Quad Core - Exemplos

EACH

Aquecimento: Netburst X Core

Pentium D

Pentium Extreme Edition

EACH

Aquecimento: Netburst X Core

Core 2 Duo

Core 2 Extreme

Core 2 Quad

EACH

Arquitetura Core Processadores

Dual/Quad/Six Core Xeon

EACH

Arquitetura Core Ncleos

EACH

AMD: Athlon 64 X2

Primeiro processador com dois ncleos da AMD. Deriva do Athlon 64.

EACH

AMD: Athlon 64 X2

EACH

AMD: Athlon 64 X2

EACH

AMD: Phenom X3/X4

Trs ou Quatro ncleos independentes. Os ncleos se comunicam internamente dentro da pastilha. Controlador de memria integrado. Tecnologia HT.

EACH

AMD: Phenom X3/X4

EACH

Consideraes Finais

Por 10 anos os aumentos de desempenho vieram custa do uso cada vez mais ineficiente do uso de energia. A partir de 2001, a taxa de crescimento de desempenho pareceu ter reduzido. Se essa diminuio ser ou no temporria ainda uma questo obscura. Arquitetos esto usando tcnicas cada vez mais complexas para tentar explorar mais paralelismo a nvel de instruo.

J L Hennessy e D A Patterson

EACH

Consideraes Finais

Com essa estratgia em mente, os fabricantes de processadores tem o desafio de continuar entregando a melhor relao desempenho/Watts. A Intel propem melhorar sempre, em um ano a microarquitetura, no ano seguinte a miniaturizao, e assim por diante.

EACH

Consideraes Finais

Fonte: http://blogs.intel.com

EACH

Consideraes Finais

2007 a Intel lana os primeiros processadores para servidores fabricados com a tecnologia de 45nm. 2008 foi o ano do Nehalem, que foi o nome cdigo da nova microarquitetura, que permitir um outro passo importante, para manter viva a Lei de Moore.

EACH

Consideraes Finais

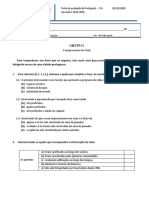

Processadores Futuros (Roadmaps) Arquitetura Processador Nehalem Westmere Sandy Bridge Haswell Core i7 Clock Processo Intel 2,6 - 3,2 Ghz 4 por padro 45nm 6 por padro 32nm 48 32nm 8 por padro 22nm AMD Barcelona Opteron Shanguai Opteron/Phenom Istambu Phenom Magny-Cours So Paulo 4 4 6 12 6 65nm 45nm 45nm 45nm 45nm 2mb 6mb 6mb 12mb 6mb 2008 2008/2009 2009 2010 2010 Ncleos Cache 1 a 8mb 1 a 12mb 8 a 24mb TDP Previso

130W 150W Novembro-08 2009/2010 2010/2011 2012

EACH

Bibliografia

J L Hennessy e D A Patterson HENSON Valerie Bookshelf: Ultimate Computation The Kernel Hacker's Physical Limits of

INTEL - http://www.intel.com/portugues/ products/ processor/index.htm BLOGS INTEL - http://blogs.intel.com FAPESP - http://www.agencia.fapesp.br NATIONAL INSTRUMENTS http://digital.ni.com/worldwide/brazil

EACH

Bibliografia

CLUBE DO HARDWARE http://www.clubedohardware.com.br/ PC FRUM - http://www.pcforum.com.br/ FRUM PC - http://forumpcs.ig.com.br/home Vasconcelos, Larcio Introduo aos processadores dual core e quad core

Você também pode gostar

- Livro Mapas Conceituais e Diagramas V CompletoDocumento103 páginasLivro Mapas Conceituais e Diagramas V CompletoLucas Boeira Michels100% (1)

- Fundamentos e Tecnologia de Realidade Virtual e Aumentada-V22-11-06 PDFDocumento422 páginasFundamentos e Tecnologia de Realidade Virtual e Aumentada-V22-11-06 PDFDivergente EtnegrevidAinda não há avaliações

- Lee ShulmanDocumento34 páginasLee ShulmanMayara Permanhane50% (2)

- Introdução À Filosofia de MarxDocumento128 páginasIntrodução À Filosofia de MarxponteslargoAinda não há avaliações

- E-Book 50 Olhares PDFDocumento108 páginasE-Book 50 Olhares PDFjkmilfont860Ainda não há avaliações

- Sonia CastellarDocumento14 páginasSonia CastellarJosenilton De Aragão LimaAinda não há avaliações

- Jovens, Ensino Médio e Politecnia PDFDocumento12 páginasJovens, Ensino Médio e Politecnia PDFEMYGDIODIASAinda não há avaliações

- 04 Estrutura Textual PDFDocumento21 páginas04 Estrutura Textual PDFMakunaima KulaAinda não há avaliações

- Tdah Uma Conversa Com EducadoresDocumento32 páginasTdah Uma Conversa Com EducadoresDebora Figueiredo100% (1)

- Frigotto Educacao e Trabalho Bases para DebaterDocumento17 páginasFrigotto Educacao e Trabalho Bases para DebaterJorlan Lima OliveiraAinda não há avaliações

- A Miseria Da Filosofia - Karl MarxDocumento98 páginasA Miseria Da Filosofia - Karl MarxSabrinaCortezAinda não há avaliações

- Aplicabilidade de Padrões de Engenharia deDocumento6 páginasAplicabilidade de Padrões de Engenharia dedeepsea_brAinda não há avaliações

- Analise de SistemasDocumento86 páginasAnalise de SistemasLuiz Fernando Reinoso100% (1)

- HardwareDocumento120 páginasHardwareCelso RochaAinda não há avaliações

- Analise de SistemasDocumento86 páginasAnalise de SistemasLuiz Fernando Reinoso100% (1)

- (Educacao) - Acacia Z Kuenzer - Educacao No Mundo AtualDocumento17 páginas(Educacao) - Acacia Z Kuenzer - Educacao No Mundo AtualRobson Santana SAinda não há avaliações

- Livro NIED 2018 Final PDFDocumento408 páginasLivro NIED 2018 Final PDFFernandoAinda não há avaliações

- Art07 PDFDocumento4 páginasArt07 PDFJosenilton De Aragão LimaAinda não há avaliações

- Analise de SistemasDocumento86 páginasAnalise de SistemasLuiz Fernando Reinoso100% (1)

- Modelos de ProcessoDocumento75 páginasModelos de ProcessoJosenilton De Aragão LimaAinda não há avaliações

- IHC e Engenharia de SoftwareDocumento8 páginasIHC e Engenharia de SoftwareJosenilton De Aragão LimaAinda não há avaliações

- Usabilidade Dos Jogos - A Experiência Do Virtual Team, UFPEDocumento9 páginasUsabilidade Dos Jogos - A Experiência Do Virtual Team, UFPEVitor FerreiraAinda não há avaliações

- Texto1 PDFDocumento1 páginaTexto1 PDFJosenilton De Aragão LimaAinda não há avaliações

- Apostila Java UnicampDocumento131 páginasApostila Java UnicampLuis Claudinei de MoraesAinda não há avaliações

- AnaliseestruturadaDocumento44 páginasAnaliseestruturadaJosenilton De Aragão LimaAinda não há avaliações

- 20 - Diagrama de ContextoDocumento5 páginas20 - Diagrama de ContextoLuiz Gustavo CorreiaAinda não há avaliações

- 1090 - Profissionais de TIDocumento16 páginas1090 - Profissionais de TIgeorgelima1Ainda não há avaliações

- ACF1BDocumento155 páginasACF1BJosenilton De Aragão LimaAinda não há avaliações

- Diagrama Fluxo DadosDocumento7 páginasDiagrama Fluxo DadosporcaprenhaAinda não há avaliações

- Tecnicas de Analise de SistemaDocumento34 páginasTecnicas de Analise de SistemaJosimar LimaAinda não há avaliações

- Jantar Dos FilosofosDocumento4 páginasJantar Dos FilosofosMoçambicano GuiguiguiAinda não há avaliações

- 2012 ArchiNews24 PROMONTORIODocumento139 páginas2012 ArchiNews24 PROMONTORIOFrancisco PereiraAinda não há avaliações

- SPT - Decourt-QuaresmaDocumento7 páginasSPT - Decourt-QuaresmaRandall Stevens0% (2)

- 04 - AA - Art NouveauDocumento10 páginas04 - AA - Art NouveauIara M. S. ZanattaAinda não há avaliações

- Aula 1 - Cobertura PDFDocumento23 páginasAula 1 - Cobertura PDFKlayrton TecynhaAinda não há avaliações

- Instalando Fontes em Grego e HebraicoDocumento3 páginasInstalando Fontes em Grego e HebraicoSandra SilvaAinda não há avaliações

- Orçamento SudecoDocumento18 páginasOrçamento SudecojoseAinda não há avaliações

- Word 2000 - SebentaDocumento55 páginasWord 2000 - SebentafilipaschoolAinda não há avaliações

- Carta PropostaDocumento2 páginasCarta PropostaowagnernAinda não há avaliações

- Mundo Apto Books - Praça Da Sé - CentralDocumento50 páginasMundo Apto Books - Praça Da Sé - CentralOsvaldo da Conceição NetoAinda não há avaliações

- 2º Teste - 2º PeríodoDocumento10 páginas2º Teste - 2º PeríodoAntonio FerreiraAinda não há avaliações

- Mini Apostila Telhados PDFDocumento9 páginasMini Apostila Telhados PDFHigor RairAinda não há avaliações

- 5 - Aula 5 - Vistas OrtograficasDocumento38 páginas5 - Aula 5 - Vistas OrtograficasDaniele VianaAinda não há avaliações

- Loa 2014 PDFDocumento439 páginasLoa 2014 PDFwaltervix1047Ainda não há avaliações

- Ciencia e Conservacao Jan 2014 PDFDocumento334 páginasCiencia e Conservacao Jan 2014 PDFAna PanissetAinda não há avaliações

- Desenho Assistido Por or 3Documento32 páginasDesenho Assistido Por or 3Diana Nogueira100% (1)

- Prédios de São PauloDocumento143 páginasPrédios de São Paulobiblioteca mailfenceAinda não há avaliações

- Rca Relatório Volume IIIDocumento45 páginasRca Relatório Volume IIIRafaelaAgapitoAinda não há avaliações

- Pontes ExtradosadasDocumento13 páginasPontes ExtradosadasRamonn Henrique FrançaAinda não há avaliações

- Aula 1 - IntroduçãoDocumento28 páginasAula 1 - IntroduçãoVitor Folador GonçalvesAinda não há avaliações

- Porta Paletes 222381Documento44 páginasPorta Paletes 222381Rodrigo NishiAinda não há avaliações

- Aula 05 RevestimentosDocumento22 páginasAula 05 RevestimentosJosimar MacedoAinda não há avaliações

- Catálogo Farma Médico Hospitalar WEB Mar 2014Documento24 páginasCatálogo Farma Médico Hospitalar WEB Mar 2014thiagojapurAinda não há avaliações

- Configurando Di-624Documento8 páginasConfigurando Di-624lelioflavioAinda não há avaliações

- Comandos DOS-WilDocumento4 páginasComandos DOS-WilWilmar Albarrcin HernandezAinda não há avaliações

- Easybok-Easyhome-Projeto Exemplo-Eep-Especificac o Do Escopo Do Projeto-V5 03Documento3 páginasEasybok-Easyhome-Projeto Exemplo-Eep-Especificac o Do Escopo Do Projeto-V5 03Everton LimaAinda não há avaliações

- Ficha de Trabalho 1 NG5 DR2Documento10 páginasFicha de Trabalho 1 NG5 DR2sergiorocha13Ainda não há avaliações

- Book Estação Guanabara IIDocumento25 páginasBook Estação Guanabara IIRaquel SpíndolaAinda não há avaliações

- Lista de Preços Onda Aquários Atualizada Janeiro 2012Documento54 páginasLista de Preços Onda Aquários Atualizada Janeiro 2012barbaraweisseAinda não há avaliações

- Catalogo Materiais SotecnisolDocumento12 páginasCatalogo Materiais SotecnisolTiago ValenteAinda não há avaliações