Escolar Documentos

Profissional Documentos

Cultura Documentos

Mosfets III

Enviado por

Arthur Henrique CapuaniTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Mosfets III

Enviado por

Arthur Henrique CapuaniDireitos autorais:

Formatos disponíveis

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Um passo essencial no projecto de um circuito amplificador MOSFET, passa pelo estabelecimento de um ponto de operao DC apropriado, para o transstor. Este passo conhecido por projecto de polarizao (bias). Um ponto de operao DC apropriado caracterizado por uma corrente de dreno DC (iD) estvel e previsvel e por uma tenso dreno-source DC (VDS) que assegure a operao na regio de saturao, para todos os nveis de sinais de entrada esperados. Polarizao usando um valor de VGS fixo. A forma mais simples de polarizao de um MOSFET, consiste em fixar a tenso gate-source num valor que proporcione a corrente desejada ID. Este valor de tenso pode ser obtido a partir da tenso da fonte de tenso VDD, usando um divisor de tenso apropriado. Em alternativa, VGS pode ser uma adequada tenso de referncia existente no sistema. Independentemente do modo como VGS gerado, este tipo de polarizao no a melhor.

Departamento de Engenharia Electrotcnica e de Computadores

78

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo. Tal pode ser explicado atravs da expresso para ID:

ID =

W 1 n C ox (VGS Vt ) 2 L 2

Tenso de limiar aspect ratio do transstor

Capacidade do xido

Estes parmetros variam fortemente entre dispositivos do mesmo tamanho e tipo. Alm disso, Vt e n dependem da temperatura. Assim, se fixarmos o valor de VGS, a corrente de dreno ID, torna-se bastante dependente da temperatura. Para reforar o facto de que uma tenso fixa de polarizao VGS no constitui uma boa tcnica, a Fig. 32, mostra duas curvas caractersticas (iD vGS), representando valores extremos para MOSFETs do mesmo tipo.

Departamento de Engenharia Electrotcnica e de Computadores

79

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo.

Observa-se que para um valor fixo de VGS, a diferena na evoluo da corrente de dreno pode ser substancial.

Fig. 32

Departamento de Engenharia Electrotcnica e de Computadores

80

TRANSSTORES DE EFEITO DE CAMPO

Polarizao usando um valor de VGS fixo. Polarizao em circuitos amplificadores MOS Uma excelente tcnica de polarizao consiste na fixao da tenso da gate VG usando uma resistncia da source para a massa. Tal ilustrado na Fig. 33 sendo VG dado por

VG = VGS + RS I D

(44)

Se VG muito maior de que VGS, ID ser essencialmente determinada pelos valores de VG e RS. Mesmo que VG no seja muito maior de VGS, a resistncia RS proporciona realimentao negativa, a qual actua como estabilizador da corrente de polarizao ID. Para perceber o funcionamento, considere-se a situao em que ID aumenta por qualquer razo. A equao (44), indica que nestas circunstncias, como VG constante, VGS ter de decrescer. Tal resulta num decrscimo em ID, variao esta oposta ao inicialmente assumido. RS actua de forma a manter ID o mais constante possvel. A esta aco de realimentao negativa de RS d-se o nome de resistncia de degenerao.

Departamento de Engenharia Electrotcnica e de Computadores

Fig. 33 81

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo. O grfico da Fig. 34 ilustra este processo de polarizao, onde so mostradas duas caractersticas iD vGS, para dois dispositivos, que representam os extremos de uma dada produo de MOSFETs. O segmento de recta desenhado representa as restries impostas pelo circuito de polarizao (eq. 44) A interseco desta linha recta com a curva caracterstica iD vGS, proporciona as coordenadas do ponto de polarizao (ID e VGS).

Comparativamente ao caso de VGS de valor fixo, neste caso a variao obtida em ID muito menor. Note-se que a variao decresce medida que VG e RS so incrementados.

Fig. 34

Departamento de Engenharia Electrotcnica e de Computadores

82

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo. As Fig. 35 (c) e (e) ilustram duas implementaes prticas para este esquema de polarizao. O circuito da Fig. 35 (c) utiliza uma fonte de tenso VDD, obtendo-se VG atravs de um divisor de tenso (RG1 e RG2). Visto que IG = 0, RG1 e RG2, podem ser seleccionadas com elevada valor (na gama dos M), permitindo ao MOSFET apresentar uma resistncia de entrada elevada a uma fonte de sinal, que pode ser ligada gate atravs de um condensador de acoplamento.

Fig. 35

Departamento de Engenharia Electrotcnica e de Computadores

83

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo. A funo do condensador Cc1 bloquear uma eventual componente DC, permitindo acoplar o sinal vsig entrada do amplificador sem perturbao do ponto de polarizao DC do MOSFET. O valor de Cc1 deve ser seleccionado de modo a possuir um valor elevado tal que, para todas frequncias do sinal de interesse, este se comporte como um curto-circuito. A resistncia RD, deve ser seleccionada com o maior valor possvel para obter-se um ganho elevado, mas suficientemente pequena de modo a permitir que o sinal desejado varie sem distoro, mantendo o MOSFET permanentemente na saturao.

Fig. 36

Departamento de Engenharia Electrotcnica e de Computadores

84

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando um valor de VGS fixo. Quando existem duas fontes de tenso de disponveis, pode ser usado o esquema de polarizao mais simples ilustrado na Fig. 35 (e). Este circuito uma implementao da equao 44, com VG substitudo por VSS. A resistncia RG apresenta uma resistncia elevada a uma fonte de sinal que lhe seja eventualmente ligada. EXEMPLO 8 Admita que se pretende projectar o circuito da figura 35(c), afim de estabelecer uma corrente de dreno ID=0,5mA. O MOSFET especificado para ter Vt = 1 V e kn W/L = 1mA/V2. Por questes de simplicidade, despreze o efeito de modulao do comprimento do canal (i.e., assuma = 0). Use uma fonte VDD = 15 V. Determine a percentagem de variao verificada no valor de ID, quando o MOSFET substitudo por um outro com o mesmo kn W/L e Vt = 1.5V.

Departamento de Engenharia Electrotcnica e de Computadores

85

TRANSSTORES DE EFEITO DE CAMPO

Polarizao, fixando VG e ligando uma resistncia na source EXEMPLO 8 (cont.) Como regra, para o projecto deste circuito clssico, escolhe-se RD e RS de modo a proporcionarem 1/3 da tenso da fonte VDD atravs de RD, transstor (i.e., VDS) e RS. Para VDD = 15 V, esta escolha faz com que VD = +10 V e VS =+ 5V. Visto que requerido ID = 0,5 mA, pode-se obter os valores de RD e RS do seguinte modo: Polarizao em circuitos amplificadores MOS

RD =

VDD VD 15 10 = = 10k ID 0 .5

RS =

VS 5 = = 10k I D 0.5

O valor de VGS pode ser determinado, calculando previamente a tenso overdrive VOV usando,

1 ' 2 I D = k n (W / L) VOV 2

Assim,

1 2 0.5 = 1 VOV 2

VOV = 1 V

VGS = Vt + VOV = 1 + 1 = 2 V VG = VS + VGS = 5 + 2 = 7 V

86

Visto que VS = +5V, resulta para VG:

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Polarizao, fixando VG e ligando uma resistncia na source (cont)

Polarizao em circuitos amplificadores MOS

EXEMPLO 8 (cont.) Afim de estabelecer esta tenso na gate, pode-se seleccionar RG1 = 8 M e RG2 = 7 M. O circuito projectado mostrado na Fig. 37. Observe-se que a tenso DC no dreno (+10V) permite a excurso de um sinal positivo de +5V (i.e., at VDD) e de um sinal negativo de -4V (i.e. abaixo de (VG Vt)). Se o transstor NMOS substitudo por um outro tendo Vt = 1,5 V, o novo valor de ID pode ser determinado por,

1 I D = 1 ( VGS 1.5) 2 2

I D = 0.455 mA

Assim, a variao em ID :

VG = VGS + RS I D

7 = VGS + 10 I D

Fig. 37 i.e.

0.045 x100 = 9% 0.5

I D = 0.455 0.5 = 0.045 mA

(variao) 87

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando uma resistncia de realimentao Dreno-Gate Uma outra forma de polarizao de um circuito discreto utiliza uma resistncia de realimentao ligada entre o dreno e a gate mostrado na Fig. 38. A resistncia de realimentao de elevado valor RG (usualmente na gama dos M), fora a tenso DC na gate a um valor igual tenso no dreno (porque IG = 0) Assim, pode-se escrever Que pode ser rescrito como

VGS = VDS = VDD RD I D VDD = VGS + RD I D

(45)

A eq. (45) tem a mesma forma que a eq. (44). Se por qualquer razo ID aumentar, VGS tem de decrescer. O decrscimo em VGS, por sua vez, causa um decrscimo em ID, variao que oposta inicialmente assumida. Assim, a resistncia de realimentao, proporcionada por RG, funciona de modo a manter o valor de ID o mais constante possvel.

Departamento de Engenharia Electrotcnica e de Computadores

Fig. 38

88

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao, usando uma resistncia de realimentao Dreno-Gate O circuito da Fig. 38, pode ser utilizado como um amplificador source-comum, aplicando um de sinal de tenso na gate via um condensador de acoplamento, de modo a no perturbar as condies de polarizao j estabelecidas. O sinal de sada no dreno, pode ser acoplado a outra parte do circuito, via condensador. Polarizao usando uma fonte de corrente constante O circuito mais eficiente para polarizao de um amplificador MOSFET baseado na utilizao de uma fonte de corrente. A Fig. 39 ilustra essa configurao. A resistncia RG apresenta uma resistncia elevada a uma fonte de sinal que lhe seja eventualmente ligada. A resistncia RD, estabelece uma tenso DC apropriada no dreno, que permite a excurso desejada do sinal de sada e assegura que o transstor permanea sempre na regio de saturao. Fig. 39

Departamento de Engenharia Electrotcnica e de Computadores

89

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando uma fonte de corrente constante A Fig. 40 ilustra um circuito para implementao da fonte de corrente constante I. O elemento fundamental do circuito o transstor Q1, cujo dreno est curto-circuitado sua gate, operando assim na regio de saturao, tal que:

I D1 =

1 ' W k n (VGS Vt ) 2 2 L 1

(46)

onde foi desprezado a modulao do comprimento do canal (i.e. = 0). A corrente de dreno de Q1 fornecida por VDD, atravs de R. Visto que as correntes de gate so zero,

I D1 = I REF =

VDD + VSS VGS R

(47)

Onde a corrente atravs de R, a corrente de referncia da fonte de corrente, designada por IREF. Dados os parmetros de Q1 e o valor desejado para IREF, as equaes (46) e (47) podem ser usadas para determinar o valor R.

Departamento de Engenharia Electrotcnica e de Computadores

Fig. 40

90

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Polarizao usando uma fonte de corrente constante Considere-se o Transstor Q2: Q2 possui o mesmo VGS que Q1. Assumindo que este opera na regio de saturao, a sua corrente de dreno, que a corrente I da fonte de corrente, ser:

I = I D2 =

1 ' W k n (VGS Vt ) 2 2 L 2

(48)

onde foi desprezada a modulao do comprimento do canal (i.e. = 0). Equaes (47) e (48), permitem a obteno de uma relao entre a corrente I e a corrente IREF.

I = I REF

(W / L) 2 (W / L)1

(49)

Como se verifica, I relacionado com IREF pela relao dos aspect ratios de Q1 e Q2. Este circuito conhecido como espelho de corrente, sendo muito popular no projecto de amplificadores MOS.

Departamento de Engenharia Electrotcnica e de Computadores

91

TRANSSTORES DE EFEITO DE CAMPO

Polarizao em circuitos amplificadores MOS Exerccio 6 Considere o circuito da Fig. 35(c) usando uma tenso de alimentao de 15V. Para o MOSFET temos: Vt=1,2 V, =0, kn=80 mA/V2, W=240 mm and L= 6 mm. A corrente de dreno de 2 mA e um tero da tenso de alimentao aplicada a RS e RD, respectivamente. A maior das resistncia RG1 e RG2 vale 22 M. Quais os valores de RG1, RG2, RS, RD. Para os valores encontrados a que distncia de encontra VD da saturao?

Exerccio 7 Dimensione o circuito da Fig. 41 de forma a que o transistor funcione na saturao com VD a 1 V da regio de trodo, com ID=1 mA e VD=3 V, para os seguintes dispositivos (considerar 10 A no divisor de tenso): a) V t = 1V , k ' p W / L = 0 ,5 mA / V 2

' 2 b) Vt = 2 V , k p W / L = 1, 25 mA / V

Fig. 41

Departamento de Engenharia Electrotcnica e de Computadores

92

TRANSSTORES DE EFEITO DE CAMPO

O Ponto de funcionamento DC Modelos para pequenos sinais.

Como estudado anteriormente, a amplificao linear pode ser obtida polarizando o MOSFET de modo a que este funcione na regio de saturao. Considere-se, agora, a operao para pequenos sinais, com algum detalhe, usando para o efeito o circuito amplificador source comum, mostrado na Fig. 42. O transstor MOS polarizado aplicando uma tenso VGS. Claramente uma situao pouco prtica mas que simples e til. O sinal de entrada a amplificar (vgs), surge sobreposto tenso de polarizao VGS. A corrente de polarizao ID, pode ser determinada fixando o sinal vgs a zero. Assim, assumindo = 0

ID =

1 ' W k n (VGS Vt ) 2 2 L

(50)

A tenso no dreno, VDS ou simplesmente VD (S est ligado massa), :

VD = VDD RD I D

Departamento de Engenharia Electrotcnica e de Computadores

(51)

Fig. 42

93

TRANSSTORES DE EFEITO DE CAMPO

O Ponto de funcionamento DC Modelos para pequenos sinais.

Para assegurar que a operao se verifica na regio de saturao, tem de verificar-se,

VD > VGS Vt

Visto que a tenso total no dreno, ter a componente de sinal sobreposta a VD, esta tenso ter de ser suficientemente superior a (VGS Vt), afim de permitir que o sinal tenha a excurso desejada. A corrente de sinal no terminal de dreno. dreno Considere-se, agora, o sinal de entrada (vgs) aplicado. A tenso instantnea gate-source, ser:

vGS = VGS + v gs

Resulta uma corrente de dreno instantnea:

(52)

1 ' W kn 2 L 1 ' W iD = k n 2 L iD =

2 (VGS + v gs Vt ) 2 ' W (VGS Vt ) + k n L

1 ' W (VGS Vt )v gs + k n 2 L

2 v gs

(53) 94

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. A corrente de sinal no terminal de dreno (Cont.). .)

iD =

1 ' W kn 2 L

2 ' W (VGS Vt ) + k n L

1 ' W (VGS Vt )v gs + k n 2 L

2 v gs

O primeiro termo identifica a corrente DC de polarizao (ID). O segundo termo, representa a componente de corrente que directamente proporcional ao sinal de entrada (vgs). O terceiro termo, representa a componente de corrente que proporcional ao quadrado do sinal de entrada. Este ltimo termo indesejvel, pelo facto de representar distoro. Afim de reduzir a distoro, introduzida pelo MOSFET, o sinal de entrada deve ser mantido num baixo valor, tal que:

1 ' W 2 ' W k n v gs << k n (VGS Vt )v gs 2 L L

Isto ,

Tenso overdrive (55) 95

v gs << 2 (VGS Vt )

(54)

ou

v gs << 2 VOV

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. A corrente de sinal no terminal de dreno (Cont.). .) Se a condio anterior, para pequeno sinais, satisfeita pode-se desprezar o ltimo termo da eq. 53, e representar iD do seguinte modo:

iD I D + id

(56)

com

' W id = k n (VGS Vt )v gs L

O parmetro que relaciona id com vgs, designado por transcondutncia do MOSFET gm:

gm =

ou

id ' W = kn v gs L

(VGS Vt )

(57)

' W g m = k n VOV L

(58)

A Fig. 43 representa uma interpretao grfica, para a operao de pequenos sinais do amplificador MOSFET. Note-se que gm igual inclinao da caracterstica iD vGS do ponto de polarizao,

gm =

iD vGS

(59)

vGS =VGS

Fig. 43

Departamento de Engenharia Electrotcnica e de Computadores

96

TRANSSTORES DE EFEITO DE CAMPO

O ganho em tenso. tenso Modelos para pequenos sinais. Voltando ao circuito da Fig. 42, note-se que se pode exprimir a tenso de dreno instantnea total vD como se segue:

vD = VDD RD iD

Para a condio de pequenos sinais, vem:

que pode ser reescrita como:

Assim, a componente de sinal da tenso de dreno : (60) Pelo que o ganho de tenso dado por Av (61) 97

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

O ganho em tenso (cont) Modelos para pequenos sinais. O sinal menos na Eq. (61) indica que o sinal de sada vd est em oposio de fase com o sinal de entrada vgs.

Tal ilustrado na Fig. 44, que mostra vGS e vD. Admite-se que o sinal de entrada tem uma forma de onda triangular com uma amplitude muito menor do que 2(VGS Vt), que a condio de pequenos sinais da Eq. (54), para assegurar funcionamento linear. Para confinar o funcionamento regio de saturao para qualquer instante, o valor mnimo de vD no deve tornar-se inferior ao valor correspondente de vG por um valor superior a Vt. Alm disso, o valor mximo de vD deve ser menor do que VDD, de outro modo o FET entrar em corte e os picos da forma de onda do sinal de sada sero cortados. Fig. 44

Departamento de Engenharia Electrotcnica e de Computadores

98

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais.

Separao da anlise em DC da anlise de sinal

Da anlise anterior conclumos que dentro da aproximao de pequenos sinais, as variaes de sinal aparecem sobrepostas aos valores DC. Por exemplo, a corrente de dreno total iD igual corrente DC (ID) mais a corrente de sinal id; a tenso de dreno total vD = VD + vd, etc. Decorre daqui que a anlise e o projecto podem ser muito simplificados separando os clculos de DC dos clculos para pequenos sinais. Isto , uma vez estabelecido um ponto de funcionamento estvel e tendo calculado todos os valores DC podemos realizar a anlise de sinal ignorando esses valores DC.

Modelos equivalentes de circuito para pequenos sinais

Do ponto de vista de sinal, o FET comporta-se como uma fonte de corrente controlada por tenso, que tem como entrada um sinal vgs aplicado entre a porta e a source e como sada a corrente gmvgs no terminal do dreno. A resistncia de entrada desta fonte controlada muito elevada idealmente infinita. A resistncia de sada, i.e., a resistncia vista do dreno , tambm, elevada, tendo sido considerada infinita at agora.

Departamento de Engenharia Electrotcnica e de Computadores

99

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais.

Modelos equivalentes de circuito para pequenos sinais (Cont.)

Tendo em ateno o exposto, o funcionamento para pequenos sinais do FET pode ser representado pelo circuito mostrado na Fig. 45. Trata-se de um modelo ou circuito equivalente para pequenos sinais. Na anlise de um circuito amplificador com FETs, o FET pode ser substitudo pelo modelo equivalente mostrado na Fig. 45. O resto do circuito permanece inalterado excepto que as fontes de tenso contnua so substitudas por curto-circuitos. Isto resulta do facto de que a tenso aos terminais de uma fonte de tenso contnua ideal no varia, pelo que a tenso de sinal aos seus terminais ser sempre zero. O circuito resultante pode ento ser usado para realizar a anlise de sinal pretendida e, em particular, calcular o ganho de tenso. 100 Fig. 45

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais.

Modelos equivalentes de circuito para pequenos sinais (Cont.)

O maior inconveniente do modelo para pequenos sinais da Fig. 45 que ele pressupe que a corrente de dreno, em saturao, independente da tenso do dreno. O estudo das caractersticas do FET em saturao mostrou que, na verdade, a corrente cresce linearmente com a tenso vDS. Esta dependncia foi modelada por uma resistncia finita ro entre o dreno e a source, cujo valor foi dado pela equao,

ro =

VA ID

(62)

em que VA = 1/ um parmetro do MOSFET que, ou especificado, ou pode ser medido. VA proporcional ao comprimento do canal do MOSFET. A corrente ID, a corrente de dreno DC (no considerando a modulao do comprimento do canal):

ID =

1 ' W 2 k n VOV 2 L

(63) 101

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais.

Modelos equivalentes de circuito para pequenos sinais (Cont.)

Tipicamente, ro assume valores entre 10 e 1000 k. Assim, a preciso do modelo para pequenos sinais pode ser melhorada incluindo ro em paralelo com a fonte controlada, como se mostra na Fig. 46. importante notar que os parmetros do modelo para pequenos sinais gm e ro dependem do ponto de polarizao DC do MOSFET. Voltando ao amplificador da Fig. 42, vemos que substituindo o MOSFET pelo modelo para pequenos sinais da Fig. 46, obtemos a seguinte expresso do ganho de tenso

Av =

uma diminuio do valor do ganho de tenso.

(64)

Verifica-se, assim, que o efeito da resistncia de sada ro d origem a A anlise realizada para o transstor NMOS, os resultados e os modelos de circuito apresentados aplicam-se tambm a dispositivos PMOS, considerando para tal, |VGS|,|Vt|, |Vov|, |VA| e substituindo kn por kp

Departamento de Engenharia Electrotcnica e de Computadores

Fig. 46

102

TRANSSTORES DE EFEITO DE CAMPO

A transcondutncia gm

Modelos para pequenos sinais.

Analisemos um pouco mais em pormenor a transcondutncia do MOSFET, dada por,

gm =

id ' W ' W = k n (VGS Vt ) = k n VOV v gs L L

(65)

Esta relao indica que gm proporcional ao parmetro de transcondutncia do processo kn =nCox e ao factor W/L do transstor MOS. Assim, para obter uma transcondutncia relativamente grande, o dispositivo deve ser curto e largo. Tambm se verifica que, para um dado transstor, a transcondutncia proporcional tenso overdrive VOV= VGS - Vt, (quantidade para a qual a tenso de repouso VGS excede a tenso limiar Vt). Note-se, contudo, que aumentar gm custa de aumentar VGS tem o inconveniente de reduzir a excurso permitida da tenso de sinal do dreno. Uma outra expresso til para gm pode ser obtida substituindo (VGS - Vt) na Eq. (65) por,

' 2 I D /(k n (W / L))

(eq. (50))

' g m = 2k n W / L I D

(66) 103

Departamento de Engenharia Electrotcnica e de Computadores

TRANSSTORES DE EFEITO DE CAMPO

A transcondutncia gm

Esta expresso mostra que: 1. Para um dado MOSFET, gm proporcional raiz quadrada da corrente de polarizao DC; 2. Para uma dada corrente de polarizao, gm proporcional raiz quadrada de W/L. Modelos para pequenos sinais.

' g m = 2k n W / L I D

Para ter uma ideia da ordem de grandeza dos valores de gm dos MOSFETs, considere-se um transstor integrado funcionando com ID = 1 mA e tendo nCox = 120 A/V2. A Eq. (66) mostra que, para W/L = 1, gm=0,35 mA/V, enquanto que para um transstor para o qual W/L = 100 tem um gm = 3.5 mA/V. Uma outra expresso til para gm do MOSFET, pode ser obtida substituindo kn(W/L) na eq. (65) por 2ID/(VGS-Vt)2:

gm =

CONCLUSES:

2I D 2I = D VGS Vt VOV

(67)

Existem trs diferentes expresses para determinar gm. Existem trs parmetros de projecto: (W/L), VOV e ID. O projectista pode escolher que o MOSFET funcione com uma determinada tenso overdrive VOV e a uma corrente ID particular. A relao W/L pretendida, pode ento ser determinada e gm calculada.

Departamento de Engenharia Electrotcnica e de Computadores

104

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. EXEMPLO 9 A Fig. 47 mostra um amplificador com um transstor MOSFET, utilizando realimentao dreno-gate. O sinal de entrada vi acoplado gate atravs de um condensador de elevada capacidade e o sinal de sada do dreno acoplado resistncia de carga RL, tambm mediante um condensador de grande capacidade. Pretende-se analisar este amplificador de modo a determinar o seu ganho de tenso para pequenos sinais, a sua resistncia de entrada e o maior sinal de entrada admissvel. O transstor tem Vt = 1,5 V, kn(W/L) = 0,25 mA/V2 e VA = 50 V. Admita que a capacidade dos condensadores suficientemente grande para que possam ser considerados curto-circuitos s frequncias de interesse. Fig. 47

Departamento de Engenharia Electrotcnica e de Computadores

105

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. EXEMPLO 9 (cont) 1 - Calcula-se o ponto de funcionamento da seguinte forma:

1 I D = 0,25 (VGS 1,5) 2 2

(1)

onde, por simplicidade, ignormos o efeito da modulao do comprimento do canal. Uma vez que a corrente da gate zero, no h queda de tenso em RG ;assim, VGS = VD, que substituda em (1) conduz a

I D = 0,125 (VD 1,5) 2

Como

(2)

(3) Resolvendo o sistema formado pelas equaes (2) e (3), vem: ID = 1,06 mA e VD = 4,4 V

Departamento de Engenharia Electrotcnica e de Computadores

106

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. EXEMPLO 9 (cont) Conhecido o ponto de funcionamento, podemos agora calcular gm

' g m = kn

W (VGS Vt ) = 0,25 (4,4 1,5) = 0,725 mA / V L

A resistncia de sada dada por

Fig. 48 A Fig. 48 mostra o esquema equivalente para pequenos sinais do amplificador, onde os condensadores de acoplamento foram substitudos por curto-circuitos e a fonte DC foi substituda por um curto-circuito . Uma vez que RG muito grande (10 M), a corrente atravs desta pode ser desprezada comparada com a da fonte gmvgs, o que nos permite escrever para a tenso de sada,

Departamento de Engenharia Electrotcnica e de Computadores

107

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. EXEMPLO 9 (cont) Uma vez que vgs = vi, o ganho de tenso :

= 0,725 (10 // 10 // 47) = 3,3 V / V

Para calcular a resistncia de entrada Rin, note-se que a corrente de entrada ii dada por

Assim,

Departamento de Engenharia Electrotcnica e de Computadores

108

TRANSSTORES DE EFEITO DE CAMPO

Modelos para pequenos sinais. EXEMPLO 9 (cont) O maior sinal de entrada admissvel vi determinado pela necessidade de manter o MOSFET na saturao. Isto ,

vDS vGS Vt

No ponto limite, vGS mximo e vDS correspondentemente mnimo. Assim,

vDS min = vGS max Vt

VDS Av vi = VGS + vi Vt

4,4 3,3vi = 4,4 + vi 1,5

Resulta

vi = 0,35 V

Departamento de Engenharia Electrotcnica e de Computadores

109

TRANSSTORES DE EFEITO DE CAMPO

Modelo de circuito equivalente em T Modelos para pequenos sinais. Atravs de transformaes simples do circuito possvel desenvolver um modelo equivalente alternativo para o MOSFET. O desenvolvimento desse modelo, conhecido por modelo em T, est ilustrado na Fig. 49. A Fig. 49(a) mostra o circuito equivalente j apresentado anteriormente, sem ro. Na Fig. 49(b) foi acrescentada uma segunda fonte de corrente gmvgs em srie com a fonte de corrente original. Esta introduo obviamente no altera correntes terminais e, portanto, permitida. as

O novo n assim criado, designado por X, foi ligado ao terminal da gate G, na Fig. 49(c). Note-se que a corrente da gate no alterada, i.e., continua a ser zero e, portanto, tambm esta alterao no altera as caractersticas terminais. Note-se, agora, que temos uma fonte de corrente controlada gmvgs, ligada aos mesmos terminais da sua tenso de controlo vgs.

Departamento de Engenharia Electrotcnica e de Computadores

Fig. 49 110

TRANSSTORES DE EFEITO DE CAMPO

Modelo de circuito equivalente em T Modelos para pequenos sinais.

Podemos assim substituir esta fonte controlada por uma resistncia desde que esta resistncia conduza a mesma corrente da source (teorema da absoro da fonte). Teorema da absoro da fonte Admite-se que na anlise de um rede elctrica que temos uma fonte de corrente dependente Ix entre dois ns a e a, cuja diferena de potencial corresponde tenso de controlo da fonte, sendo Ix=gmVx (gm a condutncia). A fonte pode ser substituda por uma impedancia Zx=Vx/Ix=1/gm, como se mostra na figura, pois a corrente absorvida pela impedancia coincide com a corrente da fonte inicial que foi substituda.

Departamento de Engenharia Electrotcnica e de Computadores

111

TRANSSTORES DE EFEITO DE CAMPO

Modelo de circuito equivalente em T O valor dessa resistncia vgs / gmvgs = 1/ gm. Esta substituio est ilustrada na Fig. 49(d), resultando no modelo alternativo. Note-se que ig continua a ser zero, id = gmvgs e is = vgs / (1/ gm) = gmvgs, todas iguais s do modelo original da Fig. 49(a). O modelo da Fig. 49(d) mostra que a resistncia entre a gate e a source vista pela source, 1/ gm. Note-se que a resistncia entre a gate e a source vista pela gate, infinita. No desenvolvimento do modelo em T, no inclumos a resistncia ro. Se necessrio, isso pode ser feito incorporando essa resistncia entre o dreno e a source, no circuito da Fig. 49(d). Tal ilustrado na Fig. 50(a). Uma representao alternativa do modelo em T, no qual a fonte de corrente controlada por tenso substituda por uma fonte de corrente controlada por corrente, ilustrado na Fig. 50(b). Modelos para pequenos sinais.

Departamento de Engenharia Electrotcnica e de Computadores

112

TRANSSTORES DE EFEITO DE CAMPO

Modelo de circuito equivalente em T Modelos para pequenos sinais.

Finalmente, note-se que afim de distinguir o modelo da Fig. 46 do modelo equivalente T, o primeiro designado por modelo hbrido.

Fig. 50

Departamento de Engenharia Electrotcnica e de Computadores

113

Exerccio 8 Considere o circuito da Fig. 42 onde temos: Vt=2 V, =0, kn(W/L)=1 mA/V2, VGS=4V, VDD=10V e RD=3,6 k. a) Determine ID e VD. b) Determine o valor de gm para o ponto de funcionamento. c) Calcule o valor do ganho de tenso. d) Se o MOSFET tiver =0,01V-1, determine r0 no ponto de funcionamento e calcule o ganho em tenso.

Exerccio 9 Para o circuito da Fig. 51 substitua o transstor pelo seu equivalente T. Obtenha as expresses para os ganhos de tenso vs/vi e vd/vi.

Fig. 51

Departamento de Engenharia Electrotcnica e de Computadores

114

Você também pode gostar

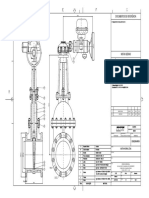

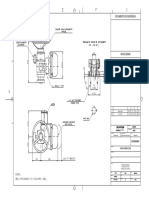

- CL09216 (Bypass)Documento1 páginaCL09216 (Bypass)Arthur Henrique CapuaniAinda não há avaliações

- CL09197 (Drenagem e Esgotamento)Documento1 páginaCL09197 (Drenagem e Esgotamento)Arthur Henrique CapuaniAinda não há avaliações

- Guia Elm PDFDocumento142 páginasGuia Elm PDFArthur Henrique CapuaniAinda não há avaliações

- Catalogo Geral CoesterDocumento8 páginasCatalogo Geral CoesterArthur Henrique CapuaniAinda não há avaliações

- CL09215 (Filtro)Documento1 páginaCL09215 (Filtro)Arthur Henrique CapuaniAinda não há avaliações

- CL09217 (Manual)Documento1 páginaCL09217 (Manual)Arthur Henrique CapuaniAinda não há avaliações

- CL09245 (Atuadores)Documento2 páginasCL09245 (Atuadores)Arthur Henrique CapuaniAinda não há avaliações

- Guia Elm PDFDocumento142 páginasGuia Elm PDFArthur Henrique CapuaniAinda não há avaliações

- Manual SMS Sinus Double IIDocumento51 páginasManual SMS Sinus Double IIwbendelak967477% (13)

- Guia Elm PDFDocumento142 páginasGuia Elm PDFArthur Henrique CapuaniAinda não há avaliações

- Cabo Eprotenax PDFDocumento4 páginasCabo Eprotenax PDFDeivison GonçalvesAinda não há avaliações

- DOMA046242Documento46 páginasDOMA046242Arthur Henrique CapuaniAinda não há avaliações

- Calculo Circuitos EletricosDocumento1 páginaCalculo Circuitos EletricossandrobonafinAinda não há avaliações

- Módulo 1Documento4 páginasMódulo 1Arthur Henrique CapuaniAinda não há avaliações

- Guia Do EletricistaDocumento192 páginasGuia Do EletricistasandrosrpAinda não há avaliações

- Cabo Eprotenax PDFDocumento4 páginasCabo Eprotenax PDFDeivison GonçalvesAinda não há avaliações

- Levantamento de Carga - Rev2Documento24 páginasLevantamento de Carga - Rev2Arthur Henrique CapuaniAinda não há avaliações

- LM - IlsDocumento6 páginasLM - IlsArthur Henrique CapuaniAinda não há avaliações

- Os Aterramentos Dos PainéisDocumento1 páginaOs Aterramentos Dos PainéisArthur Henrique CapuaniAinda não há avaliações

- GuiaDocumento2 páginasGuiaArthur Henrique CapuaniAinda não há avaliações

- Manual OPzS - Edição Setembro 2016Documento48 páginasManual OPzS - Edição Setembro 2016Arthur Henrique CapuaniAinda não há avaliações

- Guia Do EletricistaDocumento192 páginasGuia Do EletricistasandrosrpAinda não há avaliações

- Guia Do EletricistaDocumento192 páginasGuia Do EletricistasandrosrpAinda não há avaliações

- Ritual Matinal Extraordina Rio 2017-03-06Documento24 páginasRitual Matinal Extraordina Rio 2017-03-06Arthur Henrique CapuaniAinda não há avaliações

- Catalogo de Motores SiemensDocumento20 páginasCatalogo de Motores SiemensJuliano Reis Pereira0% (1)

- Custos de Veiculação Na MídiaDocumento1 páginaCustos de Veiculação Na MídiaArthur Henrique CapuaniAinda não há avaliações

- Hard InstitucionalDocumento24 páginasHard InstitucionalArthur Henrique CapuaniAinda não há avaliações

- FwefwrefwDocumento1 páginaFwefwrefwArthur Henrique CapuaniAinda não há avaliações

- Custos de Equipamentos de TIDocumento1 páginaCustos de Equipamentos de TIArthur Henrique CapuaniAinda não há avaliações

- WEG Transformadores A Oleo Instalacao e Manutencao 751 Manual Portugues BRDocumento28 páginasWEG Transformadores A Oleo Instalacao e Manutencao 751 Manual Portugues BRGilson Guimaraes de PaulaAinda não há avaliações

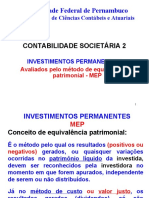

- Aula 2 Investimentos Permanentes MepDocumento56 páginasAula 2 Investimentos Permanentes MepADRIANO TRINDADEAinda não há avaliações

- STJ - Consulta ProcessualDocumento5 páginasSTJ - Consulta ProcessualMarília DominguesAinda não há avaliações

- Sony. DAV-DZ77T - ManualDocumento122 páginasSony. DAV-DZ77T - ManualMauryas De Castro ManzoliAinda não há avaliações

- New Datasheet Advanced Business Security - PTDocumento3 páginasNew Datasheet Advanced Business Security - PTvilaounipAinda não há avaliações

- Sistema de Administração de Benefício Por IncapacidadeDocumento1 páginaSistema de Administração de Benefício Por IncapacidadeRosely CastroAinda não há avaliações

- Av1 - PortuguesDocumento10 páginasAv1 - PortuguesThaina SilvaAinda não há avaliações

- ResumoDocumento12 páginasResumoEUCILENE NUNES DA SILVAAinda não há avaliações

- Prova de 100Documento7 páginasProva de 100carlao1234555555555Ainda não há avaliações

- ECG - ResumoDocumento14 páginasECG - ResumoNuno NogueiraAinda não há avaliações

- Unidades Da Grandeza ComprimentoDocumento2 páginasUnidades Da Grandeza ComprimentoJose Graciano100% (1)

- ContrachequeDocumento1 páginaContrachequeMony KellyAinda não há avaliações

- Redação: Estrutura Dissertativa No ENEMDocumento19 páginasRedação: Estrutura Dissertativa No ENEMADRONOO GUSTAVUAinda não há avaliações

- Fispq Acido SulfuricoDocumento14 páginasFispq Acido SulfuricoMarllon Boamorte LobatoAinda não há avaliações

- Apostila Ligações Químicas - (Comentada)Documento8 páginasApostila Ligações Químicas - (Comentada)Maurício Monteiro JúniorAinda não há avaliações

- Circular CL 21 - Novos Relés Eletrônicos Temporizadores RTW17Documento4 páginasCircular CL 21 - Novos Relés Eletrônicos Temporizadores RTW17Mateus Manoel CarvalhoAinda não há avaliações

- Relatorio Coluna WinogradskyDocumento6 páginasRelatorio Coluna WinogradskyBeatrizMattiuzzo100% (1)

- A Semiótica de PeirceDocumento4 páginasA Semiótica de PeirceJuscelino Alves de OliveiraAinda não há avaliações

- Lista 3 Estatistica Descritiva TabelasDocumento15 páginasLista 3 Estatistica Descritiva TabelasThamily Luiza UzanAinda não há avaliações

- Lista Exercicios ExcelDocumento6 páginasLista Exercicios ExcelCarlos Júnior UchôaAinda não há avaliações

- 20 Maneiras de Fazer 10.000mt Mensais. OriDocumento53 páginas20 Maneiras de Fazer 10.000mt Mensais. OriSchélzia Fátima Lampreia ManjateAinda não há avaliações

- Calculadora de Sobrevivência No MercadoDocumento3 páginasCalculadora de Sobrevivência No Mercadoyan allenAinda não há avaliações

- Avaliação de Geografiaa9º - 124217Documento2 páginasAvaliação de Geografiaa9º - 124217KarineAinda não há avaliações

- WEG Control Ad or Automatico Pfw01 Manual Portugues BRDocumento40 páginasWEG Control Ad or Automatico Pfw01 Manual Portugues BRlindomarlagunaAinda não há avaliações

- 2021 Ativ 01 05 de NovembroDocumento4 páginas2021 Ativ 01 05 de NovembroNatália SilvaAinda não há avaliações

- Sum Rio CTU22Documento12 páginasSum Rio CTU22Eduardo MullerAinda não há avaliações

- Aula 4 QueimadurasDocumento36 páginasAula 4 QueimadurasRosangela Rosas Santos100% (2)

- Atividade 2 Educação em Lugares Fora Da Ecola 3Documento2 páginasAtividade 2 Educação em Lugares Fora Da Ecola 3Luciano José DA Cruz33% (3)

- Exercícios Polígonos e Classificação Dos TriângulosDocumento4 páginasExercícios Polígonos e Classificação Dos TriângulosMiriam Silva Oliveira83% (29)

- Livro Osca Digosdomilha oDocumento161 páginasLivro Osca Digosdomilha oHemis Vivi LeiteAinda não há avaliações

- Aula 10 - Fundamento de Lógica Booleana PDFDocumento20 páginasAula 10 - Fundamento de Lógica Booleana PDFEduardo CaioAinda não há avaliações