Escolar Documentos

Profissional Documentos

Cultura Documentos

Resumo A9

Enviado por

Letícia AlvesDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Resumo A9

Enviado por

Letícia AlvesDireitos autorais:

Formatos disponíveis

Tecnologias de Lógica Combinacional

Portas Padrão

-Pacotes de portas

-Bibliotecas de células

Lógica Regular

-Multiplexadores

-Decodificadores

Lógica Programável em 2 níveis

-PALs

-PLAs

-ROMs

---

Lógica Aleatória

-Transistores foram integrados às portas lógicas

-Quais portas usar?

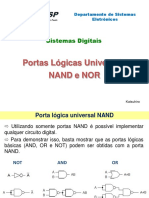

-Mapear da lógica para redes NAND/NOR

-Determinar nro. mínimo de pacotes (pequenas alterações na função podem

diminuir o custo)

-Alterações difíceis de realizar: religar peças, novas peças, design com peças de

reposição (poucos inversores e portões extras em cada placa)

---

Lógica Regular

-Tornar o design + rápido, facilitar alterações, + fácil entender e mapear

funcionalidades (+ difícil pensar em portas específicas, melhor em termos de bloco multiuso)

---

Conexões

-Ponto a ponto diretas entre portas

-Multiplexador (Mux): Encaminhar uma das muitas entradas para uma única saída

-Demultiplexador (Demux): Única entrada para uma das muitas saídas

---

Multiplexadores

-Seletores: conceito geral

-2 entradas de dados, n entradas de controle (chamadas "seleciona"), 1 saída

n

-Para conectar 2 pontos a um único ponto

n

-Padrão de sinal de controle forma o índice binário da entrada conectada à saída

Multiplexadores como lógica de uso geral

-Um Mux 2 : 1 pode implementar qualquer função de n variáveis

n

-Com as variáveis usadas como entradas de controle e as entradas de dados

vinculadas a 0 ou 1 (em essência, uma tabela de pesquisa)

-Um Mux 2 : 1 pode implementar qualquer função de n variáveis

n-1

-Com n-1 variáveis usadas como entradas de controle e as entradas de dados

vinculadas à última variável ou seu complemento

---

Demultiplexadores/Decodificadores

-Conceito geral: entrada única de dados, n entradas de controle, 2 saídas

n

-Entradas de controle (chamadas “seleciona” (S)) representam o índice binário de saída ao qual

a entrada está conectada

-Entrada de dados geralmente chamada de “habilitação” (G)

Demultiplexadores como lógica de uso geral

-Um decodificador n:2 pode implementar qualquer função de n variáveis com as

n

variáveis usadas como entradas de controle

-As entradas de habilitação vinculadas a 1

-Mintermos apropriados somados para formar a função

*n é o número de sinais de controle

---

Arrays de lógica programável

-Bloco de construção pré-fabricado de muitas portas AND / OR (na vdd NOR ou

NAND)

-"Personalizados" fazendo / interrompendo conexões entre as portas

-Diagrama de blocos de array programável para a forma soma de produtos

---

PALs e PLAs

Matriz lógica programável (PLA)

-O que vimos até agora

-Arrays AND e OR totalmente gerais sem restrições

Lógica de matriz programável (PAL)

-Topologia restrita da array OR

-Inovação por Memórias Monolíticas

-Plano OR mais rápido e menor

ROM vs. PLA

-Abordagem de ROM vantajosa quando:

-Tempo de design é curto (não é necessário minimizar as funções de saída)

-É necessária a maioria das combinações de entrada (por exemplo, conversores de

código)

-Poucos termos de produto comuns entre as funções de saída

-Problemas de ROM

-O tamanho dobra para cada entrada adicional

-Não é possível explorar os don’t cares

-Abordagem do PLA é vantajosa quando:

-As ferramentas de design estão disponíveis para minimização de múltiplas saídas

-Existem relativamente poucas combinações de mintermos únicas

-Muitos mintermos são compartilhados entre as funções de saída

-Problemas PAL:

-Fan-ins restritos no plano OR

Estruturas lógicas regulares para lógica de dois níveis

-ROM: plano AND completo, plano OR geral

-Barato (componente de alto volume)

-Pode implementar qualquer função de n entradas

-Velocidade média

-PAL: plano AND programável e plano, plano OR fixo

-Custo intermediário

-Pode implementar funções limitadas pelo número de termos

-Alta velocidade (apenas um plano programável que é muito menor que o

decodificador da ROM)

-PLA: planos AND e OR programáveis

-Mais caros (mais complexos em design, precisam de ferramentas mais sofisticadas)

-Podem implementar qualquer função até um limite de prazo do produto

-Lento (dois planos programáveis)

Estruturas lógicas regulares para lógica multinível

-Difícil conceber uma estrutura regular para conexões arbitrárias entre um grande conjunto de

tipos diferentes de portas

-Preocupações de eficiência / velocidade para essa estrutura

-Usa vários níveis de PALs / PLAs / ROMs

-Resultado intermediário de saída

-Entrada a ser usada em lógica adicional

Resumo da tecnologia de lógica combinacinal

-Lógica aleatória

-Portas simples ou em grupos

-Conversão para redes NAND-NAND e NOR-NOR

-Transição de portas simples para blocos de construção de porta mais complexos

-Contagem reduzida de portas, ventiladores, potencialmente mais rápidos

-Mais níveis, mais difíceis de projetar

-Tempo de resposta em redes combinacionais

-Atrasos de porta e tempo de formas de onda

-Hazards/glitches (o que são e por que acontecem)

-Lógica regular

-Multiplexadores / decodificadores

-ROMs

-PLAs / PALs

-Vantagens / desvantagens de cada

Você também pode gostar

- 4 - DEC - 7511 3.0 Caracteristicas Dos Sistemas EmbarcadosDocumento15 páginas4 - DEC - 7511 3.0 Caracteristicas Dos Sistemas EmbarcadosSamady CorrêaAinda não há avaliações

- Microcontroladores - Arquitetura PDFDocumento24 páginasMicrocontroladores - Arquitetura PDFRubens Zenko SakiyamaAinda não há avaliações

- CLP Apostila SLC500 v2Documento116 páginasCLP Apostila SLC500 v2Darlan Leite100% (2)

- Capítulo 4 SlidesDocumento65 páginasCapítulo 4 SlidesDiego Villegas VillacrecesAinda não há avaliações

- Apostila - Profibus DPDocumento18 páginasApostila - Profibus DPPaulo AbreuAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Ph Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Ph Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Catalogo NextoDocumento6 páginasCatalogo Nextotecmedrado@yahoo.com.brAinda não há avaliações

- Velloso - Redes Locais - Segmentaçào e GerênciaDocumento7 páginasVelloso - Redes Locais - Segmentaçào e GerênciaHauwaruAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Co Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Co Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Co2 Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Co2 Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- 02 Mapeamento ES emSDsDocumento6 páginas02 Mapeamento ES emSDsVítor André BeckenkampAinda não há avaliações

- Apostila Logica Programavel Aula 1Documento18 páginasApostila Logica Programavel Aula 1Jorge Henrique Marques MarianoAinda não há avaliações

- Curso de Redes Cisco CnaaDocumento332 páginasCurso de Redes Cisco CnaaJonathan Jonathancm10Ainda não há avaliações

- Teste FormativoDocumento10 páginasTeste Formativovaldimiro.gaspar16Ainda não há avaliações

- Desenvolvendo Uma Interface Ihm Modbus Rs-485 No ArduinoNo EverandDesenvolvendo Uma Interface Ihm Modbus Rs-485 No ArduinoAinda não há avaliações

- Apostila de RoteamentoDocumento16 páginasApostila de RoteamentoKarla NascimentoAinda não há avaliações

- Automação e Robótica PDFDocumento64 páginasAutomação e Robótica PDFjoseto_441Ainda não há avaliações

- Microcontrolador 8051Documento39 páginasMicrocontrolador 8051digitaleletronicaAinda não há avaliações

- Lista - SC II - 4 - BimestreDocumento5 páginasLista - SC II - 4 - BimestreApFernandezAinda não há avaliações

- Treinamento SiemensDocumento283 páginasTreinamento SiemensEric LimaAinda não há avaliações

- PEA5016-Mais ProtocolosDocumento68 páginasPEA5016-Mais ProtocolosLuis ChirinosAinda não há avaliações

- Desenvolvendo Um Gaussímetro Modbus Rs485 No ArduinoNo EverandDesenvolvendo Um Gaussímetro Modbus Rs485 No ArduinoAinda não há avaliações

- Classificação Dos Sistemas InformáticosDocumento37 páginasClassificação Dos Sistemas Informáticosapi-369612450% (8)

- Comunicação Rs-485 Modbus Para Medir Dinamômetro Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Dinamômetro Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Aula 1 - Dispositivos Logicos Programaveis PLDsDocumento34 páginasAula 1 - Dispositivos Logicos Programaveis PLDsVerônica SantosAinda não há avaliações

- Aulas Organizacao de Computadores Versao 2016 - 5 e 6Documento79 páginasAulas Organizacao de Computadores Versao 2016 - 5 e 6Andre DiasAinda não há avaliações

- Aula - 03 - Elementos de Interconexão de RedeDocumento13 páginasAula - 03 - Elementos de Interconexão de RedeDetobassAinda não há avaliações

- Tipos de Redes IndustriaisDocumento26 páginasTipos de Redes IndustriaisKleber SantosAinda não há avaliações

- Pesquisa de RedesDocumento21 páginasPesquisa de RedesthaylonrramonAinda não há avaliações

- Desenvolvendo Um Sensor De Pressão Modbus Rs485 No ArduinoNo EverandDesenvolvendo Um Sensor De Pressão Modbus Rs485 No ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Voltímetro Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Voltímetro Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Desenvolvendo Um Luxímetro Modbus Rs485 No ArduinoNo EverandDesenvolvendo Um Luxímetro Modbus Rs485 No ArduinoAinda não há avaliações

- Comunicação Paralela e SerialDocumento26 páginasComunicação Paralela e SerialRafael BorgesAinda não há avaliações

- ALTUS - Folheto de CLPsDocumento6 páginasALTUS - Folheto de CLPsJoão Paulo Ferreira TabeliãoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Termômetro Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Termômetro Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Gaussímetro Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Gaussímetro Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Aula1 - Conceitos Básicos, Histórico, Arquitetura de Microprocessadores, Microcontrolador 8051, Programação.Documento45 páginasAula1 - Conceitos Básicos, Histórico, Arquitetura de Microprocessadores, Microcontrolador 8051, Programação.RoanaD'ÁvilaAinda não há avaliações

- Microcontroladores e MicroprocessadoresDocumento9 páginasMicrocontroladores e MicroprocessadoresRenato Monteiro BatistaAinda não há avaliações

- Desenvolvendo Um Frequencímetro Modbus Rs485 No ArduinoNo EverandDesenvolvendo Um Frequencímetro Modbus Rs485 No ArduinoAinda não há avaliações

- Aula 1 MicroprocessadoresDocumento18 páginasAula 1 Microprocessadores194digaoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Gaussímetro Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Gaussímetro Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Fluxo De Massa Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Fluxo De Massa Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Glp Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Glp Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Dinamômetro Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Dinamômetro Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Microprocess AdoresDocumento59 páginasMicroprocess AdoresRicardo GomesAinda não há avaliações

- Desenvolvendo Um Medidor Co2 Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Co2 Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Voltímetro Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Voltímetro Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Higrômetro Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Higrômetro Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Célula De Carga Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Célula De Carga Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Etanol Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Etanol Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Desenvolvendo Um Medidor Barômetro Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Barômetro Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Folheto Tecnico S7-200Documento36 páginasFolheto Tecnico S7-200Cassio LemesAinda não há avaliações

- Sistemas de Geraao de Energia Eletrica Sistemas de Distribuiao de Energia Eletrica Supervisao e Controle de Energia Eletrica Aquisiao de Dados eDocumento38 páginasSistemas de Geraao de Energia Eletrica Sistemas de Distribuiao de Energia Eletrica Supervisao e Controle de Energia Eletrica Aquisiao de Dados eFrancisco BlancoAinda não há avaliações

- Desenvolvendo Um Medidor Fluxo De Massa Modbus Rs232 No Stm32f103 Programado No ArduinoNo EverandDesenvolvendo Um Medidor Fluxo De Massa Modbus Rs232 No Stm32f103 Programado No ArduinoAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Decibelímetro Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Decibelímetro Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Lógica ProgramávelDocumento10 páginasLógica ProgramávelJoão MoraisAinda não há avaliações

- Desenhos de Placas MãesDocumento22 páginasDesenhos de Placas MãesDAVID ALEXANDRE ROSA CRUZAinda não há avaliações

- Comunicação Rs-485 Modbus Para Medir Glp Com Esp8266 (nodemcu) Programado Em ArduinoNo EverandComunicação Rs-485 Modbus Para Medir Glp Com Esp8266 (nodemcu) Programado Em ArduinoAinda não há avaliações

- Resumo A9pt2Documento1 páginaResumo A9pt2Letícia AlvesAinda não há avaliações

- ResumoDocumento19 páginasResumoLetícia AlvesAinda não há avaliações

- Resumo Alocação DinâmicaDocumento3 páginasResumo Alocação DinâmicaLetícia AlvesAinda não há avaliações

- Resumo RecursividadeDocumento1 páginaResumo RecursividadeLetícia AlvesAinda não há avaliações

- DjangoDocumento25 páginasDjangoLetícia AlvesAinda não há avaliações

- Resumo P1Documento17 páginasResumo P1Letícia AlvesAinda não há avaliações

- Resum Oaul AsDocumento1 páginaResum Oaul AsLetícia AlvesAinda não há avaliações

- Resumo P1Documento10 páginasResumo P1Letícia AlvesAinda não há avaliações

- Resum Oaul AsDocumento1 páginaResum Oaul AsLetícia AlvesAinda não há avaliações

- Resum Oaul AsDocumento1 páginaResum Oaul AsLetícia AlvesAinda não há avaliações

- Resumo Aula 2Documento1 páginaResumo Aula 2Letícia AlvesAinda não há avaliações

- Ta BomDocumento1 páginaTa BomLetícia AlvesAinda não há avaliações

- ResumoP1 RedesDocumento11 páginasResumoP1 RedesLetícia AlvesAinda não há avaliações

- Ta BomDocumento1 páginaTa BomLetícia AlvesAinda não há avaliações

- Este É Um Documento TesteDocumento1 páginaEste É Um Documento TesteLetícia AlvesAinda não há avaliações

- CMOS Organizados Por FunçãoDocumento1 páginaCMOS Organizados Por FunçãoEletecAinda não há avaliações

- 05-Circuito Integrado-Portas LógicasDocumento35 páginas05-Circuito Integrado-Portas LógicasAirton MaestrelloAinda não há avaliações

- M 1112a 1100 Aluno PorDocumento21 páginasM 1112a 1100 Aluno PorDi OliveiraAinda não há avaliações

- Manual ProteusDocumento34 páginasManual ProteusHugo Magalhães MartinsAinda não há avaliações

- Algebra BooleanaDocumento3 páginasAlgebra BooleanaSamuel RibeiroAinda não há avaliações

- Teoremas Booleanos, Álgebra Booleana e Circuitos LógicosDocumento7 páginasTeoremas Booleanos, Álgebra Booleana e Circuitos Lógicosmarcio2silvaAinda não há avaliações

- 5 - Laboratório de Sistemas DigitaisDocumento62 páginas5 - Laboratório de Sistemas DigitaisGabriel Vasconcelos NogueiraAinda não há avaliações

- 83 - Lógica - de - Programação 2Documento82 páginas83 - Lógica - de - Programação 2Rodrigo S. de QuadrosAinda não há avaliações

- Lógica DigitalDocumento58 páginasLógica DigitalEdson MendesAinda não há avaliações

- Cap2 Digital IDocumento56 páginasCap2 Digital ICesar JrAinda não há avaliações

- Portas Lógicas Universais Nand E Nor: Sistemas DigitaisDocumento11 páginasPortas Lógicas Universais Nand E Nor: Sistemas DigitaisLucasAinda não há avaliações

- Funções Ci 7404 7408 7432 7400Documento21 páginasFunções Ci 7404 7408 7432 7400Franklin MirandaAinda não há avaliações

- Simulado RESOLVIDODocumento28 páginasSimulado RESOLVIDOSilvi PernaAinda não há avaliações

- Atividade 02Documento7 páginasAtividade 02Ana Carolina Barroso100% (1)

- Circuitos - Combinacionais Somadores e Codificadores PDFDocumento67 páginasCircuitos - Combinacionais Somadores e Codificadores PDFFabio Splendor100% (1)

- Eletrônica DigitalDocumento23 páginasEletrônica DigitalYuri X Kenny0% (1)

- Apostila Álgebra Booleana Exercicios ResolvidosDocumento16 páginasApostila Álgebra Booleana Exercicios ResolvidosandrelenilzeAinda não há avaliações

- Lab002 002Documento41 páginasLab002 002Fabio CostaAinda não há avaliações

- Exercicio02 - GabaritoDocumento5 páginasExercicio02 - GabaritoBruno Cardoso HolandaAinda não há avaliações

- Portas LogicasDocumento15 páginasPortas LogicasAnderson VertuanAinda não há avaliações

- Aula 1 - Portas LógicasDocumento14 páginasAula 1 - Portas LógicasGabriel GuilhermeAinda não há avaliações

- Aula 3 - Eletronica Sub - Circuitos LógicosDocumento36 páginasAula 3 - Eletronica Sub - Circuitos Lógicosdecioadmi6105Ainda não há avaliações

- Exp Lab Sistemas DigitaisDocumento33 páginasExp Lab Sistemas DigitaisautojhAinda não há avaliações

- 03 Circuitos LógicosDocumento31 páginas03 Circuitos LógicosJoelsonAinda não há avaliações

- Apostila de Sistemas Logicos e DigitaisDocumento70 páginasApostila de Sistemas Logicos e DigitaisYann Braga100% (1)

- Lógica Booleana e Circuitos LógicosDocumento3 páginasLógica Booleana e Circuitos Lógicosrogersantosferreira100% (1)

- NorDocumento5 páginasNorDaniel S BachAinda não há avaliações

- Aula2 - Funções e Portas LógicasDocumento17 páginasAula2 - Funções e Portas LógicasclerisAinda não há avaliações

- Circuitos Digitais-Aula03Documento41 páginasCircuitos Digitais-Aula03christian souza100% (1)