Escolar Documentos

Profissional Documentos

Cultura Documentos

02.1 Sistemas de Memoria

Enviado por

Il Ton PrandiDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

02.1 Sistemas de Memoria

Enviado por

Il Ton PrandiDireitos autorais:

Formatos disponíveis

Organizao e Arquitetura de

computadores

Prof. Wilfredo Blanco Figuerola

Curso Superior de:

Tecnologia em Analise e

Desenvolvimento de Sistemas

Redes

ORGANIZAO E ARQUITETURA DE COMPUTADORES 2

Ementa

1. Introduo Organizao de

Computadores

Arquitetura e organizao de computadores:

viso geral

Componentes do sistema de computador

Evoluo dos Computadores

2. Sistema de Memria

Representao numrica

Caractersticas e tipos

Estrutura e organizao

Hierarquia de memria

Memria principal

Memria virtual

Memria cache

Memria secundria

3. Unidade Central de Processamento

Processadores

Construo de uma via de dados

Abordagem monociclo

Abordagem multi-ciclo

Pipeline

Evoluo dos Processadores

Processadores CISC e RISC

Mquinas escalares

Mquinas superescalares

Mquinas VLIW

Tendncias

4. Sistema de Entrada e Sada

Sistema de Interconexo: Barramentos

Estruturas de interconexo

Interconexo de barramentos

Mdulos de E/S

Tcnicas de Controle para Transferncia de

Dados

E/S Programada

E/S Dirigida por Interrupo

Acesso Direto Memria (DMA)

5. Introduo Arquitetura de Computadores

A viso do Software

O compilador

O montador

O ligador

O carregador

O processo de boot

6. Linguagem de Montagem

Operaes e operandos

Instrues Lgicas e Aritmticas

Instrues de desvio

7. Linguagem de Mquina

Codificao das Instrues

Linguagem de descrio de Arquitetura

Anatomia de um arquivo executvel

ORGANIZAO E ARQUITETURA DE COMPUTADORES 3

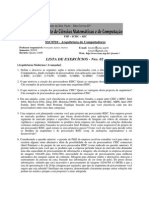

Sistema de Memria

Introduo

Dispositivos

de entrada

Dispositivos

de sada

Memoria primaria

(RAM)

Programas so

armazenados aqui

Processador

Controlador de

memoria

Memoria secundaria

(discos rgidos, CDs, etc)

Memria Principal

Memria Cache

Interna (L1)

Memria Secundria

HD, FD, ZIP, CD, DVD

Registradores

C

u

s

t

o

p

o

r

b

i

t

Memria Interna

Capacidade de Armazenamento

Armazenamento

de Segurana

Fita Magntica, MO, WORM

Armazenamento

Externo

Externa (L2)

V

e

l

o

c

i

d

a

d

e

d

e

a

c

e

s

s

o

ORGANIZAO E ARQUITETURA DE COMPUTADORES 4

Sistema de Memria

Memria interna: Registradores

O objetivo de toda memria ou subsistema de memria

e armazenar informao, que em algum momento,

seja utilizada pelo processador.

Antes de uma memria sela utilizada, o processador

necessita busc-la (memria cache ou principal) e

armazen-la no seu prprio interior, nos registradores.

ORGANIZAO E ARQUITETURA DE COMPUTADORES 5

Sistema de Memria

Memria interna: Registradores

Registrador

Elemento superior da pirmide de memria

Maior velocidade de transferncia

Menor capacidade de armazenamento

Maior custo

Tempo de acesso: um ciclo de memria (em torno de

1 ou 2 nanos-segundos)

Capacidade: armazenam um nico dado, dependendo

do tipo de processador.

Volatilidade: so memrias volteis, necessitam de

energia para funcionarem.

Tecnologia: bipolar e MOS (metal oxide semicondutor)

Temporalidade: guardam informao o mais

temporariamente possvel (tempo necessrio para ser

utilizada na UAL).

Custo: elevado

ORGANIZAO E ARQUITETURA DE COMPUTADORES 6

Sistema de Memria

Memria cache

www.yourdictionary.com/computer/cache

Sistemas de computao antigos no possua memria cache.

Em toda execuo de uma instruo, o processador acessa a

memria principal

Dependendo do tipo de instruo, levava mais de um ciclo de

memria.

Esta interface entre o processador e a memria vem sendo um ponto

frgil para o performance (gargalo)

(1) Motivo para o

surgimento do projeto

de uso de memoria

cache

ORGANIZAO E ARQUITETURA DE COMPUTADORES 7

Sistema de Memria

Memria cache

Memria cache: dispositivo de memria,

fabricado com tecnologia semelhante do

processador, localizado entre o processador e a

memria principal.

Tempo de acesso: 5 a 20 ns

Capacidade: L1 oscilam entre 32 e 256KB e at

4MB para L2.

Volatilidade: so dispositivos volteis.

Tecnologia: circuitos eletrnicos de alta

velocidade, constitudas de um

capacitor/transistor, requerem de recarregamento.

Temporariedade: baixo

Custo: alto

ORGANIZAO E ARQUITETURA DE COMPUTADORES 8

Sistema de Memria

Memria cache

(1) Diferena de velocidade processador->memria principal

Operao

Soma: 2ns

Memria

principal

Transferncia: 100ns

Processador

Ciclo de tempo do processador muito menor

que o ciclo tempo da memria principal

Estado de espera (wait state) maior

Tecnologia vs Custo

Se agrava com o uso concorrente de vrios

programas (multi-programao)

Em 1960 IBM analisaram o comportamento dos

processos (programas)

ORGANIZAO E ARQUITETURA DE COMPUTADORES 9

Sistema de Memria

Memria cache

(2) Principio da localidade

____________

Call sub_rotina 1

____________

____________

____________

____________

____________

____________

____________

____________

____________

____________

____________

____________

____________

MP

Execuo em

seqncia

Loop 1

Loop 2

sub_rotina 1

Localidade espacial:

Localidade temporal:

Os programas so executados em

pequenos blocos de instrues,

executados seqencialmente

Os programas tenderem a usar

freqentemente o mesmo

endereo em curtos espaos de

tempo.

ORGANIZAO E ARQUITETURA DE COMPUTADORES 10

Sistema de Memria

Memria cache (Organizao e funcionamento)

(2) Principio da localidade

(espacial e temporal)

(1) Diferena de velocidade

processador->memria principal

Organizao e

funcionamento da

memria cache

Deve possuir elevada

velocidade de transferncia

Tamanho capaz de armazenar

partes de um programa

Suficientemente pequenas para

no elevar o custo do sistema.

ORGANIZAO E ARQUITETURA DE COMPUTADORES 11

Sistema de Memria

Memria cache (Organizao e funcionamento)

Transferncia cache/MP:

Bloco por blocos de palavras

Transferncia cache/processador:

Palavra por palavra

Processador

Memria

Principal

Memria

Cache

BD Barramento de dados

BE Barramento de endereo

BC BC

A conexo entre os dispositivos

comum ao processador a as

duas memorias.

Redundancia

Facilitando a comunicao entre

os trs componentes.

BC

BD - BE

Ec = -------------------- * 100

Acertos (Hit)

Total acessos

Eficincia da cache

ORGANIZAO E ARQUITETURA DE COMPUTADORES 12

Sistema de Memria

Memria cache (Organizao e funcionamento)

Byte

3

Byte

2

Byte

1

Byte

0

. . . . Byte

1

Byte

0

:

:

:

:

:

Byte

1

Linha 0

Linha 1

Linha L-1

B Blocos

Byte 0

Byte 1

Byte 2

Byte 3

Byte 4

Byte 5

Byte 6

Byte 7

Byte 8

Byte N-1

Tag Dados

Bloco 0

Bloco 1

Bloco B-1

Memria principal

N nmero de palavras ou clulas

X nmero de clulas de uma linha

B = ----------- * 100

N

X

ORGANIZAO E ARQUITETURA DE COMPUTADORES 13

Sistema de Memria

Memria cache (Organizao e funcionamento)

No. de Blocos (B) >>> Linhas (L)

Dedicir entre vrias alternativas tecnolgicas:

Mapeamento de dados MP/cache

Direto

Associativo

Associativo por conjunto

Algoritmos de substituo de dados na cache

Poltica de escrita pela cache

Nveis de cache

Definio do tamanho das memrias cache, L1 e L2

Escolha de Largura de linha de cache

Requerendo

ORGANIZAO E ARQUITETURA DE COMPUTADORES 14

Sistema de Memria

Memria cache (Tipos)

Podem se definir dois tipos (ate agora):

UPC/MP (cache de RAM ou RAM Cache)

MP/Discos (cache de disco ou Disk Cache)

ORGANIZAO E ARQUITETURA DE COMPUTADORES 15

Sistema de Memria

Memria cache (Atuais arquiteturas)

http://hothardware.com/printarticle.aspx?articleid=1384

A diviso tradicional entre cache L1 e cache L2 funcionou bem durante a fase dos

processadores single-core e dual-core. Entretanto, com a introduo dos processadores

quad-core passou a fazer mais sentido usar caches L1 e L2 menores e incluir um terceiro

nvel de cache. Com isso, temos 4 pequenos blocos de cache L1 e L2 (um para cada

ncleo) e um grande cache L3 compartilhado entre todos.

Um bom exemplo o Core i7 de

45 nm, que usa 64 KB de cache

L1 e 256 KB de cache L2 por

ncleo e usa um grande cache L3

de 8 MB compartilhado entre

todos. Dentro do processador, ele

corresponde rea sombreada

no diagrama a seguir, novamente

uma rea considervel.

http://en.wikipedia.org/wiki/Gulftown_%28microprocessor%29

ORGANIZAO E ARQUITETURA DE COMPUTADORES 16

Bibliografia

Gabriel Torres. Hardware Curso Completo. Axcel

Books do Brasil Editora Ltda, 4ta edio 2001.

Andrew S. Tanenbaum. Organizao Estruturada de

Computadores. Pearson Prentice Hall, 5ta edio

2007.

Mrio A. Monteiro. Introduo Organizao de

Computadores, LTC Editora S.A., 4ta edio 2001.

http://en.wikipedia.org/

Você também pode gostar

- Apostila Treinamento DeltaDocumento25 páginasApostila Treinamento DeltaJuliano Marcio DA Silva80% (10)

- Dia01 - Questões de Subrede - Todas As QuestõesDocumento32 páginasDia01 - Questões de Subrede - Todas As Questõesedu40% (2)

- Multipic4 16f628 Assembly ApostilaDocumento43 páginasMultipic4 16f628 Assembly ApostilaOirã Vinícius Moreira de OliveiraAinda não há avaliações

- Aula Timers Display 7SEG ArduinoDocumento27 páginasAula Timers Display 7SEG ArduinoJoud da SanfonaAinda não há avaliações

- Aula08 Desmontagem e MontagemDocumento67 páginasAula08 Desmontagem e MontagemRafael Farias de SouzaAinda não há avaliações

- Apostila de Microcontroladores PIC e Perifericos (WWW - Mecatronicadegaragem.blogspot - Com)Documento276 páginasApostila de Microcontroladores PIC e Perifericos (WWW - Mecatronicadegaragem.blogspot - Com)Khelen Diogo NetoAinda não há avaliações

- Watson TDM ResumoDocumento7 páginasWatson TDM ResumoTatianno AlvesAinda não há avaliações

- AE2 - Atividade de Estudo 2Documento3 páginasAE2 - Atividade de Estudo 2Bruno AlexAinda não há avaliações

- Arquitetura de Computadores Unidade I e II DPDocumento19 páginasArquitetura de Computadores Unidade I e II DPvictor cccAinda não há avaliações

- 6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024Documento11 páginas6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024matheus koniczAinda não há avaliações

- Atividade de Pesquisa 01Documento6 páginasAtividade de Pesquisa 01Juliano MartinsAinda não há avaliações

- Pinagem Cabo Serial DB25 - RS232 - Ferramentas PCDocumento7 páginasPinagem Cabo Serial DB25 - RS232 - Ferramentas PCJosé FelipeAinda não há avaliações

- Eletrônica Digital Apostila Portas Lógicas SimplesDocumento16 páginasEletrônica Digital Apostila Portas Lógicas SimplesCarlos Alexandre PavonatoAinda não há avaliações

- Relatorio SemaforoDocumento10 páginasRelatorio Semaforopaulo victorAinda não há avaliações

- Lista Variação Bips - BiosDocumento6 páginasLista Variação Bips - BiosVindictaeAinda não há avaliações

- SSC510 Lista Exerc 02Documento3 páginasSSC510 Lista Exerc 02Nelma Regina Dos Santos TeixeiraAinda não há avaliações

- 5823 - Relatório 1 - João Plácido Neto e João Gabriel BispoDocumento9 páginas5823 - Relatório 1 - João Plácido Neto e João Gabriel BispoNetoAinda não há avaliações

- 5 Micro Parte 5 (PIC) Pratica PDFDocumento197 páginas5 Micro Parte 5 (PIC) Pratica PDFCarollineSouzaAinda não há avaliações

- Circuitos Digitais - ListaDocumento4 páginasCircuitos Digitais - ListaAndré Araújo de Souza SilvaAinda não há avaliações

- Como Funciona 6Documento184 páginasComo Funciona 6parsfreitasAinda não há avaliações

- Tipos de Flip FlopsDocumento12 páginasTipos de Flip FlopsAmerco TivaneAinda não há avaliações

- Apostila Eletronica Digital Aula 3Documento29 páginasApostila Eletronica Digital Aula 3FabricioBrantAinda não há avaliações

- Aula 05 Circuitos Lógicos Combinacionais PDFDocumento5 páginasAula 05 Circuitos Lógicos Combinacionais PDFMauricio Dos SantosAinda não há avaliações

- Aula 04 - Flip FlopsDocumento40 páginasAula 04 - Flip FlopsMarielisa Pereira AlvesAinda não há avaliações

- Memorias PrimariasDocumento24 páginasMemorias Primariasapi-3696124100% (1)

- 04 Circuitos Combinacionais PDFDocumento62 páginas04 Circuitos Combinacionais PDFPedro ThiagoAinda não há avaliações

- Avaliaç o Prática 1Documento2 páginasAvaliaç o Prática 1Luiz FrançaAinda não há avaliações

- RTLDocumento38 páginasRTLanthoniniAinda não há avaliações