Escolar Documentos

Profissional Documentos

Cultura Documentos

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

Enviado por

Natanael RibeiroDireitos autorais:

Formatos disponíveis

Você também pode gostar

- E-Book Maratona VmwareDocumento36 páginasE-Book Maratona VmwareJonathan SouzaAinda não há avaliações

- RONTAN - Manual - Is3000 - Português - Rev 1.1Documento36 páginasRONTAN - Manual - Is3000 - Português - Rev 1.125bpmi telecomAinda não há avaliações

- O Ratinho o Morango Vermelho Maduro e o Grande Urso EsfomeadoDocumento59 páginasO Ratinho o Morango Vermelho Maduro e o Grande Urso EsfomeadoNatanael RibeiroAinda não há avaliações

- As Criancas e o TriviumDocumento8 páginasAs Criancas e o TriviumNatanael RibeiroAinda não há avaliações

- Arquitetura CISCDocumento10 páginasArquitetura CISCskolachado_roAinda não há avaliações

- Arquitetura de Computadores - Questionário 10Documento5 páginasArquitetura de Computadores - Questionário 10Marcus RamosAinda não há avaliações

- Questionário 10Documento5 páginasQuestionário 10Marcus RamosAinda não há avaliações

- Apostila - Projeto e Análise de AlgoritmoDocumento162 páginasApostila - Projeto e Análise de AlgoritmoNatanael RibeiroAinda não há avaliações

- Apostila Arquitetura Risc e Cisc. Noções BásicasDocumento4 páginasApostila Arquitetura Risc e Cisc. Noções BásicasAdr Silva0% (1)

- Microprocessadores & Microcontroladores - Cap. 2Documento33 páginasMicroprocessadores & Microcontroladores - Cap. 220200818Ainda não há avaliações

- O Que É e Qual A Diferenças Entre Risc e CiscDocumento2 páginasO Que É e Qual A Diferenças Entre Risc e CiscAdriano Vieira da SilvaAinda não há avaliações

- RISC e CISC v2Documento8 páginasRISC e CISC v2Otniel PinheiroAinda não há avaliações

- Cita Cinco Principais Vantagens Da Arquitetura Harvard e Cinco Desvantagens Da Arquitetura Von NeumanDocumento43 páginasCita Cinco Principais Vantagens Da Arquitetura Harvard e Cinco Desvantagens Da Arquitetura Von NeumanRuzlan De Jesus PereiraAinda não há avaliações

- Arquitetura Risc e CiscDocumento21 páginasArquitetura Risc e CiscFelipe da SilveiraAinda não há avaliações

- Risc e CiscDocumento5 páginasRisc e CiscInformaAinda não há avaliações

- Trabalho de MICDocumento7 páginasTrabalho de MICOtniel PinheiroAinda não há avaliações

- Lista de Exercicios IIDocumento2 páginasLista de Exercicios IIdouglas_cptAinda não há avaliações

- Arquitetura RISC e CISCDocumento13 páginasArquitetura RISC e CISCAgnaldo Ferreira100% (1)

- Emmerson Silva, Maquina Risc X Cisc.Documento19 páginasEmmerson Silva, Maquina Risc X Cisc.Emerson SilvaAinda não há avaliações

- Risc X CiscDocumento7 páginasRisc X CischeronmarroniAinda não há avaliações

- Risc e CiscDocumento17 páginasRisc e CiscMonique CorrêaAinda não há avaliações

- Questoes CISC e RISCDocumento3 páginasQuestoes CISC e RISCBruna SouzaAinda não há avaliações

- Arquitetura CISC e RISCDocumento27 páginasArquitetura CISC e RISCKeven PaivaAinda não há avaliações

- RISC e CISCDocumento7 páginasRISC e CISCElton MironaAinda não há avaliações

- 2 - Assembly e Risc CiscDocumento25 páginas2 - Assembly e Risc CiscPedroCorreiaAinda não há avaliações

- Arquitetura Dos ProcessadoresDocumento14 páginasArquitetura Dos ProcessadoresDhellano0% (1)

- Avaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFDocumento3 páginasAvaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFJOSE NETOAinda não há avaliações

- CPU RISC e CISCDocumento4 páginasCPU RISC e CISCGiovana Amaro PereiraAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento11 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaCaillou PotterAinda não há avaliações

- Folha de Resposta AVI - Doc MicrocontroladoresDocumento9 páginasFolha de Resposta AVI - Doc MicrocontroladoresfrgengenhariaAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento12 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaJosé ManuelAinda não há avaliações

- Aula III - Arquitectura de Computador PDFDocumento24 páginasAula III - Arquitectura de Computador PDFInvestir VidaAinda não há avaliações

- Arquitetura Cisc e Risc Qual DiferençaDocumento9 páginasArquitetura Cisc e Risc Qual DiferençaAnderson RaposoAinda não há avaliações

- Yury Rodrigues Shelkvosky - Comparativo RISC e CISCDocumento4 páginasYury Rodrigues Shelkvosky - Comparativo RISC e CISCYury ShelkovskyAinda não há avaliações

- Arquiteturas Risc Cisc PDFDocumento23 páginasArquiteturas Risc Cisc PDFmaia_owneedAinda não há avaliações

- Semana 13 ATC 2021Documento21 páginasSemana 13 ATC 2021Sami NzéAinda não há avaliações

- Exercícios RISC - CISCDocumento3 páginasExercícios RISC - CISCNikolas AugustoAinda não há avaliações

- Microprocessadores Overclocking e HyperDocumento4 páginasMicroprocessadores Overclocking e HyperZé PedroAinda não há avaliações

- Arquitetura RAMDocumento30 páginasArquitetura RAMMarco Túlio MarcelinoAinda não há avaliações

- Auscêncio Machavane Júnior - FICHA 11 - ATC - LEIT15Documento7 páginasAuscêncio Machavane Júnior - FICHA 11 - ATC - LEIT15Auscêncio Machavane JRAinda não há avaliações

- ProcessadoresDocumento4 páginasProcessadoresVICTOR HUGO CANDIDO MALVAOAinda não há avaliações

- Resumo de Risc X CiscDocumento7 páginasResumo de Risc X CisckohfuziAinda não há avaliações

- Arquiteturas Risc e CiscDocumento2 páginasArquiteturas Risc e CiscFlavia MagalhãesAinda não há avaliações

- PPPPPDocumento3 páginasPPPPPMesec CarnasfonAinda não há avaliações

- Processadores PDFDocumento2 páginasProcessadores PDFCPUCGAinda não há avaliações

- Artigo Risk CiskDocumento6 páginasArtigo Risk CiskOinoAinda não há avaliações

- CISC e RISCDocumento13 páginasCISC e RISCPaulo Barros100% (1)

- Relatório Arquiteturas de ComputadoresDocumento10 páginasRelatório Arquiteturas de ComputadoresAriel HennigAinda não há avaliações

- Trabalho de Microprocessadores - Kiala MárioDocumento28 páginasTrabalho de Microprocessadores - Kiala MárioKiala MárioAinda não há avaliações

- Artigo Arquitetura Risc Cisc PDFDocumento3 páginasArtigo Arquitetura Risc Cisc PDFMarcelo Rovea Serres100% (1)

- OAS - Aula 8 - Arquitetura de ProcessadoresDocumento44 páginasOAS - Aula 8 - Arquitetura de Processadorestech newAinda não há avaliações

- Arquitetura Superecalar e ParalelaDocumento10 páginasArquitetura Superecalar e ParalelaOssman RaufAinda não há avaliações

- Trabalho 3 - Organização de Computadores - Aline Rose e Max AlexandreDocumento35 páginasTrabalho 3 - Organização de Computadores - Aline Rose e Max AlexandreAline AlencarAinda não há avaliações

- Arquitetura de ProcessadoresDocumento5 páginasArquitetura de ProcessadoresWisley IbraimoAinda não há avaliações

- Resumo MicrocontroladoresDocumento2 páginasResumo MicrocontroladoresFernando FigueiredoAinda não há avaliações

- Arquitetura - CISCDocumento10 páginasArquitetura - CISCWesley Henrique0% (1)

- Arquitectura Do Conjunto de InstrucoesDocumento9 páginasArquitectura Do Conjunto de InstrucoesMário SitoeAinda não há avaliações

- Conceitos de Computação I PtiDocumento1 páginaConceitos de Computação I PtiAndré KimAinda não há avaliações

- Arquitetura de Processadores Cisc e Risc (1) OriginalDocumento11 páginasArquitetura de Processadores Cisc e Risc (1) OriginalClary ManuelAinda não há avaliações

- Arquitetura Harvard - Wikipédia, A Enciclopédia LivreDocumento2 páginasArquitetura Harvard - Wikipédia, A Enciclopédia Livre2007229048Ainda não há avaliações

- Silo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresDocumento53 páginasSilo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresIvanildo SilvaAinda não há avaliações

- Direitos Sociais e NacionalidadeDocumento11 páginasDireitos Sociais e NacionalidadeNatanael RibeiroAinda não há avaliações

- Agentes PúblicosDocumento4 páginasAgentes PúblicosNatanael RibeiroAinda não há avaliações

- Responsabilidade Civil Do EstadoDocumento3 páginasResponsabilidade Civil Do EstadoNatanael RibeiroAinda não há avaliações

- Atos AdministrativosDocumento4 páginasAtos AdministrativosNatanael RibeiroAinda não há avaliações

- VoIP Quality of Service in Networks With Active QuDocumento10 páginasVoIP Quality of Service in Networks With Active QuNatanael RibeiroAinda não há avaliações

- Licitação PúblicaDocumento8 páginasLicitação PúblicaNatanael RibeiroAinda não há avaliações

- Lista de Exercícios - ResolvidosDocumento3 páginasLista de Exercícios - ResolvidosNatanael RibeiroAinda não há avaliações

- Catalogo de Pecas Dcfco12819aDocumento28 páginasCatalogo de Pecas Dcfco12819aFernando KrothAinda não há avaliações

- 3 - TREI - 12 Classe - PLACA MÃEDocumento25 páginas3 - TREI - 12 Classe - PLACA MÃEEdvânio Dos Santos II100% (1)

- Como Instalar o Windows 11 GrátisDocumento20 páginasComo Instalar o Windows 11 GrátisCristiano LimaAinda não há avaliações

- Orçamento Future CPD em AndamentoDocumento2 páginasOrçamento Future CPD em AndamentoEverton SilveiraAinda não há avaliações

- 02 AVR ProgrammerDocumento5 páginas02 AVR Programmerrodrigo dias martinsAinda não há avaliações

- Capinhas No Atacado Resumo Do Pedido 48263Documento3 páginasCapinhas No Atacado Resumo Do Pedido 48263Leonardo GabrielAinda não há avaliações

- Teclado dgp2 641rDocumento4 páginasTeclado dgp2 641rYuri DetoniAinda não há avaliações

- SPW02, SPWC e SPW12 - Dimensões (MM) e Esquemas de LigaçãoDocumento1 páginaSPW02, SPWC e SPW12 - Dimensões (MM) e Esquemas de LigaçãotiagoAinda não há avaliações

- LA FY16Q3 383 Dell PowerEdge T130 SpecSheet Final PT BRDocumento2 páginasLA FY16Q3 383 Dell PowerEdge T130 SpecSheet Final PT BRmanoel mafdosanjosAinda não há avaliações

- Hardware IIDocumento15 páginasHardware IIRAYANE ALIXANDRINO DUARTEAinda não há avaliações

- Engenharia em Tecnologia e Sistemas de InformaçãoDocumento14 páginasEngenharia em Tecnologia e Sistemas de InformaçãouambaAinda não há avaliações

- O Que É o Windows e Como Ele FuncionaDocumento3 páginasO Que É o Windows e Como Ele FuncionaRaquel razaiAinda não há avaliações

- Computação em Nuvem - 2 - Ferramentas de Virtualização de ServidoresDocumento37 páginasComputação em Nuvem - 2 - Ferramentas de Virtualização de ServidoresEvandro CelsoAinda não há avaliações

- 5.2-Eixo Dianteiro Não-MotrizDocumento46 páginas5.2-Eixo Dianteiro Não-Motrizdavi henrique boazAinda não há avaliações

- Catalogo Bojoga 2021Documento44 páginasCatalogo Bojoga 2021cyberkaoAinda não há avaliações

- Relação de Material faltante-MTQ - Rev03Documento23 páginasRelação de Material faltante-MTQ - Rev03LeonardoAinda não há avaliações

- Manual YAR9061-YAR1261-YAR1361-YAR1561Documento4 páginasManual YAR9061-YAR1261-YAR1361-YAR1561britodemateusAinda não há avaliações

- Elétrico Casa Tipo - Ville D'or-FOLHA 01-Plantas Baixas e DetalhesDocumento1 páginaElétrico Casa Tipo - Ville D'or-FOLHA 01-Plantas Baixas e DetalhesSamuel Nogueira da SilvaAinda não há avaliações

- 6034r Rack Aruba BC 6034Documento3 páginas6034r Rack Aruba BC 6034Scorpion ZAinda não há avaliações

- NovaStar Product Catalog 2022 PTDocumento38 páginasNovaStar Product Catalog 2022 PTWalefi SilvaAinda não há avaliações

- Roup Iluminat 6pts 2gvtsDocumento2 páginasRoup Iluminat 6pts 2gvtsCenanda Brum AguilarAinda não há avaliações

- Como Utilizar Algumas Ferramentas Do CD Hírens Boot 10Documento7 páginasComo Utilizar Algumas Ferramentas Do CD Hírens Boot 10JAS-DesignerAinda não há avaliações

- MsinfoDocumento832 páginasMsinfoNeto TrevisanAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento21 páginasArquitetura e Organização de ComputadoresJulianaAinda não há avaliações

- Intelbras CFTVDocumento6 páginasIntelbras CFTVJohnny TorresAinda não há avaliações

- Manutenção em Computadores Revisto PDFDocumento101 páginasManutenção em Computadores Revisto PDFLucas AlmeidaAinda não há avaliações

- MM Casa Chap.23-11-31 23-12-10Documento86 páginasMM Casa Chap.23-11-31 23-12-10L Eka Juangga IAinda não há avaliações

- TRANSMISSAODocumento6 páginasTRANSMISSAOcaparo tratoresAinda não há avaliações

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

Enviado por

Natanael RibeiroTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

ARQUITETURA & ORGANIZAÇÃO - RISC X CISC

Enviado por

Natanael RibeiroDireitos autorais:

Formatos disponíveis

4.4.

RISC x CISC

O projeto do Conjunto de Instruções inicia com a escolha de uma entre duas

abordagens, a abordagem RISC e a CISC. O termo RISC é a abreviação de Reduced

Instruction Set Computer, ou Computador de Conjunto de Instruções Reduzido e

CISC vem de Complex Instruction Set Computer, ou Computador de Conjunto

de Instruções Complexo. Um computador RISC parte do pressuposto de que um

conjunto simples de instruções vai resultar numa Unidade de Controle simples,

barata e rápida. Já os computadores CISC visam criar arquiteturas complexas o

bastante a ponto de facilitar a construção dos compiladores, assim, programas

complexos são compilados em programas de máquina mais curtos. Com programas

mais curtos, os computadores CISC precisariam acessar menos a memória para

buscar instruções e seriam mais rápidos.

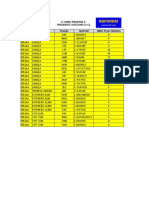

A Tabela 4.4, “Arquiteturas RISC x CISC” resume as principais características dos

computadores RISC em comparação com os CISC. Os processadores RISC geralmente

adotam arquiteturas mais simples e que acessam menos a memória, em favor do

acesso aos registradores. A arquitetura RegistradorRegistrador é mais adotada,

enquanto que os computadores CISC utilizam arquiteturas RegistradorMemória.

Tabela 4.4. Arquiteturas RISC x CISC

Características RISC CISC

Arquitetura Registrador RegistradorMemória

Registrador

Tipos de Dados Pouca variedade Muito variada

Formato das Instruções poucos Instruções com muitos

Instruções endereços endereços

Modo de Pouca variedade Muita variedade

Endereçamento

Estágios de Pipeline Entre 4 e 10 Entre 20 e 30

Acesso aos dados Via registradores Via memória

Como as arquiteturas RISC visam Unidades de Controle mais simples, rápidas e

baratas, elas geralmente optam por instruções mais simples possível, com pouca

variedade e com poucos endereços. A pouca variedade dos tipos de instrução e dos

modos de endereçamento, além de demandar uma Unidade de Controle mais

simples, também traz outro importante benefício, que é a previsibilidade. Como as

intrusões variam pouco de uma para outra, é mais fácil para a Unidade de Controle

prever quantos ciclos serão necessários para executalas. Esta previsibilidade traz

benefícios diretos para o ganho de desempenho com o Pipeline. Ao saber quantos

ciclos serão necessários para executar um estágio de uma instrução, a Unidade de

Controle saberá exatamente quando será possível iniciar o estágio de uma próxima

instrução.

Já as arquiteturas CISC investem em Unidades de Controle poderosas e capazes de

executar tarefas complexas como a Execução Fora de Ordem e a Execução

Superescalar. Na execução Fora de Ordem, a Unidade de Controle analisa uma

sequência de instruções ao mesmo tempo. Muitas vezes há dependências entre uma

instrução e a seguinte, impossibilitando que elas sejam executadas em Pipeline.

Assim, a Unidade de Controle busca outras instruções para serem executadas que não

são as próximas da sequência e que não sejam dependentes das instruções

atualmente executadas. Isso faz com que um programa não seja executado na mesma

ordem em que foi compilado. A Execução Superescalar é a organização do

processador em diversas unidades de execução, como Unidades de Pontos Flutuante

e Unidades de Inteiros. Essas unidades trabalham simultaneamente. Enquanto uma

instrução é executada por uma das unidades de inteiros, outra pode ser executada por

uma das unidades de Pontos Flutuantes. Com a execução Fora de Ordem junto com a

Superescalar, instruções que não estão na sequência definida podem ser executadas

para evitar que as unidades de execução fiquem ociosas.

É importante ressaltar que a execução fora de ordem não afeta o

resultado da aplicação pois foram projetadas para respeitar as

dependências entre os resultados das operações.

Estas características de complexidade tornam os estágios de Pipeline dos

processadores CISC mais longos, em torno de 20 a 30 estágios. Isto porque estas

abordagens de aceleração de execução devem ser adicionadas no processo de

execução. Já os processadores RISC trabalham com estágios mais curtos, em torno de

4 a 10 estágios.

Os processadores CISC também utilizam mais memória principal e Cache, enquanto

que os processadores RISC utilizam mais registradores. Isso porque os processadores

CISC trabalham com um maior volume de instruções e dados simultaneamente. Esses

dados não poderiam ser armazenados em registradores, devido à sua elevada

quantidade e são, geralmente, armazenados em memória Cache. Enquanto que os

processadores RISC trabalham com menos instruções e dados por vez, o que

possibilita a utilização predominante de registradores.

4.4.1. Afinal, qual a melhor abordagem?

Sempre que este assunto é apresentado aos alunos, surge a pergunta crucial sobre

qual é a melhor abordagem, a RISC ou a CISC? Esta é uma pergunta difícil e sem

resposta definitiva. A melhor resposta que acho é de que depende do uso que se quer

fazer do processador.

Processadores RISC geralmente resultam em projetos menores, mais baratos e que

consumem menos energia. Isso tornaos muito interessante para dispositivos móveis

e computadores portáteis mais simples. Já os processadores CISC trabalham com

clock muito elevado, são mais caros e mais poderosos no que diz respeito a

desempenho. Entretanto, eles são maiores e consomem mais energia, o que os torna

mais indicados para computadores de mesa e notebooks mais poderosos, além de

servidores e computadores profissionais.

Os processadores CISC iniciaram com processadores mais simples e depois foram

incorporando mais funcionalidades. Os fabricantes, como a Intel e a AMD,

precisavam sempre criar novos projetos mas mantendo a compatibilidade com as

gerações anteriores. Ou seja, o Conjunto de Instruções executado pelo 486 precisa

também ser executado pelo Pentium para os programas continuassem compatíveis. O

Pentium IV precisou se manter compatível ao Pentium e o Duo Core é compatível

com o Pentium IV. Isso tornou o projeto dos processadores da Intel e AMD muito

complexos, mas não pouco eficientes. Os computadores líderes mundiais em

competições de desempenho computacional utilizam processadores CISC.

Já o foco dos processadores RISC está na simplicidade e previsibilidade. Além do

benefício da previsibilidade do tempo de execução ao Pipeline, ele também é muito

interessante para aplicações industriais. Algumas dessas aplicações são chamadas de

Aplicações de Tempo Real. Essas aplicações possuem como seu requisito principal o

tempo para realizar as tarefas. Assim, o Sistema Operacional precisa saber com

quantos milissegundos um programa será executado. Isso só é possível com

processadores RISC, com poucos estágios de Pipeline, poucos tipos de instrução,

execução em ordem etc. Mesmo que os processadores RISC sejam mais lentos do que

os CISC, eles são mais utilizados nessas aplicações críticas e de tempo real, como

aplicações industriais, de automação e robótica.

Você também pode gostar

- E-Book Maratona VmwareDocumento36 páginasE-Book Maratona VmwareJonathan SouzaAinda não há avaliações

- RONTAN - Manual - Is3000 - Português - Rev 1.1Documento36 páginasRONTAN - Manual - Is3000 - Português - Rev 1.125bpmi telecomAinda não há avaliações

- O Ratinho o Morango Vermelho Maduro e o Grande Urso EsfomeadoDocumento59 páginasO Ratinho o Morango Vermelho Maduro e o Grande Urso EsfomeadoNatanael RibeiroAinda não há avaliações

- As Criancas e o TriviumDocumento8 páginasAs Criancas e o TriviumNatanael RibeiroAinda não há avaliações

- Arquitetura CISCDocumento10 páginasArquitetura CISCskolachado_roAinda não há avaliações

- Arquitetura de Computadores - Questionário 10Documento5 páginasArquitetura de Computadores - Questionário 10Marcus RamosAinda não há avaliações

- Questionário 10Documento5 páginasQuestionário 10Marcus RamosAinda não há avaliações

- Apostila - Projeto e Análise de AlgoritmoDocumento162 páginasApostila - Projeto e Análise de AlgoritmoNatanael RibeiroAinda não há avaliações

- Apostila Arquitetura Risc e Cisc. Noções BásicasDocumento4 páginasApostila Arquitetura Risc e Cisc. Noções BásicasAdr Silva0% (1)

- Microprocessadores & Microcontroladores - Cap. 2Documento33 páginasMicroprocessadores & Microcontroladores - Cap. 220200818Ainda não há avaliações

- O Que É e Qual A Diferenças Entre Risc e CiscDocumento2 páginasO Que É e Qual A Diferenças Entre Risc e CiscAdriano Vieira da SilvaAinda não há avaliações

- RISC e CISC v2Documento8 páginasRISC e CISC v2Otniel PinheiroAinda não há avaliações

- Cita Cinco Principais Vantagens Da Arquitetura Harvard e Cinco Desvantagens Da Arquitetura Von NeumanDocumento43 páginasCita Cinco Principais Vantagens Da Arquitetura Harvard e Cinco Desvantagens Da Arquitetura Von NeumanRuzlan De Jesus PereiraAinda não há avaliações

- Arquitetura Risc e CiscDocumento21 páginasArquitetura Risc e CiscFelipe da SilveiraAinda não há avaliações

- Risc e CiscDocumento5 páginasRisc e CiscInformaAinda não há avaliações

- Trabalho de MICDocumento7 páginasTrabalho de MICOtniel PinheiroAinda não há avaliações

- Lista de Exercicios IIDocumento2 páginasLista de Exercicios IIdouglas_cptAinda não há avaliações

- Arquitetura RISC e CISCDocumento13 páginasArquitetura RISC e CISCAgnaldo Ferreira100% (1)

- Emmerson Silva, Maquina Risc X Cisc.Documento19 páginasEmmerson Silva, Maquina Risc X Cisc.Emerson SilvaAinda não há avaliações

- Risc X CiscDocumento7 páginasRisc X CischeronmarroniAinda não há avaliações

- Risc e CiscDocumento17 páginasRisc e CiscMonique CorrêaAinda não há avaliações

- Questoes CISC e RISCDocumento3 páginasQuestoes CISC e RISCBruna SouzaAinda não há avaliações

- Arquitetura CISC e RISCDocumento27 páginasArquitetura CISC e RISCKeven PaivaAinda não há avaliações

- RISC e CISCDocumento7 páginasRISC e CISCElton MironaAinda não há avaliações

- 2 - Assembly e Risc CiscDocumento25 páginas2 - Assembly e Risc CiscPedroCorreiaAinda não há avaliações

- Arquitetura Dos ProcessadoresDocumento14 páginasArquitetura Dos ProcessadoresDhellano0% (1)

- Avaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFDocumento3 páginasAvaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFJOSE NETOAinda não há avaliações

- CPU RISC e CISCDocumento4 páginasCPU RISC e CISCGiovana Amaro PereiraAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento11 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaCaillou PotterAinda não há avaliações

- Folha de Resposta AVI - Doc MicrocontroladoresDocumento9 páginasFolha de Resposta AVI - Doc MicrocontroladoresfrgengenhariaAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento12 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaJosé ManuelAinda não há avaliações

- Aula III - Arquitectura de Computador PDFDocumento24 páginasAula III - Arquitectura de Computador PDFInvestir VidaAinda não há avaliações

- Arquitetura Cisc e Risc Qual DiferençaDocumento9 páginasArquitetura Cisc e Risc Qual DiferençaAnderson RaposoAinda não há avaliações

- Yury Rodrigues Shelkvosky - Comparativo RISC e CISCDocumento4 páginasYury Rodrigues Shelkvosky - Comparativo RISC e CISCYury ShelkovskyAinda não há avaliações

- Arquiteturas Risc Cisc PDFDocumento23 páginasArquiteturas Risc Cisc PDFmaia_owneedAinda não há avaliações

- Semana 13 ATC 2021Documento21 páginasSemana 13 ATC 2021Sami NzéAinda não há avaliações

- Exercícios RISC - CISCDocumento3 páginasExercícios RISC - CISCNikolas AugustoAinda não há avaliações

- Microprocessadores Overclocking e HyperDocumento4 páginasMicroprocessadores Overclocking e HyperZé PedroAinda não há avaliações

- Arquitetura RAMDocumento30 páginasArquitetura RAMMarco Túlio MarcelinoAinda não há avaliações

- Auscêncio Machavane Júnior - FICHA 11 - ATC - LEIT15Documento7 páginasAuscêncio Machavane Júnior - FICHA 11 - ATC - LEIT15Auscêncio Machavane JRAinda não há avaliações

- ProcessadoresDocumento4 páginasProcessadoresVICTOR HUGO CANDIDO MALVAOAinda não há avaliações

- Resumo de Risc X CiscDocumento7 páginasResumo de Risc X CisckohfuziAinda não há avaliações

- Arquiteturas Risc e CiscDocumento2 páginasArquiteturas Risc e CiscFlavia MagalhãesAinda não há avaliações

- PPPPPDocumento3 páginasPPPPPMesec CarnasfonAinda não há avaliações

- Processadores PDFDocumento2 páginasProcessadores PDFCPUCGAinda não há avaliações

- Artigo Risk CiskDocumento6 páginasArtigo Risk CiskOinoAinda não há avaliações

- CISC e RISCDocumento13 páginasCISC e RISCPaulo Barros100% (1)

- Relatório Arquiteturas de ComputadoresDocumento10 páginasRelatório Arquiteturas de ComputadoresAriel HennigAinda não há avaliações

- Trabalho de Microprocessadores - Kiala MárioDocumento28 páginasTrabalho de Microprocessadores - Kiala MárioKiala MárioAinda não há avaliações

- Artigo Arquitetura Risc Cisc PDFDocumento3 páginasArtigo Arquitetura Risc Cisc PDFMarcelo Rovea Serres100% (1)

- OAS - Aula 8 - Arquitetura de ProcessadoresDocumento44 páginasOAS - Aula 8 - Arquitetura de Processadorestech newAinda não há avaliações

- Arquitetura Superecalar e ParalelaDocumento10 páginasArquitetura Superecalar e ParalelaOssman RaufAinda não há avaliações

- Trabalho 3 - Organização de Computadores - Aline Rose e Max AlexandreDocumento35 páginasTrabalho 3 - Organização de Computadores - Aline Rose e Max AlexandreAline AlencarAinda não há avaliações

- Arquitetura de ProcessadoresDocumento5 páginasArquitetura de ProcessadoresWisley IbraimoAinda não há avaliações

- Resumo MicrocontroladoresDocumento2 páginasResumo MicrocontroladoresFernando FigueiredoAinda não há avaliações

- Arquitetura - CISCDocumento10 páginasArquitetura - CISCWesley Henrique0% (1)

- Arquitectura Do Conjunto de InstrucoesDocumento9 páginasArquitectura Do Conjunto de InstrucoesMário SitoeAinda não há avaliações

- Conceitos de Computação I PtiDocumento1 páginaConceitos de Computação I PtiAndré KimAinda não há avaliações

- Arquitetura de Processadores Cisc e Risc (1) OriginalDocumento11 páginasArquitetura de Processadores Cisc e Risc (1) OriginalClary ManuelAinda não há avaliações

- Arquitetura Harvard - Wikipédia, A Enciclopédia LivreDocumento2 páginasArquitetura Harvard - Wikipédia, A Enciclopédia Livre2007229048Ainda não há avaliações

- Silo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresDocumento53 páginasSilo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresIvanildo SilvaAinda não há avaliações

- Direitos Sociais e NacionalidadeDocumento11 páginasDireitos Sociais e NacionalidadeNatanael RibeiroAinda não há avaliações

- Agentes PúblicosDocumento4 páginasAgentes PúblicosNatanael RibeiroAinda não há avaliações

- Responsabilidade Civil Do EstadoDocumento3 páginasResponsabilidade Civil Do EstadoNatanael RibeiroAinda não há avaliações

- Atos AdministrativosDocumento4 páginasAtos AdministrativosNatanael RibeiroAinda não há avaliações

- VoIP Quality of Service in Networks With Active QuDocumento10 páginasVoIP Quality of Service in Networks With Active QuNatanael RibeiroAinda não há avaliações

- Licitação PúblicaDocumento8 páginasLicitação PúblicaNatanael RibeiroAinda não há avaliações

- Lista de Exercícios - ResolvidosDocumento3 páginasLista de Exercícios - ResolvidosNatanael RibeiroAinda não há avaliações

- Catalogo de Pecas Dcfco12819aDocumento28 páginasCatalogo de Pecas Dcfco12819aFernando KrothAinda não há avaliações

- 3 - TREI - 12 Classe - PLACA MÃEDocumento25 páginas3 - TREI - 12 Classe - PLACA MÃEEdvânio Dos Santos II100% (1)

- Como Instalar o Windows 11 GrátisDocumento20 páginasComo Instalar o Windows 11 GrátisCristiano LimaAinda não há avaliações

- Orçamento Future CPD em AndamentoDocumento2 páginasOrçamento Future CPD em AndamentoEverton SilveiraAinda não há avaliações

- 02 AVR ProgrammerDocumento5 páginas02 AVR Programmerrodrigo dias martinsAinda não há avaliações

- Capinhas No Atacado Resumo Do Pedido 48263Documento3 páginasCapinhas No Atacado Resumo Do Pedido 48263Leonardo GabrielAinda não há avaliações

- Teclado dgp2 641rDocumento4 páginasTeclado dgp2 641rYuri DetoniAinda não há avaliações

- SPW02, SPWC e SPW12 - Dimensões (MM) e Esquemas de LigaçãoDocumento1 páginaSPW02, SPWC e SPW12 - Dimensões (MM) e Esquemas de LigaçãotiagoAinda não há avaliações

- LA FY16Q3 383 Dell PowerEdge T130 SpecSheet Final PT BRDocumento2 páginasLA FY16Q3 383 Dell PowerEdge T130 SpecSheet Final PT BRmanoel mafdosanjosAinda não há avaliações

- Hardware IIDocumento15 páginasHardware IIRAYANE ALIXANDRINO DUARTEAinda não há avaliações

- Engenharia em Tecnologia e Sistemas de InformaçãoDocumento14 páginasEngenharia em Tecnologia e Sistemas de InformaçãouambaAinda não há avaliações

- O Que É o Windows e Como Ele FuncionaDocumento3 páginasO Que É o Windows e Como Ele FuncionaRaquel razaiAinda não há avaliações

- Computação em Nuvem - 2 - Ferramentas de Virtualização de ServidoresDocumento37 páginasComputação em Nuvem - 2 - Ferramentas de Virtualização de ServidoresEvandro CelsoAinda não há avaliações

- 5.2-Eixo Dianteiro Não-MotrizDocumento46 páginas5.2-Eixo Dianteiro Não-Motrizdavi henrique boazAinda não há avaliações

- Catalogo Bojoga 2021Documento44 páginasCatalogo Bojoga 2021cyberkaoAinda não há avaliações

- Relação de Material faltante-MTQ - Rev03Documento23 páginasRelação de Material faltante-MTQ - Rev03LeonardoAinda não há avaliações

- Manual YAR9061-YAR1261-YAR1361-YAR1561Documento4 páginasManual YAR9061-YAR1261-YAR1361-YAR1561britodemateusAinda não há avaliações

- Elétrico Casa Tipo - Ville D'or-FOLHA 01-Plantas Baixas e DetalhesDocumento1 páginaElétrico Casa Tipo - Ville D'or-FOLHA 01-Plantas Baixas e DetalhesSamuel Nogueira da SilvaAinda não há avaliações

- 6034r Rack Aruba BC 6034Documento3 páginas6034r Rack Aruba BC 6034Scorpion ZAinda não há avaliações

- NovaStar Product Catalog 2022 PTDocumento38 páginasNovaStar Product Catalog 2022 PTWalefi SilvaAinda não há avaliações

- Roup Iluminat 6pts 2gvtsDocumento2 páginasRoup Iluminat 6pts 2gvtsCenanda Brum AguilarAinda não há avaliações

- Como Utilizar Algumas Ferramentas Do CD Hírens Boot 10Documento7 páginasComo Utilizar Algumas Ferramentas Do CD Hírens Boot 10JAS-DesignerAinda não há avaliações

- MsinfoDocumento832 páginasMsinfoNeto TrevisanAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento21 páginasArquitetura e Organização de ComputadoresJulianaAinda não há avaliações

- Intelbras CFTVDocumento6 páginasIntelbras CFTVJohnny TorresAinda não há avaliações

- Manutenção em Computadores Revisto PDFDocumento101 páginasManutenção em Computadores Revisto PDFLucas AlmeidaAinda não há avaliações

- MM Casa Chap.23-11-31 23-12-10Documento86 páginasMM Casa Chap.23-11-31 23-12-10L Eka Juangga IAinda não há avaliações

- TRANSMISSAODocumento6 páginasTRANSMISSAOcaparo tratoresAinda não há avaliações