Escolar Documentos

Profissional Documentos

Cultura Documentos

9a Aula PDF

Enviado por

Bruno SilvaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

9a Aula PDF

Enviado por

Bruno SilvaDireitos autorais:

Formatos disponíveis

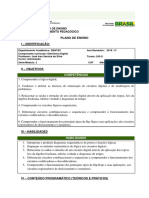

Aula 09

Memrias e Circuitos Digitais Seqenciais

Introduo

Os circuitos lgicos estudados at aqui so chamados de

combinacionais (ou combinatrios). So assim chamados porque a sua

sada depende apenas dos valores presentes nas suas entradas. Portanto,

esses circuitos no possuem memria.

Os circuitos lgicos que incorporam memria so denominados

circuitos seqenciais; isto , sua sada no depende apenas do valor

presente na entrada, mas tambm dos valores de instantes anteriores.

Esses circuitos requerem, para sua operao, o uso de um relgio

(clock) de temporizao.

H basicamente duas formas para fazer com que um circuito

digital tenha memria, essas so:

1. Realimentao positiva

2. Armazenamento de carga em um capacitor.

A realimentao positiva faz com o circuito tenha dois estados

estveis. Tal circuito biestvel pode ser empregado par armazenar um

bit de informao. Um circuito biestvel pode permanecer em dado

estado indefinidamente na ausncia de sinal e, portanto, pertence

categoria de circuitos seqncias estticos.

O armazenamento de carga em um capacitor indicar um 1

quando estiver carregado; quando estiver descarregado, ter um 0

armazenado. Uma vez que as correntes de fuga so inevitveis e

causam a descarga do capacitor, ele necessitar ser regenerado

periodicamente, no processo conhecido como restaurao. Portanto,

como na lgica dinmica, memrias baseadas no armazenamento de

cargas so conhecidas como memrias dinmicas e pertencem classe

de circuitos seqncias dinmicas.

O Latch

O elemento bsico de memria, lacth est representado na figura

A.9.1 a). Ele consiste em dois inversores lgicos, G

1

e G

2

, conectados

em malhas fechada. Os inversores forma uma malha de realimentao

positiva.

Figura A.9.1 a) Latch bsico. b) O latch com a malha de realimentao

aberta. c)Determinao do ponto de operao do latch.

Princpio de funcionamento

Para entender o funcionamento do latch, vamos abrir a malha de

realimentao do inversor G

1

(por, exemplo) e aplicar um voltagem v

W

que varia de 0 V at uma tenso maior que V

OH

; como indicado na

figura A.9.1 b). A caracterstica de transferncia dos dois inversores

est mostrada figura A.9.1 c). Observe que essa caracterstica consiste

em trs segmentos, com o segmento do meio correspondendo regio

de transio dos inversores.

mostrada tambm na figura uma reta com inclinao 1. Essa

reta representa a relao entrada igual a sada (v

W

= v

Z

), que obtida

quando conectamos os pontos W e Z.

Como pode ser observado na figura, a linha reta intercepta a curva

de transferncia em trs pontos, A, B e C. deixado por aluno mostrar

que, enquanto os pontos A e C so estveis, no sentido em que o

circuito permanece em um deles indefinidamente, o ponto B um ponto

de operao instvel; o latch no pode permanecer por um perodo

significativo.

Portanto o latch um circuito biestvel que possui duas sadas

complementares. O estado estvel no qual o latch opera depende da

excitao externa que o fora para um estado particular. O latch ento

memoriza essa ao externa, permanecendo indefinidamente no estado

a que foi levado. Como elemento de memria, o latch capaz de

armazenar um bit de informao. Finalmente, deve ser bvio que o

circuito latch descrito do tipo esttico.

Analisaremos a seguir, o mecanismo pelo qual o latch pode ser

disparado, para mudar de estado. O latch, junto com o circuito de

disparo, forma um flip-flop.

O flip-flop

O tipo mais simples de flip-flop o set/reset (RS ou SR),

mostrado na figura A.9.2 a). formado por duas portas NOU (ou NOR)

interligadas por conexes cruzadas entre entradas e sadas e, portanto,

incorpora um latch. A segunda entrada de cada porta NOU usada para

entradas de disparos do flip-flop. Essas duas entradas so denominadas

S (para set) e R (para reset). As sadas so chamadas Q e Q,

enfatizando o fato de que elas so complementares. Considera-se o flip-

flop no estado de set (isto , armazenando um 1 lgico) quando Q alta

e Q baixa. Quando o flip-flop est no outro estado (Q baixa e Q alta),

ele considerado em reset (armazenando um 0 lgico).

Figura A.9.2 O flip-flop tipo set/reset (SR) e sua tabela verdade.

Q

A operao do flip-flop est resumida pela tabela verdade na

figura A.9.2 b), na qual Q

n

representa o valor de Q no instante t

n

antes

da aplicao dos sinais R e S, e Q

n+1

representa o valor de Q no

instantes t

n+1

aps a aplicao dos sinais de entrada.

Operao do flip-flop

Consideraremos o caso em que o flip-flop est memorizando o 0

lgico. Uma vez que Q ser baixa, as duas entradas da porta NOU P

2

sero baixas. Sua sada ento ser alta. Esse nvel alto aplicado a

entrada de P

1

, fazendo com que a sada Q seja baixa, satisfazendo a

condio inicial. Para o estado set do flip-flop, elevamos a entrada S

para o nvel lgico 1, enquanto mantemos R em 0. O 1 no terminal A

forar a sada de P

2

, Q, para 0. portanto, as duas entradas de P

1

sero

0 e sua sada Q ser 1. No entanto, mesmo que S volte para 0, o flip-flop

permanecer no ltimo estado adquirido, set. Obviamente, se elevarmos

S para 1 novamente (com R permanecendo em 0), no haver

modificao. Para o estado de reset do flip-flop, precisamos elevar R

para 1, enquanto mantemos S = 0. Podemos mostrar de imediato que

isso fora o flip-flop ao estado de reset e o flip-flop permanecer nesse

estado, mesmo depois de R retornar a 0. Devemos observar que o sinal

de disparo simplesmente d incio ao regenerativa da malha de

realimentao do lacth.

Finalmente deixamos como exerccio para o aluno mostrar que as

sada do flip-flop ficam indeterminada, caso as duas entradas forem

elevadas para o nvel lgico 1.

Em vez de utilizarmos duas porta NOU, podemos implementar

tambm um flip-flop SR pela conexo de duas porta NE(ou NAND)

interligadas por conexes cruzadas, em que as funes set e reset

estaro ativas quando em nvel baixo e as entradas sero, dessa forma,

chamadas de S e R.

Implementao de flip-flop tipo SR em CMOS

O flip-flop da figura A.9.2 pode ser diretamente implementado em

CMOS simplesmente substituindo cada uma das portas NOU por seu

correspondente circuito CMOS j visto. Deixamos como exerccio para

o aluno esboar o circuito resultante. Embora o circuito assim obtido

funcione muito bem, ele relativamente complexo. Como alternativa,

consideraremos o circuito simplificado que, alm do mais, implementa

uma lgica adicional. Especificamente, a figura A.9.3 mostra outra

verso de flip-flop SR controlada por um sinal de relgio. Visto que as

entradas de relgio formam funes E com as entradas set e reset, o

flip-flop pode ser setado e resetado quando o sinal de relgio estiver

em nvel alto. Observe que, embora os inversores ligados de forma

cruzadas no ncleo do flip-flop sejam do tipo CMOS complementar,

somente os transistores NMOS realizam as funes de ativar o set-

reset. Todavia, uma vez que no h um caminho entre V

DD

e terra

(exceto durante o chaveamento), o circuito no dissipa nenhuma

potncia esttica.

Figura A.9.3 Implementao CMOS de um flip-flop SR com sinal de

relgio. O sinal de relgio est indicado por .

Operao do flip-flop SR dinmico

Considere inicialmente quando o flip-flop est no estado reset (Q

= 0, Q = 1, isto , v

Q

= 0 e

Q

v = V

DD

) e desejamos pass-los para o

estado set. Para tanto, aplicaremos um nvel alto na entrada S, enquanto

R mantido em nvel baixo. Ento, quando o relgio for para o nvel

alto, tanto Q

5

como Q

6

conduziro e faro a tenso

Q

v abaixar. Se

Q

v

cair abaixo da tenso de transio do inversor formado por (Q

3

e Q

4

)

sua sada mudar de estado (ou pelo menos comear a mudar de

estado) e a tenso v

Q

subir. Esse aumento de v

Q

ser realimentado para

entrada do inversor formado por Q

1

e Q

2

, fazendo com que

Q

v por sua

vez, tenha sua tenso de sada diminuda at chegar em 0 V. Esse

processo de realimentao positiva caracterstica do latch.

Duas hipteses foram admitidas na anlise acima do flip-flop

dinmico:

1. Os transistores Q

5

e Q

6

fornecem corrente suficiente para abaixar

a tenso no n Q ao menos levemente abaixo da tenso de

transio do inversor Q

3

e Q

4

. Isso essencial para que o processo

iniciar regenerativo. Sem essa excitao inicial o flip-flop no

chavear.

2. O sinal set deve permanecer em nvel alto por um intervalo de

tempo suficiente longo para fazer com que o processo

regenerativo acontea durante o chaveamento. Uma estimativa

para largura mnima necessria para o pulso set pode ser obtida

somando o intervalo em que

Q

v reduzido de V

DD

para V

DD

/2 com

o intervalo para que a tenso v

Q

passe de 0 a V

DD

/2.

Finalmente, dado a simetria do circuito, todas essa observaes se

aplicam ao processo reset.

Exemplo:

O flip-flop SR CMOS mostrado na figura A.9.3 fabricado em

uma tecnologia para qual

n

C

ox

= 50 A/V

2

,

p

C

ox

= 20, V

Tn0

= - V

Tp0

=

V

T0

= 1,0 V e V

DD

= 5 V. Os inversores tm (W/L)

n

= 4 m/2 m e

(W/L)

p

= 10 m/2 m. os quatro transistores NMOS no circuito set/reset

tm razes (W/L) idnticas. Determine o valor mnimo necessrio para

essa razo garantir que o flip-flop chavear.

Soluo:

A figura A.9.4 mostra a parte relevante do circuito flip-flop para

anlise neste exemplo. Observe que o processo de regenerao ainda

no comeou e supe-se que

Q

v = 0 e, portanto, Q

2

estar conduzindo.

Dessa forma, o circuito se comporta como uma porta psedo-NMOS e

nossa tarefa escolher as razes (W/L) para Q

5

e Q

6

, tal que o valor de

V

OL

desse inversor seja menor que V

DD

/2 (isto , a transio do inversor

formado por Q

3

e Q

4

(que so casados).

Para encontramos o valor mnimo necessrio de (W/L)

utilizaremos dois caminhos. No primeiro igualamos as correntes que

passam por Q

2

, Q

5

e Q

6

na situao onde

Q

v = V

DD

/2 e que podemos

supor que os transistores Q

5

e Q

6

podem ser substitudo por um

transistor de (W/L)

equiv.

(associao em srie) igual metade da razo de

(W/L)

5

e (W/L)

6

. Assim, verificando que os transistores Q

5

e Q

6

esto

operando na regio de triodo, temos

( ) ( ) ( )

(

\

|

=

(

\

| 2

2

' 2

5

'

2

1

| | ) (

2

1

2

1

SD SD Tp SG

Q

p DS DS Tn GS

Q

n

V V V V

L

W

k V V V V

L

W

k

( ) ( ) ( )

(

\

|

=

(

\

| 2

2

2

5

2 / 5

2

1

2 / 5 1 5

2

10

20 ) 2 / 5 (

2

1

2 / 5 1 5

2

1

50

Q Q

L

W

2 5

2

10

20

2

1

50

Q Q

L

W

|

\

|

=

|

\

|

logo,

4

5

=

|

\

|

Q

L

W

e 4

6

=

|

\

|

Q

L

W

Figura A.9.4 Parte importante do circuito do flip-flop para determinar

as razes mnimas (W/L) de Q

5

e Q

6

para garantir o chaveamento.

A segunda maneira de determinarmos a razo mnima de (W/L)

Q5

e (W/L)

Q6

admitindo que a metade da tenso de sada

Q

v = V

DD

/2

ficar sobre cada um dos transistores e, como para esta situao o

transistore que fica sujeito a menor tenso V

GS

o transistor Q

6

, ento

faremos a corrente que passa por este transistor igual a corrente que

passa por Q

2

, portanto

( ) ( ) ( )

(

\

|

=

(

\

| 2

2

' 2

6

'

2

1

| | ) (

2

1

SD SD Tp SG

Q

p DS DS Tn GS

Q

n

V V V V

L

W

k V V V V

L

W

k

( ) ( ) ( )

(

\

|

=

(

\

| 2

2

2

6

2 / 5

2

1

2 / 5 1 5

2

10

20 ) 4 / 5 (

2

1

4 / 5 1 4 / 5 5 50

Q Q

L

W

(

\

|

=

(

\

|

8

55

2

200

32

85

50

2 6 Q Q

L

W

logo,

2 . 5

6

\

|

Q

L

W

e 2 . 5

5

\

|

Q

L

W

Um valor muito prximo do resultado anterior. Lembrando que este

um valor mnimo absoluto, poderamos, na prtica escolher uma razo

6 ou 7.

Exerccio:

Repita o exemplo anterior para determinar o valor mnimo

necessrio de (W/L)

Q5

= (W/L)

Q6

tal que o chaveamento ocorra quando

as entradas S e estiverem em V

DD

/2.

Resposta : 24,4.

Implementao mais simples de flip-flop SR dinmico

Uma implementao mais simples para uma flip-flop SR

controlado por relgio mostrada na figura A.9.5. Nesse caso, a lgica

de transistores de passagem empregada para implementar as funes

set-reset por relgio.

Esse circuito comum como clula bsica de memria esttica de

acesso randmico (static random-access memory SRAM).

Figura A.9.5 Uma implementao CMOS mais simples de um flip-flop

SR controlado por relgio.

Circuitos flip-flop tipo D

Existem vrios tipos de flip-flop. Muitos podem ser sintetizados

em termos de portas lgicas. As portas lgicas depois podem ser

substitudas pela implementao CMOS de seus circuitos. Essa

abordagem simples quase sempre leva para uma implementao mais

complexa. Em muitos casos, circuitos mais simples podem ser

projetados em vez do projeto a partir de portas lgicas. Para ilustrar

isso, apresentaremos o projeto de um circuito de um flip-flop de dados

ou tipo D.

O flip-flop tipo D apresentado em forma de diagrama de blocos

na figura A.9.6. Este tem duas entradas, a entrada de dados D e a

entrada do relgio . As sadas complementares Q e Q. Quando a

entrada do relgio for baixa, o flip-flop est no estado de memria ou

repouso; a mudana no sinal de dados no tem nenhum efeito nas

sadas do flip-flop. Quando o relgio vai para o nvel alto, o flip-flop

adquire o nvel lgico presente em D logo na subida da borda do pulso

de relgio. Diz-se que esse flip-flop disparado pela borda (edge-

triggered). Algumas implementaes do flip-flop tipo D incluem

tambm as entradas de set e reset que se impem sobre a operao com

o relgio que acabamos de descrever.

Figura A.9.6 Representao na forma de diagrama de blocos de um flip-

flop tipo D

Uma simples implementao de um flip-flop tipo D apresentada

na figura A.9.7. O circuito consiste em dois inversores conectados em

uma malha de realimentao positiva como se fosse um latch esttico

semelhante quele mostrado na figura A.9.1, exceto que aqui a malha

de realimentao fica fechada por apenas uma parte do tempo.

Especificamente, a malha de realimentao estar fechada quando o

sinal de relgio estiver em nvel baixo ( =0, 1 = ). A entrada D est

conectada no flip-flop por meio de uma chave que fecha quando o sinal

de relgio est em nvel alto. O princpio de funcionamento direto:

quando =1, a malha de realimentao estar aberta e a entrada D

estar conectada na entrada do inversor P

1

. A capacitncia de entrada

do n P

1

ser carregada com o mesmo valor de D e a capacitncia no de

entrada P

2

ser carregada com o valor de D. Ento, quando o sinal de

relgio passar a nvel baixo, a linha de entrada ficar isolada do flip-

flop, a malha de realimentao passa a ficar fechada e o latch adquire o

valor de D assim que vai para nvel baixo, fornecendo uma sada Q =

D.

Este circuito combina a tcnica de realimentao positiva presente

em circuitos biestveis estticos com a tcnica de armazenamento de

cargas de circuitos dinmicos.

Finalmente, importante observar que para uma operao

apropriada deste e de muitos outros circuitos que empregam sinais de

relgio necessrio que e no devem estar simultaneamente em

nvel alto em nenhum instante. Essa condio definida em relao as

duas fases de relgio como fases no sobrepostas (nonoverlapping).

Figura A.9.7 Uma simples implementao de um flip-flop tipo D. a)

emprega um sinal de relgio com duas fases no superpostas mostradas

em b).

Observando mais atentamente o circuito da figura A.9.7 notamos

que, durante o intervalo de tempo em que est em nvel alto, a sada

do flip-flop segue o mesmo sinal da linha de entrada D. Isso pode

ocasionar problemas em determinadas situaes de projetos lgico. O

problema pode ser resolvido de forma efetiva utilizando a configurao

mestre-escravo (master-slave) mostrada na figura A.9.8.

O circuito mestre-escravo consiste em um par de circuitos do tipo

mostrado na figura A.9.7, controlado por fases de relgio alternadas.

Aqui, para enfatizar que as duas fases de relgio no devem apresentar

sobreposio, vamos represent-las por

1

e

2

, conforme mostrado na

figura A.9.7 b). A operao do circuito a seguinte:

1. Quando

1

est em nvel alto e

2

est em nvel baixo, a entrada

est conectada ao latch-mestre cuja malha de realimentao est

aberta, enquanto o latch escravo est isolado. Portanto, a sada Q

permanece no valor previamente armazenado no latch escravo

cuja malha de realimentao est agora fechada. As capacitncias

nodais do latch mestre so carregadas com as tenses apropriadas

correspondentes ao valor presente de D.

2. Quando

1

vai para nvel baixo, o latch-mestre est isolado da

linha de dados da entrada. Ento, quando

2

vai para o nvel alto,

a malha de realimentao do latch-mestre passa a estar fechada e

o valor de D fica constante e armazenado. Alm disso, sua sada

est conectada ao latch escravo cuja malha de realimentao est

agora aberta. As capacitncias nodais no escravo so

apropriadamente carregadas tal que, quando

1

vai para nvel alto

novamente, o latch escravo trava em um novo valor de D e

fornece-o na sada, Q = D.

A partir dessa descrio, notamos que, na transio positiva do sinal

de relgio

2

, a sada Q adota o valor de D que havia na linha D no

fim da fase de relgio anterior,

1

. Esse valor de sada permanece

constante por um perodo de relgio. Finalmente, note que, durante o

intervalo sem sobreposio em nvel baixo, ambos os latches tm

suas malhas de realimentao abertas e teremos as capacitncias

nodais mantendo a maior parte da sua carga. Nesse caso, o intervalo

sem sobreposio deve ser feito o mais curto possvel (da ordem de

1ns ou menos na prtica).

Figura A.9.8 a) Um flip-flop D mestre-escravo. b) Formas de onda do

relgio no superpostas.

Você também pode gostar

- MIFalcão MatLab 2001 PDFDocumento71 páginasMIFalcão MatLab 2001 PDFBruno SilvaAinda não há avaliações

- Circuito Magazine Volume 6Documento26 páginasCircuito Magazine Volume 6Bruno SilvaAinda não há avaliações

- Projeto 7Documento29 páginasProjeto 7Bruno SilvaAinda não há avaliações

- MCBMini V4.4 Manual PDFDocumento19 páginasMCBMini V4.4 Manual PDFBruno SilvaAinda não há avaliações

- Apostila MatLabDocumento29 páginasApostila MatLabGuilherme GoraiebAinda não há avaliações

- MIFalcão MatLab 2001 PDFDocumento71 páginasMIFalcão MatLab 2001 PDFBruno SilvaAinda não há avaliações

- 13a Aula PDFDocumento21 páginas13a Aula PDFBruno SilvaAinda não há avaliações

- Trabalho para Apresentação PDFDocumento1 páginaTrabalho para Apresentação PDFBruno SilvaAinda não há avaliações

- Power Reduction of A CMOS High Speed PDFDocumento70 páginasPower Reduction of A CMOS High Speed PDFBruno SilvaAinda não há avaliações

- 12a Aula PDFDocumento21 páginas12a Aula PDFBruno SilvaAinda não há avaliações

- 3a Prova2008 PDFDocumento1 página3a Prova2008 PDFBruno SilvaAinda não há avaliações

- 3a Aula PDFDocumento17 páginas3a Aula PDFBruno SilvaAinda não há avaliações

- 8a Aula PDFDocumento21 páginas8a Aula PDFBruno SilvaAinda não há avaliações

- 11a AulaDocumento10 páginas11a AulaElias GemisseAinda não há avaliações

- Manual McLab2 (16F877A) Rev 07Documento23 páginasManual McLab2 (16F877A) Rev 07Sidney HenriqueAinda não há avaliações

- MD Comin 2012 2 02 PDFDocumento57 páginasMD Comin 2012 2 02 PDFBruno SilvaAinda não há avaliações

- Norma Escrita v2011Documento27 páginasNorma Escrita v2011Bruno SilvaAinda não há avaliações

- Matlab 1 PDFDocumento1 páginaMatlab 1 PDFMiguel LoderoAinda não há avaliações

- Emicro Doc PDFDocumento52 páginasEmicro Doc PDFBruno SilvaAinda não há avaliações

- Estruturas Cmos Programáveis para Aplicação em Eletrônica PDFDocumento136 páginasEstruturas Cmos Programáveis para Aplicação em Eletrônica PDFBruno SilvaAinda não há avaliações

- Matlab 1 PDFDocumento1 páginaMatlab 1 PDFMiguel LoderoAinda não há avaliações

- Apostila Completa de Eletronica Digital.Documento49 páginasApostila Completa de Eletronica Digital.assuncao_t9375Ainda não há avaliações

- 3 - 2 Transporte 2010 PDFDocumento43 páginas3 - 2 Transporte 2010 PDFBruno SilvaAinda não há avaliações

- Quadro Eléctrico de Habitação PDFDocumento15 páginasQuadro Eléctrico de Habitação PDFBruno SilvaAinda não há avaliações

- Silva Eduardo Silvester de Carvalho PDFDocumento62 páginasSilva Eduardo Silvester de Carvalho PDFBruno SilvaAinda não há avaliações

- Livro Eletrônico (TCC)Documento74 páginasLivro Eletrônico (TCC)Vanessa S. Cavalcante100% (2)

- DISPOSITIVOS DE COMANDO - PPSXDocumento26 páginasDISPOSITIVOS DE COMANDO - PPSXBruno SilvaAinda não há avaliações

- Avaliacao Rui Vaz PDFDocumento11 páginasAvaliacao Rui Vaz PDFBruno SilvaAinda não há avaliações

- Dissertacao - Células de Referência de Tensão CMOS Com Compensacao PDFDocumento86 páginasDissertacao - Células de Referência de Tensão CMOS Com Compensacao PDFBruno SilvaAinda não há avaliações

- Lista 2 - MicrocontroladoresDocumento4 páginasLista 2 - MicrocontroladoresGilberto JuniorAinda não há avaliações

- Relatório 6Documento9 páginasRelatório 6lucianoAinda não há avaliações

- Logica Programavel PDFDocumento43 páginasLogica Programavel PDFLucilia Dos SantosAinda não há avaliações

- Memórias ROM RAMDocumento22 páginasMemórias ROM RAMJoao HomeroAinda não há avaliações

- Tutorial) Saber Eletronica - Mini Curso de Micro Control Ad or (8051)Documento20 páginasTutorial) Saber Eletronica - Mini Curso de Micro Control Ad or (8051)api-3702256Ainda não há avaliações

- Circuitos CombinacionaisDocumento17 páginasCircuitos CombinacionaisDiógenes Muller PereiraAinda não há avaliações

- Momento03 - Relatório - Prática Laboratorial Sistemas Digitais - 919021-6Documento6 páginasMomento03 - Relatório - Prática Laboratorial Sistemas Digitais - 919021-6Marcio Jose SoutoAinda não há avaliações

- 2 Elementos de Logica Sequencial Rev2013Documento23 páginas2 Elementos de Logica Sequencial Rev2013Joao LuisAinda não há avaliações

- Manipulação de Timers No PIC18F4520Documento13 páginasManipulação de Timers No PIC18F4520Ilton Luiz Barbacena100% (1)

- Sistemas - Digitaisaula4Documento21 páginasSistemas - Digitaisaula4Renato TaveiraAinda não há avaliações

- 022-Schimit Triger - Gerador de ClockDocumento2 páginas022-Schimit Triger - Gerador de ClockXP CAinda não há avaliações

- Memória RAM 1 - Frequências, Tensões, Latências e SiglasDocumento2 páginasMemória RAM 1 - Frequências, Tensões, Latências e SiglasJonathan LimaAinda não há avaliações

- Eletrônica Digital - Apostila MemóriasDocumento16 páginasEletrônica Digital - Apostila MemóriasDon SmithAinda não há avaliações

- Aula 3 - Registos, Memórias e DLPDocumento78 páginasAula 3 - Registos, Memórias e DLPAnisio André Carlos ManhiçaAinda não há avaliações

- 2.2 Dispositivos Lógicos ProgramáveisDocumento25 páginas2.2 Dispositivos Lógicos ProgramáveisThiago Azevedo0% (1)

- Apostila Do Placa Mãe NotebookDocumento4 páginasApostila Do Placa Mãe Notebooksand25Ainda não há avaliações

- Flip-Flops e Registradores de DeslocamentoDocumento28 páginasFlip-Flops e Registradores de DeslocamentoAugusto Rodrigues0% (1)

- UFU - Eletrônica DigitalDocumento4 páginasUFU - Eletrônica DigitallordtalgAinda não há avaliações

- Aula HardwareDocumento11 páginasAula HardwarecarlosgasparAinda não há avaliações

- 03 - Módulos Sequenciais 2Documento27 páginas03 - Módulos Sequenciais 2Vicente NascimentoAinda não há avaliações

- Curso Básico de Eletrônica Digital Parte 10Documento8 páginasCurso Básico de Eletrônica Digital Parte 10Thiago_jry100% (2)

- Mux Demux 4canaisDocumento4 páginasMux Demux 4canaisJoaquim TomazAinda não há avaliações

- Programar Microcontroladores PIC16F62XDocumento21 páginasProgramar Microcontroladores PIC16F62XTiago Caetano50% (2)

- Chip 8255 - PPIDocumento11 páginasChip 8255 - PPIPedro Henrique Rocha SousaAinda não há avaliações

- 04 ProcessadorDocumento122 páginas04 ProcessadorRamon NepomucenoAinda não há avaliações

- Circuitos Logicos CombinacionaisDocumento184 páginasCircuitos Logicos CombinacionaisVagner VieiraAinda não há avaliações

- Plano de Ensino Eletrônica Digital 243 SDocumento3 páginasPlano de Ensino Eletrônica Digital 243 SNigger boyAinda não há avaliações

- Apostila SIMATIC 1 - Instruções de Temporizadores e ContadoresDocumento6 páginasApostila SIMATIC 1 - Instruções de Temporizadores e ContadoresThiago GabanAinda não há avaliações