Escolar Documentos

Profissional Documentos

Cultura Documentos

Diagrama em Blocos - Datapath - Controle - Alunos

Enviado por

Denilson catxiTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Diagrama em Blocos - Datapath - Controle - Alunos

Enviado por

Denilson catxiDireitos autorais:

Formatos disponíveis

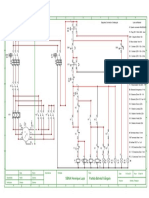

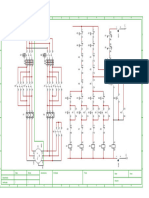

DATAPATH

Sim_2Hz & Sim_2Hz & Sim_2Hz & … & Sim_2Hz Pisca

E5

16 16

E4

CLK_1Hz Termo

R1 Set (+99)

DECODER_TERMOMETRICO

-1 8 E E6

R1

0

16

MUX

8 LOAD(STEP) Set (+15)

2:1

Termo(15..0)

0

Penalty

0

MUX

MUX

Counter_time* E5 E

2:1

2:1

8 8 Counter_round LEDR(15..0)

0 8 (+STEP) 16

1

(-1) Pisca 16

Control E5 CLK

tc < 1 tc=0

CLK 8 8

DecBCD Y T_BCD(7.. 4) dec7seg

end_game T_BCD 4

T_out 4 7

E1 end_round

E5

R HEX7

Div_Freq**

R1

R T_BCD(3.. 0)

E5 dec7seg

E3 E 4 7

CLK CLK_1Hz

Counter_seq

SW(7.. 0) Sim_2Hz (+1) HEX6

CLK_1Hz

8 tc=4

3 “1111111”

end_sequence X

7

HEX5

00

-2 Alpha(3)

8 Penalty “00000000”

01

0

MUX

-4

MUX

2:1

4:1

8

8 8

10

-6 “00” & X & “000”

1

“1111111”

8 8 7

-8 +

11

Alpha(2)

8 “0000” & Beta HEX4

“00000000”

0

MUX

8 8

2:1

SEL “000” & X & “00” Seq Seq_BCD

1 8

SW(1.. 0) 8 + + DecBCD “1111111”

R1 2 2 Alpha(1) 8 8

R 8 7

“00000000” HEX3

0

E1

MUX

E

8

2:1

REG “0000” & X & “0” 8

1

8 “1111111”

+

CLK Alpha(0) 7

8

“00000000”

0

HEX2

MUX

8 E1

2:1

SW(7.. 0) & Seq_BCD 7 7

“00000” & X 8 “1111” dec7seg

1

Play

1 0

MUX

2:1

7

0

16 8 L 7

16

MUX

R1

2:1

R

Alpha Seq_BCD(3.. 0) dec7seg 7

1 0

MUX

7

2:1

4 7

1

E4 E

SW(7.. 0) SW(3.. 0) dec7seg 7 HEX1

REG 8 8 7 7 E4

R1 R Beta

7 7 E1

CLK 4 “1111”

E2 E dec7seg

1 0

MUX

2:1

7 7

0

7

MUX

8 REG “00” & SEL(1.. 0) dec7seg

2:1

Play(7.. 0) Seq_BCD(3.. 0) 7

1 0

MUX

COMPARA dec7seg

2:1

8 Control 7

1

DOR = CLK 7

Play(15.. 8) SW(3.. 0) dec7seg 7

8 7

7 E4 E3 HEX0

CLK

E1 E2 E3 E4 E5 E6 end_game end_sequence end_round

R1

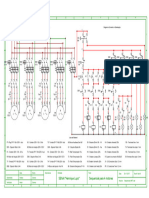

CONTROLE

BTN(1)

KEY(1) enter

Button

KEY(0) sync BTN(0)

CLK reset

CLK

* No código do counter_time, é necessário declarar a biblioteca IEEE.std_logic_signed.all para o correto cálculo do end_time. Após end_time for

ativado, o contador deve ficar fixado em "0000" até ser setado pelo estado Init.

** Foram fornecidos tanto o divisor de frequência para uso com o emulador online quanto para a placa DE2. Lab4 Lab5 Lab6 Lab7 Dado

Você também pode gostar

- Apresentando No Display Tm1638 A Medição De Barômetro Programado No ArduinoNo EverandApresentando No Display Tm1638 A Medição De Barômetro Programado No ArduinoAinda não há avaliações

- Efesto ND3Documento5 páginasEfesto ND3Filippe HenriqueAinda não há avaliações

- FichaT20-SalgueiroDeArton Otimizada v2.1 PCDocumento5 páginasFichaT20-SalgueiroDeArton Otimizada v2.1 PChiukoarosAinda não há avaliações

- Herbert MiragemDocumento5 páginasHerbert MiragemicarussalazarAinda não há avaliações

- RaioX3EdioV 04Documento328 páginasRaioX3EdioV 04Iluminati Oliveira100% (1)

- Pilares - A1Documento1 páginaPilares - A1Lorena CostaAinda não há avaliações

- Itu 04 - Painel de Ti - R0Documento1 páginaItu 04 - Painel de Ti - R0bruno vichinheskiAinda não há avaliações

- Gal Gal ND3Documento5 páginasGal Gal ND3Infamous GamerAinda não há avaliações

- Diagrama Elevador 2 Paradas PDFDocumento1 páginaDiagrama Elevador 2 Paradas PDFINTERFONE SEM FIO100% (1)

- May Bom Luan PhienDocumento1 páginaMay Bom Luan Phiennvnhat10102003Ainda não há avaliações

- Reika KitsuneDocumento5 páginasReika KitsuneDaniel RibeiroAinda não há avaliações

- 7 459 114 00 Eixo Base PunçãoDocumento1 página7 459 114 00 Eixo Base Punçãoluiz carlosAinda não há avaliações

- Trabalho Do 1 Bimestre - Vibrações Mecânicas: Fabio Correia Do Rosario 1-2112576 1-1920229Documento6 páginasTrabalho Do 1 Bimestre - Vibrações Mecânicas: Fabio Correia Do Rosario 1-2112576 1-1920229Fabio RosarioAinda não há avaliações

- PC8Documento1 páginaPC8thiagopdecastroAinda não há avaliações

- 17 11 07 Reversão Estrela Triangulo MITDocumento1 página17 11 07 Reversão Estrela Triangulo MITMELENAAinda não há avaliações

- GokashiraDocumento5 páginasGokashiraDaniel RibeiroAinda não há avaliações

- Compress Senai5 CadDocumento1 páginaCompress Senai5 CadPaulla25 MoraesAinda não há avaliações

- COMPRESSOR MESTRE E ESCRAVO - CadDocumento1 páginaCOMPRESSOR MESTRE E ESCRAVO - CadmarcoalmarAinda não há avaliações

- 17 11 06 Partida Estrela Triangulo MITDocumento1 página17 11 06 Partida Estrela Triangulo MITLUCAS DE SOUZA OLIVEIRAAinda não há avaliações

- RaioX3EdioV 04Documento328 páginasRaioX3EdioV 04isareira45Ainda não há avaliações

- ReikaDocumento5 páginasReikaDaniel RibeiroAinda não há avaliações

- Ficha Do ApheliosDocumento5 páginasFicha Do ApheliosInfamous GamerAinda não há avaliações

- CibeleDocumento2 páginasCibeleErik MichelAinda não há avaliações

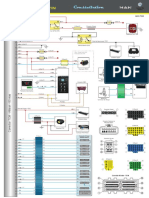

- Peugeot 408 2012 - Transmissão Controle Caixa de Velocidades Automática - Diagrama Elétrico PDFDocumento1 páginaPeugeot 408 2012 - Transmissão Controle Caixa de Velocidades Automática - Diagrama Elétrico PDFWiterMarcosAinda não há avaliações

- Krusk SalgueiroDocumento5 páginasKrusk SalgueiroInfamous GamerAinda não há avaliações

- Motor Partida Estrela-TriânguloDocumento1 páginaMotor Partida Estrela-TriânguloKelson Victor100% (2)

- Exercicios Contatos e Bobinas 1 2 3Documento1 páginaExercicios Contatos e Bobinas 1 2 3Jhosymar CastrejonAinda não há avaliações

- RaioX3EdioV 01Documento327 páginasRaioX3EdioV 01gilson costa100% (1)

- ORÇAMENTO MoveisDocumento1 páginaORÇAMENTO MoveispraiaclubecampeaoAinda não há avaliações

- 2570KF-T-50353 - FL0006 - ISOMÉTRICOS DE TUBULAÇÃO - 2570KF-EID-12-C1A-241-NI-ModelDocumento1 página2570KF-T-50353 - FL0006 - ISOMÉTRICOS DE TUBULAÇÃO - 2570KF-EID-12-C1A-241-NI-ModelevangelistapachecoAinda não há avaliações

- ESPERAS PASSAGEM TUBULAÇÃO 2-Layout1Documento1 páginaESPERAS PASSAGEM TUBULAÇÃO 2-Layout1Nícolas MarquesAinda não há avaliações

- 17 - 11 - 04 Reversão - Motor - TrifásicoDocumento1 página17 - 11 - 04 Reversão - Motor - TrifásicoRonaldo LamahAinda não há avaliações

- Grafcet OficialDocumento1 páginaGrafcet OficialMiguel Angel Fernández EquizaAinda não há avaliações

- Caldeira AutomaticaDocumento1 páginaCaldeira Automaticaivaldo2502Ainda não há avaliações

- Vex - ph.Video.130.Rev.0 (TV Ph32e32d)Documento17 páginasVex - ph.Video.130.Rev.0 (TV Ph32e32d)Marcos KettlAinda não há avaliações

- Compressor Mestre e EscravoDocumento1 páginaCompressor Mestre e EscravoContreras Galarza DiegoAinda não há avaliações

- 11-13 EstruturalDocumento1 página11-13 EstruturalRoberto GamaAinda não há avaliações

- RaioX3EdioV 04Documento328 páginasRaioX3EdioV 04Sonea Lisboa meloAinda não há avaliações

- MAN T263 - Diagrama Eletrônico Da TCM ALLISONDocumento1 páginaMAN T263 - Diagrama Eletrônico Da TCM ALLISONFabricioAinda não há avaliações

- Arduino-On Off HisteresisDocumento1 páginaArduino-On Off HisteresisJessikBorjaAinda não há avaliações

- (Simplificado) AO ÚNICO - Corinho - FingerstyleDocumento3 páginas(Simplificado) AO ÚNICO - Corinho - FingerstyleFernandes SalesAinda não há avaliações

- Turck 501Documento1 páginaTurck 501odlanramallardAinda não há avaliações

- D6 PDFDocumento1 páginaD6 PDFfabio capellinAinda não há avaliações

- CA 2024 Manual FS ALUMINIO r07Documento3 páginasCA 2024 Manual FS ALUMINIO r07Thiago OstanAinda não há avaliações

- FichaT20-SalgueiroDeArton Otimizada v2.1 PCDocumento5 páginasFichaT20-SalgueiroDeArton Otimizada v2.1 PCKauã AlvesAinda não há avaliações

- Autodesk Robot Structural Analysis Professional 2019Documento2 páginasAutodesk Robot Structural Analysis Professional 2019Ericson Mantrujar MequeAinda não há avaliações

- Metalplan RP 25 HP 380VDocumento1 páginaMetalplan RP 25 HP 380VEletrica Artpress Compressores50% (2)

- PROJETO METALICA A1 AssDocumento1 páginaPROJETO METALICA A1 AssGeorgenes SantosAinda não há avaliações

- PROJETO Layout1Documento1 páginaPROJETO Layout1Eurico RochaAinda não há avaliações

- Diagrama Modulo PTMDocumento1 páginaDiagrama Modulo PTMNereu Oliveira100% (2)

- 715G5804 P01 W20 001m+aocDocumento2 páginas715G5804 P01 W20 001m+aocjamilAinda não há avaliações

- GURPS 3rd Character Sheet FF Reader ExtendedDocumento2 páginasGURPS 3rd Character Sheet FF Reader ExtendedKijimoshi SamaAinda não há avaliações

- Conj Arrast Imã H 20 Golden Class: MáquinasDocumento1 páginaConj Arrast Imã H 20 Golden Class: MáquinasManoel CavalcanteAinda não há avaliações

- Philco PTV32C30D LED BIVDocumento9 páginasPhilco PTV32C30D LED BIVafonso juniorAinda não há avaliações

- Captura de Tela 2023-04-25 À(s) 07.18.34Documento10 páginasCaptura de Tela 2023-04-25 À(s) 07.18.34willianbmAinda não há avaliações

- Suspensao Boogie 2 Eixos Sem EstabelizadorDocumento1 páginaSuspensao Boogie 2 Eixos Sem EstabelizadorCassiano SilvaAinda não há avaliações

- 13 DiagramaDocumento3 páginas13 DiagramaKleber AugustoAinda não há avaliações

- 17 - 11 - 11 Partida - Sequencial - 4MITDocumento1 página17 - 11 - 11 Partida - Sequencial - 4MITDiorgenes Reis GomesAinda não há avaliações

- PARTIDA DAHLANDER REVERSAO BOTAO - Rev1Documento1 páginaPARTIDA DAHLANDER REVERSAO BOTAO - Rev1Leonardo CiossaniAinda não há avaliações

- Declaracao Negativa Jeremias AssinadoDocumento1 páginaDeclaracao Negativa Jeremias AssinadoDenilson catxiAinda não há avaliações

- Para JoelmaIDocumento63 páginasPara JoelmaIAnonymous PUw3YtJAinda não há avaliações

- OrganizedDocumento32 páginasOrganizedDenilson catxiAinda não há avaliações

- OrganizedDocumento32 páginasOrganizedDenilson catxiAinda não há avaliações

- Projeto EEL5105 2023 - 2Documento1 páginaProjeto EEL5105 2023 - 2Denilson catxiAinda não há avaliações

- AULA7 Prep Mini SolDocumento2 páginasAULA7 Prep Mini SolDenilson catxiAinda não há avaliações

- Edital de Resultados Aux Moradia - 2023.1 AssinadoDocumento13 páginasEdital de Resultados Aux Moradia - 2023.1 AssinadoDenilson catxiAinda não há avaliações

- O Erotismo Na Escrita de Expressao FeminDocumento39 páginasO Erotismo Na Escrita de Expressao FeminDenilson catxiAinda não há avaliações

- Comprovativo 47846103Documento1 páginaComprovativo 47846103Denilson catxiAinda não há avaliações

- SEI - UNILAB - 0604925 - Declaração - Denilson - Calculo IIDocumento6 páginasSEI - UNILAB - 0604925 - Declaração - Denilson - Calculo IIDenilson catxiAinda não há avaliações

- Renovacao de Visto Temporario de Estudante Unilab ProinterDocumento1 páginaRenovacao de Visto Temporario de Estudante Unilab ProinterDenilson catxiAinda não há avaliações

- Horarios Monitoria MTM 2023 1Documento13 páginasHorarios Monitoria MTM 2023 1Denilson catxiAinda não há avaliações

- Garry Kasparov - Biografia - WikipediaDocumento8 páginasGarry Kasparov - Biografia - WikipediasjeovaniAinda não há avaliações

- Tabela Cores HexaDocumento3 páginasTabela Cores HexaGallo InsanoAinda não há avaliações

- Peões Mágicos - The Final Countdown - (Traduzido) - Herman Van Riemsdijk & Willem HajeniusDocumento130 páginasPeões Mágicos - The Final Countdown - (Traduzido) - Herman Van Riemsdijk & Willem HajeniusLucasNasyn100% (4)

- GMG 00000 000 70310 P 0Documento4 páginasGMG 00000 000 70310 P 0Michelle Lima da CostaAinda não há avaliações

- Ataque Marshall Modernizido - Milos Pavlovic - (PT)Documento412 páginasAtaque Marshall Modernizido - Milos Pavlovic - (PT)Karl Heins Ewald100% (1)

- Xadrez Básico - Dr. Orfeu Gilberto D Agostini - ÍNDICE NOMINALDocumento4 páginasXadrez Básico - Dr. Orfeu Gilberto D Agostini - ÍNDICE NOMINALLucasNasynAinda não há avaliações

- Xeque Mate Apostila XadrezDocumento15 páginasXeque Mate Apostila XadrezHerberth Dos Santos Silva100% (1)

- Como Jogar Bem Xadrez (Barden)Documento162 páginasComo Jogar Bem Xadrez (Barden)carlos trentin100% (1)

- Currículo Do XadrezDocumento6 páginasCurrículo Do XadrezJoao CálixAinda não há avaliações

- Partidas de MestresDocumento39 páginasPartidas de Mestreswilson.junior870Ainda não há avaliações

- UM CADERNO PESSOAL DE PARTIDAS DE XADREZ (Jorge Prata)Documento214 páginasUM CADERNO PESSOAL DE PARTIDAS DE XADREZ (Jorge Prata)Isaac FreitasAinda não há avaliações

- Torneio de Xadrez de NatalDocumento2 páginasTorneio de Xadrez de NatalAgrupamento de Escolas da Lajeosa do Dão100% (1)

- Revista Xadrez 2013Documento40 páginasRevista Xadrez 2013lucioAinda não há avaliações

- Trabalho Educação Fisica - XadrezDocumento6 páginasTrabalho Educação Fisica - XadrezRenato Augusto NeumannAinda não há avaliações

- XADREZ - 45 Dicas Úteis (Por Gilberto Milos JR.)Documento6 páginasXADREZ - 45 Dicas Úteis (Por Gilberto Milos JR.)Juliano Filho100% (1)

- Apostila - Aula 15Documento8 páginasApostila - Aula 15jv774773Ainda não há avaliações

- Xadrez - Programação Anual em 4 NiveisDocumento12 páginasXadrez - Programação Anual em 4 NiveisDharmaJuniorJuniorAinda não há avaliações

- Entrevista Com Cesar UmetsuboDocumento3 páginasEntrevista Com Cesar UmetsuboAugusto Meirelles Reis FilhoAinda não há avaliações

- Dvoretsky - S Endgame Manual 1 170Documento170 páginasDvoretsky - S Endgame Manual 1 170Henrique PedrosaAinda não há avaliações

- Apostila de Xadrez BásicoDocumento24 páginasApostila de Xadrez BásicoRafaella Viana100% (6)

- Vishy - CarlsenDocumento4 páginasVishy - CarlsenAnna Chandra Felício TeixeiraAinda não há avaliações

- Yusupov 2 TraduçaoDocumento223 páginasYusupov 2 TraduçaoLucas LiraAinda não há avaliações

- Defesa PhilidorDocumento4 páginasDefesa Philidormarcos monteiroAinda não há avaliações

- Mate Com PromoçãoDocumento6 páginasMate Com PromoçãoSheridan RibeiroAinda não há avaliações

- 1600 X WagnerDocumento2 páginas1600 X Wagnerfer_2880Ainda não há avaliações

- Plano de Aula 2 Ano Novo - 05-11 1Documento2 páginasPlano de Aula 2 Ano Novo - 05-11 1Gustavo JardimAinda não há avaliações

- Apostila de Xadrez - AvançadoDocumento273 páginasApostila de Xadrez - AvançadoEdCle91% (11)

- Posições Das Notas No ViolãoDocumento1 páginaPosições Das Notas No ViolãoAlissonCleberPintodosSantosAinda não há avaliações

- Jadwal Praktikum Safety - P3TIK Angkatan XXV - 2023Documento1 páginaJadwal Praktikum Safety - P3TIK Angkatan XXV - 2023Dewi RahhAinda não há avaliações

- Xadrez - Partida Analisada - SPASSKY X FISCHER - Match 1972 - Ultima Partida - Defesa Siciliana PaulsenDocumento3 páginasXadrez - Partida Analisada - SPASSKY X FISCHER - Match 1972 - Ultima Partida - Defesa Siciliana PaulsenRoberto Basílio LealAinda não há avaliações