Escolar Documentos

Profissional Documentos

Cultura Documentos

Portas Logicas Uberlandia

Portas Logicas Uberlandia

Enviado por

Fabrizio LutianeDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Portas Logicas Uberlandia

Portas Logicas Uberlandia

Enviado por

Fabrizio LutianeDireitos autorais:

Formatos disponíveis

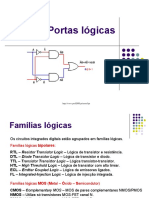

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

CAPTULO II

Funes e Portas Lgicas

2.1 Introduo

Em 1854 o matemtico ingls George Boole apresentou um sistema matemtico de anlise lgica conhecido como lgebra de Boole. Somente em 1938, um engenheiro americano utilizou as teorias da lgebra de Boole para a soluo de problemas de circuitos de telefonia com rels, tendo publicado um artigo que praticamente introduziu na rea tecnolgica o campo da eletrnica digital. Os sistemas digitais so formados por circuitos lgicos denominados de portas lgicas que, utilizados de forma conveniente, podem implementar todas as expresses geradas pela lgebra de Boole. Existem trs portas bsicas (E, OU e NO) que podem ser conectadas de vrias maneiras, formando sistemas que vo de simples relgios digitais aos computadores de grande porte.

17

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.2 Funo E ou AND

A funo E aquela que executa a multiplicao de duas ou mais variveis booleanas. Sua representao algbrica para duas variveis S=A.B, onde se l: S=A e B. Para compreender a funo E da lgebra Booleana, deve-se analisar o circuito da Fig. 2.1, para o qual se adota as seguintes convenes: chave aberta=0, chave fechada=1, lmpada apagada=0 e lmpada acesa=1.

CH A

CH B

Figura 2.1 Circuito representativo da funo E. A anlise da Fig. 2.1 revela que a lmpada somente acender se ambas as chaves estiverem fechadas e, seguindo a conveno, tem-se: CH A=1, CH B=1, resulta em S=1. Pode-se, desta forma, escrever todas as possveis combinaes de operao das chaves na chamada Tabela da Verdade, que definida como um mapa onde se depositam todas as possveis situaes com seus respectivos resultados. O nmero de combinaes possveis igual a 2N, onde N o nmero de variveis de entrada. Tabela da verdade da funo E. A 0 0 1 1 B 0 1 0 1 S 0 0 0 1

A porta lgica E um circuito que executa a funo E da lgebra de Boole, sendo representada, na prtica, atravs do smbolo visto na Fig. 2.2.

A B

Figura 2.2 Porta lgica E. A sada da porta E ser 1, somente se todas as entradas forem 1. 18

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.3 Funo OU ou OR

A funo OU aquela que assume valor 1 quando uma ou mais variveis de entrada forem iguais a 1 e assume 0 se, e somente se, todas as variveis de entrada forem iguais a zero. Sua representao algbrica para duas variveis de entrada S=A+B, onde se l: S=A ou B. Para entender melhor a funo OU da lgebra booleana, analisa-se todas as situaes possveis de operao das chaves do circuito da Fig. 2.3. A conveno a mesma adotada anteriormente: chave aberta=0, chave fechada=1, lmpada apagada=0 e lmpada acesa=1.

CH A

CH B

Figura 2.3 Circuito que representa a funo OU.

O circuito acima mostra que a lmpada acende quando qualquer uma das chaves estiver fechada e permanece apagada se ambas estiverem abertas, ou seja, CH A=0, CH B=0, resulta em S=0. A Fig. 2.4 ilustra a porta lgica que executa a funo OU da lgebra de Boole, juntamente com a sua tabela da verdade.

A B

Porta lgica OU

A 0 0 1 1

B 0 1 0 1

S 0 1 1 1

Tabela da verdade da funo OU

Figura 2.4 Porta lgica e tabela da verdade da funo OU. A sada de uma porta OU ser 1 se uma ou mais entradas forem 1. 19

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.4 Funo NO ou NOT

A funo NO aquela que inverte ou complementa o estado da varivel de entrada, ou seja, se a varivel estiver em 0, a sada vai para 1, e se estiver em 1 a sada vai para 0. representada algebricamente da seguinte forma: ou NO A. A anlise do circuito da Fig. 2.5 ajuda a compreender melhor a funo NO da lgebra Booleana. Ser utilizada a mesma conveno dos casos anteriores. , onde se l: A barra

CH A

Figura 2.5 Circuito representativo da funo NO.

Observando o circuito da Fig. 2.5, pode-se concluir que a lmpada estar acesa somente se a chave estiver aberta (CH A=0, S=1), quando a chave fecha, a corrente desvia por ela e a Lmpada apaga (CH A=1, S=0). O inversor o bloco lgico que executa a funo NO. Sua representao simblica vista na Fig. 2.6, juntamente com sua tabela da verdade.

A 0 1

S 1 0

Porta lgica NO ou inversora

Tabela da verdade da funo NO

Figura 2.6 Porta lgica e tabela da verdade da funo NO.

A sada de uma porta NO assume o nvel lgico 1 somente quando sua entrada 0 e vice-versa.

20

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.5 Funo NO E, NE ou NAND

Esta funo uma composio das funes E e NO, ou seja, a funo E invertida. Sua representao algbrica inverso do produto booleano A.B. O circuito da Fig. 2.7 esclarece o comportamento da funo NE. Observa-se que a lmpada apaga somente quando ambas as chaves so fechadas, ou seja, CH A=1, CH B=1, implica em S=0. , onde o trao indica que ocorrer uma

R CH A

CH B

Figura 2.7 Circuito que representa a funo NE.

A Fig. 2.8 ilustra o circuito que executa a funo NE da lgebra de Boole, juntamente com sua tabela da verdade.

A B A B

Porta lgica NE

A 0 0 1 1

B 0 1 0 1

S 1 1 1 0

Tabela da verdade da funo NE

Figura 2.8 Porta lgica e tabela da verdade da funo NE.

Esta funo o inverso da funo E, ou seja, a sada ser 0 somente quando todas as entradas forem 1.

21

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.6 Funo NO OU, NOU ou NOR

Analogamente a funo NE, a funo NOU a composio da funo OU com a funo NO, ou seja, a funo OU invertida. representada algebricamente da seguinte forma: booleana A+B. Para melhor compreender a funo NOU da lgebra de Boole, pode-se analisar o circuito da Fig. 2.9, onde se observa que a lmpada fica acesa somente quando as duas chaves esto abertas. Assim, CH A=0, CHB=0, resulta em S=1. , onde o trao indica que ocorrer uma inverso da soma

CH A

CH B

Figura 2.9 Circuito que representa a funo NOU.

A Fig. 2.10 ilustra o circuito que executa a funo NOU da lgebra de Boole, e sua tabela da verdade.

A B A B

Porta lgica NOU

A 0 0 1 1

B 0 1 0 1

S 1 0 0 0

Tabela da verdade da funo NOU

Figura 2.10 Porta lgica e tabela da verdade da funo NOU.

Esta funo o inverso da funo OU, ou seja, a sada ser 0 se uma ou mais entradas forem 1.

22

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.7 Funo OU EXCLUSIVO Esta funo, como o prprio nome diz, apresenta sada com valor 1 quando as

variveis de entrada forem diferentes entre si. A notao algbrica que representa a funo OU Exclusivo S=AB, onde se l: A OU Exclusivo B. Para entender melhor a funo OU Exclusivo, analisa-se o circuito da Fig. 2.11. Na condio em que as chaves CH A e CH B esto abertas ( continua apagada quando as chaves CH A e CH B esto fechadas, pois e e esto fechadas), no h caminho para a corrente circular e a lmpada no acende. A lmpada esto abertas interrompendo o fluxo de corrente. Portanto, pode-se concluir que este Bloco s ter nvel 1 na sada (lmpada acesa), quando suas entradas forem diferentes.

CH A CH B

CH A

CH B

Figura 2.11 Circuito que representa a funo OU Exclusivo.

A Fig. 2.12 ilustra o smbolo que representa, na prtica, a funo OU Exclusivo e sua tabela da verdade. A 0 0 1 1 B 0 1 0 1 S 0 1 1 0

A B

Bloco OU Exclusivo

Tabela da verdade da funo OU Exclusivo

Figura 2.12 Bloco lgico e tabela da verdade da funo OU Exclusivo. A Fig. 2.12 simplesmente simboliza o circuito lgico que executa a funo OU Exclusivo. Na verdade, o circuito que efetivamente realiza a funo demonstrada na tabela da verdade acima est ilustrado na Fig. 2.13. 23

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

A B

S=AB = A.B + A. B

S

Figura 2.13 Circuito que executa a funo OU Exclusivo. Observao importante: ao contrrio dos outros blocos lgicos, cada circuito OU EXCLUSIVO admite somente 2 variveis de entrada.

2.8 Funo COINCIDNCIA ou NO OU EXCLUSIVO

Esta funo, como seu prprio nome diz, apresenta sada com valor 1 quando houver uma coincidncia nos valores das variveis de entrada. A notao algbrica que representa a funo Coincidncia S=AuB, onde se l: A Coincidncia B. O circuito da Fig. 2.14 ajuda a compreender a operao da funo Coincidncia. Quando as chaves CH A e CH B esto abertas ( e esto fechadas) circula =1) no corrente pela lmpada e ela estar acesa. Quando CH A=1 e CH B=0 ( CH A=0 (

circula corrente pela lmpada, o que implica em lmpada apagada. Na situao inversa =1) e CH B=1 ocorre a mesma coisa e a lmpada no acender. Com as = = 0) circular corrente duas chaves fechadas, ou seja, CH A = CH B = 1 (

pela lmpada e esta estar acesa. Portanto, pode-se afirmar que a porta Coincidncia ter 1 em sua sada (lmpada acesa), quando as entradas forem idnticas. CH A CH B

CH A

CH B

Figura 2.14 Circuito que executa a funo Coincidncia. 24

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital A Fig. 2.15 ilustra o smbolo que representa, na prtica, a funo Coincidncia e sua tabela da verdade. A 0 0 1 1 B 0 1 0 1 S 1 0 0 1

A B

Bloco Coincidncia

Tabela da verdade da funo Coincidncia

Figura 2.15 Bloco lgico e tabela da verdade da funo Coincidncia.

A Fig. 2.15 simplesmente representa simbolicamente o circuito lgico que executa a funo Coincidncia. Na verdade, o circuito capaz de realizar esta funo ilustrado na Fig. 2.16.

A B

S = AuB = A. B+ A.B

S

Figura 2.16 Circuito que realiza a funo Coincidncia.

Observao importante: Assim como ocorre com o bloco lgico OU EXCLUSIVO, o circuito COINCIDNCIA definido apenas para 2 variveis de entrada.

A seguir, montada uma tabela contendo as cinco funes da lgebra de Boole, ou seja, funes: E, OU, NO, OU Exclusivo e Coincidncia, com seus respectivos smbolos, que representam os circuitos lgicos capazes de executar tais funes. mostrada, tambm, a tabela da verdade, juntamente com uma breve descrio de cada funo e sua respectiva expresso algbrica. 25

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital BLOCOS LGICOS BSICOS PORTA E AND Smbolo Usual Tabela da Verdade Funo Lgica

Funo E: Assume 1 quando todas as variveis forem 1 e 0 nos outros casos.

Expresso

A B

S=A.B

OU OR NO

A B

Funo E: Assume 0 quando todas as variveis forem 0 e 1 nos outros casos. Funo NO: Inverte a varivel aplicada sua entrada.

S=A+B

NOT NE NAND

A B

Funo NE: Inverso da funo E.

NOU NOR

A B

Funo NOU: Inverso da funo OU.

OU Exclusivo

A B

Funo OU Exclusivo: Assume 1 quando S=AB as variveis _ _ assumirem S= A.B + A. B valores diferentes entre si. Funo Coincidncia: Assume 1 quando S=AuB houver _ _ coincidncia entre S= A. B+ A.B os valores das variveis.

Coincidncia

A B

26

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.9 Expresses Booleanas Obtidas de Circuitos Lgicos

Todo o circuito lgico executa uma funo booleana e, por mais complexo que seja, formado pela interligao das portas lgicas bsicas. Assim, pode-se obter a expresso booleana que executada por um circuito lgico qualquer. Para exemplificar, ser obtida a expresso que o circuito da Fig. 2.17 executa.

A B C D

A+B (A+B).(C+D) C+D

Figura 2.17 Circuito lgico.

Para facilitar, analisa-se cada porta lgica separadamente, observando a expresso booleana que cada uma realiza, conforme ilustra o exemplo da Fig. 2.17. O exemplo da Fig. 2.18 visa evidenciar um smbolo de negao muito utilizado e que muitas vezes esquecido e no considerado. Ele pode ser utilizado na sada de uma porta lgica ( ), como na porta NO E abaixo, e na entrada de algumas portas, ). como ser visto mais adiante (

A B C

(A.B) C A.B+C+(C.D)

(C.D)

Figura 2.18 Circuito lgico.

27

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.10 Circuitos Lgicos Obtidas de Expresses Booleanas

Ser visto neste tpico que possvel desenhar um circuito lgico que executa uma funo booleana qualquer, ou seja, pode-se desenhar um circuito a partir de sua expresso caracterstica. O mtodo para a resoluo consiste em se identificar as portas lgicas na expresso e desenh-las com as respectivas ligaes, a partir das variveis de entrada. Deve-se sempre respeitar a hierarquia das funes da aritmtica elementar, ou seja, a soluo inicia-se primeiramente pelos parnteses. Para exemplificar, ser obtido o circuito que executa a expresso S=(A+B).C.(B+D). Para o primeiro parntese tem-se uma soma booleana A+B, logo o circuito que o executa ser uma porta OU. Para o segundo, tem-se outra soma booleana B+D, logo o circuito ser uma porta OU. Posteriormente tem-se a multiplicao booleana de dois parnteses juntamente com a varivel C, sendo o circuito que executa esta multiplicao uma porta E. Para finalizar, unem-se as respectivas ligaes obtendo o circuito completo.

Primeiro Passo

(A+B) A B B D (B+D) S2 S1

Segundo Passo

A B S C D

Terceiro Passo

S1 C S2

28

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.11 Tabelas da Verdade Obtidas de Expresses Booleanas

Uma maneira de se fazer o estudo de uma funo booleana a utilizao da tabela da verdade. Para extrair a tabela da verdade de uma expresso deve-se seguir alguns procedimentos: 1) Montar o quadro de possibilidades; 2) Montar colunas para os vrios membros da equao; 3) Preencher estas colunas com os seus resultados; 4) Montar uma coluna para o resultado final e 5) Preencher esta coluna com os resultados finais. Para exemplificar este processo, utiliza-se a expresso: S = A. B.C + A. D+ A.B.D A expresso contm 4 variveis: A, B, C e D, logo, existem 24=16 possibilidades de combinao de entrada. Desta forma, monta-se o quadro de possibilidades com 4 variveis de entrada, trs colunas auxiliares, sendo uma para cada membro da expresso, e uma coluna para o resultado final.

_ _ _

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Variveis de entrada B C 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1

1 membro D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0

2 membro 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0

3 membro Resultado Final 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 1 0 1 0 0 0 1 0 0 29

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.12 Expresses Booleanas Obtidas de Tabelas da Verdade

Neste item, ser estudada a forma de obter expresses e circuitos a partir de tabelas da verdade, sendo este o caso mais comum de projetos prticos, pois, geralmente, necessita-se representar situaes atravs de tabelas da verdade e a partir destas, obter a expresso booleana e conseqentemente, o circuito lgico. Para demonstrar este procedimento, ser obtida a expresso da seguinte tabela: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 S 0 0 0 1 0 1 1 1

(a) (b) (c) (d)

Na tabela, analisa-se onde S=1 e monta-se a expresso adequada. Em (a), S=1 se S = A . B.C

__ __

Em (b), S=1 se S = A . B .C Em (c), S=1 se S = A . B. C Em (c), S=1 se S = A . B.C

Para se obter a expresso basta realizar a soma booleana de cada termo acima:

__

S = A . B.C+ A. B .C+ A. B. C + A. B.C

Nota-se que o mtodo permite obter, de qualquer tabela, uma expresso padro formada sempre pela soma de produtos. No prximo captulo, relativo a lgebra de Boole, ser estudado o processo de simplificao de expresses booleanas, possibilitando a obteno de circuitos reduzidos.

__

__

__

30

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.13 Equivalncia Entre Blocos Lgicos

As portas lgicas podem ser montadas de forma que possam realizar as mesmas tarefas, ou seja, ter as sadas funcionando de maneira igual a uma outra j conhecida. Estas equivalncias so muito importantes na prtica, ou seja, na montagem de sistemas digitais, pois possibilitam maior otimizao na utilizao dose circuitos integrados comerciais, assegurando principalmente a reduo de componentes e a conseqente minimizao do custo do sistema.

BLOCO LGICO

BLOCO EQUIVALENTE

S = A+B

S=A.B

S = A+B

S=A.B

S=A.B

S = A+B

S=A.B

S = A+B

Todos os Blocos lgicos e expresses podem ser verificadas utilizando-se a tabela da verdade. 31

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital

2.14 Exerccios do Captulo II

2.14.1) Determine as expresses dos circuitos abaixo: a) Circuito 1

A B

C S D

b) Circuito 2

A B C D

c) Circuito 3

A BC D

32

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital d) Circuito 4

A B

C S D

2.14.2) Desenhe o circuito que executa as seguintes expresses:

a) b) c)

S=[(A + B) + (C + D)] . D

S=A . [B . C + A . (C + D) + B . C . D] + B . D S=(A B) . [A . B + (B + D) + C . D + (B . C)] + A . B . C . D

2.14.3) Levante a tabela verdade das seguintes expresses:

a) b)

S = C . [A . B + B . (A + C)]

S=(B + D) . [A + B . (C + D) + A . B . C]

2.14.4) Escreva a expresso caracterstica do circuito abaixo e levante sua respectiva tabela verdade. A B S C D

33

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.5) Determine a expresso booleana a partir das seguintes tabelas: a) Tabela 1 A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 S 1 0 0 1 1 0 0 1

b) Tabela 2 A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 S 0 1 1 0 0 0 0 1 0 1 0 0 1 0 0 1

2.14.6) Desenhe o sinal de sada do circuito abaixo:

A B C

B C

34

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.7) Mostre que o circuito abaixo um OU Exclusivo.

A S B

2.14.8) Mostre que o circuito um circuito Coincidncia.

A S B

2.14.9) Prove que:

(B + C) = A + (B

C)

2.14.10) Levante a tabela da verdade e esquematize o circuito que executa a seguinte expresso:

S={[A . B + C] + [A + B]}

2.14.11) Esquematize o circuito Coincidncia usando apenas porta NOU.

2.14.12) Esquematize o circuito OU Exclusivo, utilizando somente 4 portas NE.

2.14.13) Esquematize o circuito Coincidncia, utilizando apenas 4 portas NOU.

2.14.14) Desenhe o circuito que executa a expresso do exerccio 2.14.2 letra b, usando somente portas NE.

35

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.15) Desenhe o circuito que executa a expresso do exerccio 2.14.2 letra c, usando somente portas NOU.

2.14.16) Levante a tabela da verdade e, a partir desta, desenhe o circuito somente com portas NE.

S=(B + C) . [D + A . C + D . (A + B + C)]

2.14.17) Desenhe novamente o circuito do exerccio 2.14.1, circuito 3, utilizando apenas portas NOU.

Resposta dos exerccios

2.14.1) Determine as expresses dos circuitos abaixo: a) S=[(A + B).(A.C) + (B + D)] b) S=[(B.D + A).(BD + CD)].[C + (A + C).(B.D)] c) S=B + D + C.[(A.C.D) + (A + B + C)] + [(A + B + C).D] d) S=(A.B + A.B + C).(C + D)

2.14.2) Desenhe o circuito que executa as seguintes expresses: a)

A B C D S

36

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital b)

A B C D

C)

A B C D

2.14.3) Levante a tabela verdade das seguintes expresses: a) A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 S 1 0 0 0 0 0 1 0 37

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital b) A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 S 0 0 0 0 0 0 0 0 0 0 0 1 1 0 1 0

2.14.4) Escreva a expresso caracterstica e levante a tabela da verdade.

S=[(A.B) + (C.D)]

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 S 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0

38

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.5) Determine a expresso booleana a partir das seguintes tabelas: a) S = A B C + A BC+ A B C + A BC b) S = A B C D + A B C D + A BC D + A B C D + A B C D + A BC D

__ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __

2.14.6) Desenhe o sinal de sada do circuito abaixo:

A B C S

2.14.7) Mostre que o circuito abaixo um OU Exclusivo. A 0 0 1 1 B 0 1 0 1 S 0 1 1 0

2.14.8) Mostre que o circuito um circuito Coincidncia. A 0 0 1 1 B 0 1 0 1 S 1 0 0 1

39

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.9) Prove A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1

A : ( B C)

1 0 0 1 0 1 1 0

A ( B : C)

1 0 0 1 0 1 1 0

2.14.10) Levante a tabela da verdade e esquematize o circuito A 0 0 0 0 1 1 1 1

ABC

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

S 1 1 0 0 0 0 1 0

2.14.11) Esquematize o circuito Coincidncia usando apenas porta NOU.

A B S

40

UNIVERSIDADE FEDERAL DE UBERLNDIA

FACULDADE DE ENGENHARIA ELTRICA Apostila de Eletrnica Digital 2.14.12) Esquematize o circuito OU Exclusivo, utilizando 4 portas NE.

A S B

2.14.13) Esquematize o circuito Coincidncia, utilizando 4 portas NOU.

A S B

41

Você também pode gostar

- Curso de Programação de CLP, IHM e Supervisório SiemensDocumento67 páginasCurso de Programação de CLP, IHM e Supervisório Siemensandregroth100% (9)

- Aula 6 - Contadores e Temporizadores - Lista de Exercícios PráticosDocumento9 páginasAula 6 - Contadores e Temporizadores - Lista de Exercícios PráticosandregrothAinda não há avaliações

- Super Interessante 295Documento100 páginasSuper Interessante 295John DoeAinda não há avaliações

- Eletronica DigitalDocumento5 páginasEletronica DigitalBruna SantosAinda não há avaliações

- Preenchimento Do Check List para Inspeção de Subestação de Entrada de EnergiaDocumento26 páginasPreenchimento Do Check List para Inspeção de Subestação de Entrada de EnergiaCleitoviski100% (2)

- Portas LogicasDocumento15 páginasPortas LogicasLuis FornazieroAinda não há avaliações

- Aula 5 - Introdução Siemens S7-1200 e TIA Portal - Lista de ExercíciosDocumento6 páginasAula 5 - Introdução Siemens S7-1200 e TIA Portal - Lista de ExercíciosandregrothAinda não há avaliações

- Logica ResolvidaDocumento20 páginasLogica ResolvidaSPI CINTAinda não há avaliações

- 8 Avaliação Cálcio, PTH e Vitamina D Parte 1 - SlideDocumento11 páginas8 Avaliação Cálcio, PTH e Vitamina D Parte 1 - SlidePollyana Furtado JunqueiraAinda não há avaliações

- Istm ExameDocumento14 páginasIstm ExamePedro Rafael Afonso Afonso94% (36)

- Coleção Aplauso - Entrevista Wagner TisoDocumento258 páginasColeção Aplauso - Entrevista Wagner TisoBia Cyrino100% (1)

- Apostila - CLP - Blocos FuncionaisDocumento19 páginasApostila - CLP - Blocos FuncionaisDiego Carvalho100% (1)

- Circuitos Sequencias e CombinatoriosDocumento21 páginasCircuitos Sequencias e CombinatoriosMarcel Miguel0% (1)

- Exercício Extra Funções Da Linguagem Tipo e Gênro Textual 1 1Documento21 páginasExercício Extra Funções Da Linguagem Tipo e Gênro Textual 1 1eunice lazaroAinda não há avaliações

- Aula - Portas LogicasDocumento34 páginasAula - Portas LogicasNeto Pops100% (1)

- Catalogo ElginDocumento6 páginasCatalogo Elgincelso100% (1)

- Portas LogicasDocumento4 páginasPortas LogicasHosana CarolinaAinda não há avaliações

- Exemplo Laudo EletroDocumento7 páginasExemplo Laudo EletroandregrothAinda não há avaliações

- Capítulo2 - Álgebra de Boole - 2020Documento38 páginasCapítulo2 - Álgebra de Boole - 2020Manuel FernandesAinda não há avaliações

- Kpis: Tudo O Que Você Precisa Saber Sobre Os Indicadores de NegócioDocumento26 páginasKpis: Tudo O Que Você Precisa Saber Sobre Os Indicadores de NegócioLetícia - CertisignAinda não há avaliações

- Estudo de Caso - A Logística de Exportação Do Suco de Laranja Na CargillDocumento4 páginasEstudo de Caso - A Logística de Exportação Do Suco de Laranja Na CargillSigmar SabinAinda não há avaliações

- Portas Lógicas PDFDocumento36 páginasPortas Lógicas PDFRogérioPaganiniValentiniAinda não há avaliações

- Funcoes e Portas LogicasDocumento10 páginasFuncoes e Portas LogicasDiego AbreuAinda não há avaliações

- Unidade AlgebraBooleana 1Documento27 páginasUnidade AlgebraBooleana 1sasafdasfgasgAinda não há avaliações

- Portas LogicasDocumento20 páginasPortas LogicasLUIS MARCELO DELFIM (A)Ainda não há avaliações

- ELT 543 T11 - Semana 2 - Apostila - Rev1Documento41 páginasELT 543 T11 - Semana 2 - Apostila - Rev1Valdir MirandaAinda não há avaliações

- 02 - Funões Lógicas PDFDocumento12 páginas02 - Funões Lógicas PDFcefs2011Ainda não há avaliações

- Portas LogicasDocumento22 páginasPortas LogicasspriesAinda não há avaliações

- Aula 1 - Portas LógicasDocumento14 páginasAula 1 - Portas LógicasGabriel GuilhermeAinda não há avaliações

- Aula 02 Funcoes Portas LogicasDocumento25 páginasAula 02 Funcoes Portas LogicasGustavo maciel de souzaAinda não há avaliações

- Portas LógicasDocumento15 páginasPortas LógicasLarissa MoreiraAinda não há avaliações

- Logica DigitalDocumento12 páginasLogica Digitalapi-3721402100% (1)

- 2021 - Aula 2 - Algebra de BooleDocumento30 páginas2021 - Aula 2 - Algebra de BooleJEREMIAS BORGESAinda não há avaliações

- Funções e Variáveis Logicas, Luana Burghausen Rovaris, 4224 2Documento4 páginasFunções e Variáveis Logicas, Luana Burghausen Rovaris, 4224 2Luana RovarisAinda não há avaliações

- Histórico: BooleDocumento103 páginasHistórico: Boolejorginho coelhoAinda não há avaliações

- 3333 20aula04 PortasDocumento11 páginas3333 20aula04 PortasGabriel Barbosa PaganiniAinda não há avaliações

- Aula 5Documento46 páginasAula 5Thiago :3Ainda não há avaliações

- Unidade 3 - Circuitos LógicosDocumento46 páginasUnidade 3 - Circuitos LógicosJunior SacramentoAinda não há avaliações

- Universidade São Tomás de MoçambiqueDocumento9 páginasUniversidade São Tomás de Moçambiquemigueltivane2006Ainda não há avaliações

- Portas Lógicas PrimáriasDocumento7 páginasPortas Lógicas PrimáriasemerdemeloAinda não há avaliações

- Eletrônica Digital Portas Lógicas AND ORDocumento15 páginasEletrônica Digital Portas Lógicas AND ORLuciana Recart CardosoAinda não há avaliações

- Aula 2 Circuitos Digitais IDocumento29 páginasAula 2 Circuitos Digitais IanneAinda não há avaliações

- Caio Aula 01Documento18 páginasCaio Aula 01TayAinda não há avaliações

- 4 - Lógica DigitalDocumento53 páginas4 - Lógica DigitalJefferson PolettoAinda não há avaliações

- Álgebra Booleana e Circuitos LógicosDocumento42 páginasÁlgebra Booleana e Circuitos LógicosNATALY OliveiraAinda não há avaliações

- Eletrônica DigitalDocumento99 páginasEletrônica DigitalLuiz Henrique SaAinda não há avaliações

- A Plica CoesDocumento8 páginasA Plica CoesCompras VariedadesAinda não há avaliações

- Algebra Boleana Lucinete Pereira BSIDocumento3 páginasAlgebra Boleana Lucinete Pereira BSIlucineteAinda não há avaliações

- Capítulo 1 - SISD1 Rev 1-1Documento7 páginasCapítulo 1 - SISD1 Rev 1-1Felipe Cavalcante da SilvaAinda não há avaliações

- Logic GatesDocumento5 páginasLogic Gateskleiton.ferreiraAinda não há avaliações

- 2º Capitulo Funções e Portas Lógicas 2022Documento30 páginas2º Capitulo Funções e Portas Lógicas 2022Maricell Lurana De JesusAinda não há avaliações

- Aula 3 Algebra de BooleDocumento87 páginasAula 3 Algebra de BooleEduardo SantosAinda não há avaliações

- Prática 2Documento7 páginasPrática 2cardosoclara59Ainda não há avaliações

- Álgebra Booleana e Portas LógicasDocumento146 páginasÁlgebra Booleana e Portas LógicasMunir VeteranoAinda não há avaliações

- AULA 06 - Portas Lógicas IIIDocumento19 páginasAULA 06 - Portas Lógicas IIIGilvan VelosoAinda não há avaliações

- Controle LógicoDocumento39 páginasControle LógicoAsdrubolAinda não há avaliações

- Pratica1 - Portas LógicasDocumento12 páginasPratica1 - Portas LógicasBreno RochaAinda não há avaliações

- Álgebra BooleanaDocumento41 páginasÁlgebra Booleanavyctor00Ainda não há avaliações

- Portas LógicasDocumento26 páginasPortas LógicasLeonard LangAinda não há avaliações

- Lógica Digital Algebra BooleanaDocumento83 páginasLógica Digital Algebra BooleanaPhrabul SinghAinda não há avaliações

- Portas Lógicas de Grandes Ultilidades 2024Documento32 páginasPortas Lógicas de Grandes Ultilidades 2024TzeroAinda não há avaliações

- Aula 7 Algebra BooleanaDocumento30 páginasAula 7 Algebra BooleanaJoão Paulo Santiago CavalcanteAinda não há avaliações

- Projetos Em Clp Ladder Baseado No Twidosuite Parte ViiNo EverandProjetos Em Clp Ladder Baseado No Twidosuite Parte ViiAinda não há avaliações

- It - dt.Pdn.03.07.001 - Preenchimento Do Check List para Inspeção de Subestação de Entrada de EnergiaDocumento29 páginasIt - dt.Pdn.03.07.001 - Preenchimento Do Check List para Inspeção de Subestação de Entrada de EnergiaandregrothAinda não há avaliações

- Abnt - NBR 13231 - Prote o Contra Inc Ndio em Subesta Es El TricasDocumento10 páginasAbnt - NBR 13231 - Prote o Contra Inc Ndio em Subesta Es El TricasandregrothAinda não há avaliações

- Pre Aquecimento para Grupo GeradoresDocumento6 páginasPre Aquecimento para Grupo GeradoresandregrothAinda não há avaliações

- Relato de Experiência: Explorando Os Poliedros de Platão Com o Software GeogebraDocumento1 páginaRelato de Experiência: Explorando Os Poliedros de Platão Com o Software GeogebraAna Maria ScalabrinAinda não há avaliações

- Cineminha Do Zengá DRAFTDocumento7 páginasCineminha Do Zengá DRAFTcasamayamona29Ainda não há avaliações

- Ts Compact Dehumidifer FFB Series - En.ptDocumento4 páginasTs Compact Dehumidifer FFB Series - En.ptDaniele DuarteAinda não há avaliações

- Analise de Investimento - T2Documento47 páginasAnalise de Investimento - T2flavia cadijaAinda não há avaliações

- 1643-19 Fibra ÓpticaDocumento3 páginas1643-19 Fibra ÓpticaCarlino JuniorAinda não há avaliações

- O Que É Farmacovigilância - v1 - GráficaDocumento1 páginaO Que É Farmacovigilância - v1 - Gráficasilvia araujoAinda não há avaliações

- Psicologia Comportamental Aula 10 e 11: Tuane - Lima@Documento17 páginasPsicologia Comportamental Aula 10 e 11: Tuane - Lima@Jessica MarcelinoAinda não há avaliações

- Documento de Cobrança: Liquidação Genérica de TributoDocumento1 páginaDocumento de Cobrança: Liquidação Genérica de TributoVictor AlmeidaAinda não há avaliações

- Plano de Ensino Matemática Financeira (Alunos)Documento4 páginasPlano de Ensino Matemática Financeira (Alunos)Raimundo NonatoAinda não há avaliações

- Como Tocar A Flauta Doce - WikiHowDocumento6 páginasComo Tocar A Flauta Doce - WikiHowcamilausagiAinda não há avaliações

- Suporte Básico de Vida - NefroDocumento20 páginasSuporte Básico de Vida - NefroRicardo GonçalvesAinda não há avaliações

- Programa C2 em CombateDocumento63 páginasPrograma C2 em CombateGiovanni SantosAinda não há avaliações

- Antipsicoticos AtipicosDocumento8 páginasAntipsicoticos AtipicosbeasadehAinda não há avaliações

- Portfolio Pratica Pedagogica (Etapa 3)Documento4 páginasPortfolio Pratica Pedagogica (Etapa 3)Amanda R. TillmannAinda não há avaliações

- Atiidade Pratica de BioDocumento4 páginasAtiidade Pratica de BioFzinNAinda não há avaliações

- Ordem de Coleta - Ivanildo Da Silva LimaDocumento3 páginasOrdem de Coleta - Ivanildo Da Silva LimaMarcelo MafAinda não há avaliações

- Danielle - HeroSparkDocumento15 páginasDanielle - HeroSparkmauro correaAinda não há avaliações

- Ficha Tecnica Produto DomissanitarioDocumento2 páginasFicha Tecnica Produto DomissanitarioIsabella Eic VenturaAinda não há avaliações

- 08 30 28 05 MorfologiabacterianaDocumento17 páginas08 30 28 05 MorfologiabacterianaMaciel Martins Da Rrocha Martins da RochaAinda não há avaliações

- A Equipe Audiovisual e Suas AtribuiçõesDocumento12 páginasA Equipe Audiovisual e Suas AtribuiçõesAugusto SantosAinda não há avaliações

- Discurso de Abertura Ano Lectivo 2022 2023Documento2 páginasDiscurso de Abertura Ano Lectivo 2022 2023Henrique Manuel Pedro Milson75% (4)