Escolar Documentos

Profissional Documentos

Cultura Documentos

TESE

Enviado por

Gonçalo RomãoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

TESE

Enviado por

Gonçalo RomãoDireitos autorais:

Formatos disponíveis

Conversor DC-AC de um s andar para sistemas

fotovoltaicos

Andr Filipe Coelho Pinto

Dissertao para obteno do Grau de Mestre em

Engenharia Electrnica

Jri

Presidente: Prof. Moiss Simes Piedade

Orientador: Prof. Maria Beatriz Mendes Batalha Vieira Vieira Borges

Co-orientador: Eng. Hugo Eduardo dos Santos Ribeiro

Vogal: Prof. Snia Maria Nunes dos Santos Paulo Ferreira Pinto

Outubro 2009

Agradecimentos

Agradeo Prof. Beatriz Borges e ao Eng. Hugo Ribeiro por tudo o que me ensinaram e por

todo o apoio durante este projecto. Agradeo a todos os meus colegas de curso, Andreia

Oto pela compreenso nos momentos difceis, ao Daniel Almeida que me aturou durante este

ltimos meses, e aos restantes, Diogo Carvalho, Bruno Gomes, Lus Mendes, Joo Vicente,

Jos Santos, Jos Boavida, Lus Rosado, Ricardo Cunha, Grisha Tulcidas, e Raul Silva.

Agradeo tambm aos novos amigos que fiz na Alameda, Pedro, Leandro, Marco, Mohamed,

Eng. Hugo Marques, e Eng. Rui, por estarem sempre prontos a ajudar. Agradeo tambm ao

Prof. Moiss Piedade e ao Sr. Pina dos Santos por toda a ajuda durante o curso. Agradeo aos

meus pais, Maria Fernanda Pinto, e Daciano Pinto, e a toda a minha famlia por todo o apoio e

fora que sempre me deram. Por fim, agradeo a disponibilizao dos meios por parte do

Instituto de Telecomunicaes para o teste do conversor, e por parte dos laboratrios do

IST-Taguspark para o fabrico da PCB.

Muito obrigado a todos.

I

II

Resumo

A energia fotovoltaica uma fonte de energia renovvel, que tem ganho relevncia nos ltimos

anos, criando a necessidade de se conceberem conversores electrnicos de potncia para

sistemas fotovoltaicos com maior rendimento. Neste trabalho apresentado um conversor

DC-AC que junta um conversor DC-DC e um inversor numa topologia de um s andar. Este

conversor baseia-se num inversor em ponte completa com tenso de sada a trs nveis, ao

qual so adicionados dois dodos e uma bobine para poder formar um conversor Boost. O

funcionamento deste ltimo est dependente do funcionamento do inversor, sendo controlado

nos zeros da tenso de sada do inversor. O conversor de um s andar tem de funcionar em

equilbrio energtico, tentando igualar as potncias na entrada e na sada. O sistema de

controlo deste conversor baseado num controlo histertico da corrente injectada na rede e da

corrente pedida ao painel fotovoltaico, e num controlador que estabiliza a tenso do

condensador do inversor, de modo a manter o conversor em equilbrio energtico. Foi

efectuado um prottipo do conversor, verificando-se o seu funcionamento.

Palavras-chave:

Conversor Electrnico de Potncia, Sistema Fotovoltaico, Conversor DC-AC de um s Andar,

Inversor em Ponte Completa, Conversor Boost, Controlo Histertico.

III

IV

Abstract

Photovoltaic energy is a renewable energy source, which has gained importance in the last

years, creating the need to design power electronic converters for photovoltaic systems with

higher efficiency. This work presents a DC-AC converter that joins a DC-DC converter and an

inverter in a single-stage topology. This converter is based on a full-bridge inverter with three

level output voltage, where two diodes and one inductor have been added in order to create a

Boost converter. The operation of the latter is dependent of the inverter operation, being

controlled in the zeros of inverter output voltage. The single-stage converter has to operate in

energy balance, trying to match the power input and output. The control system of this converter

is based on a hysteretic control of the grid injected current and current required from the

photovoltaic panel, and on a controller that stabilize the capacitor voltage of the inverter, in

order to keep the energy balance in the converter. It was made a prototype of the converter,

verifying its operation.

Keywords:

Power Electronic Converter, Photovoltaic System, Single-Stage DC-AC converter, Full-Bridge

Inverter, Boost Converter, Hysteretic Control.

V

VI

ndice

Agradecimentos.............................................................................................................................. I

Resumo ........................................................................................................................................ III

Abstract ......................................................................................................................................... V

ndice ........................................................................................................................................... VII

Lista de Abreviaturas .................................................................................................................... XI

Lista de Figuras .......................................................................................................................... XIII

Lista de Tabelas ....................................................................................................................... XVII

Captulo 1 - Introduo .................................................................................................................. 1

1.1 Motivao ............................................................................................................................ 1

1.2 Objectivos ............................................................................................................................ 2

1.3 Organizao da Dissertao ............................................................................................... 2

Captulo 2 - Conceitos Tericos e Topologias de Conversores para Sistemas Fotovoltaicos ..... 3

2.1 Introduo ............................................................................................................................ 3

2.2 Elementos Constituintes de um Sistema Fotovoltaico ........................................................ 3

2.3 Classificao das Topologias .............................................................................................. 4

2.3.1 Nmero de andares ...................................................................................................... 4

2.3.2 Transformador .............................................................................................................. 5

2.3.3 Nmero de nveis da tenso de sada do inversor ...................................................... 5

2.4 Topologias Existentes na Literatura .................................................................................... 6

2.5 Concluses .......................................................................................................................... 8

Captulo 3 - Conversor DC-AC de um s Andar para Sistemas Fotovoltaicos ............................. 9

3.1 Introduo ............................................................................................................................ 9

3.2 Topologia ............................................................................................................................. 9

3.2.1 Inversor ....................................................................................................................... 10

3.2.2 Conversor DC-DC ...................................................................................................... 15

3.2.3 Conversor de um s andar ......................................................................................... 18

VII

3.2.4 Dimensionamento ...................................................................................................... 21

3.3 Sistema de Controlo .......................................................................................................... 24

3.3.1 Sistema de controlo das correntes i

LR

e i

LP

................................................................ 25

3.3.2 Sistema de controlo da tenso v

CF

............................................................................. 29

3.4 Concluses ........................................................................................................................ 43

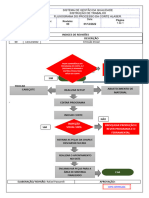

Captulo 4 - Circuito de Controlo e de Potncia Hardware ...................................................... 45

4.1 Introduo .......................................................................................................................... 45

4.2 Circuito de Controlo ........................................................................................................... 45

4.2.1 Circuito de ataque s portas dos transstores ............................................................ 46

4.2.2 Circuito para efectuar o controlo histertico ............................................................... 47

4.2.3 Circuito para efectuar o controlo de v

CF

..................................................................... 51

4.2.4 Circuito de segurana de v

CF

..................................................................................... 54

4.3 Circuito de Potncia .......................................................................................................... 55

4.4 Concluses ........................................................................................................................ 56

Captulo 5 - Simulao e Resultados Experimentais .................................................................. 57

5.1 Introduo .......................................................................................................................... 57

5.2 Resultados da Simulao .................................................................................................. 57

5.2.1 Tempos mortos entre os sinais das portas dos transstores. .................................... 57

5.2.2 Corrente injectada na rede com a tenso v

CF

estabilizada em 500V ........................ 59

5.2.3 Corrente injectada na rede com C

F

a carregar. ......................................................... 60

5.3 Resultados Experimentais ................................................................................................. 63

5.3.1 Tempos mortos entre os sinais das portas dos transstores. .................................... 63

5.3.2 Corrente injectada na rede apenas com o inversor a funcionar. ............................... 64

5.3.3 Corrente injectada na rede com C

F

a carregar. ......................................................... 66

5.3.4 Rendimento do conversor. ......................................................................................... 69

Captulo 6 - Concluses e Trabalho Futuro ................................................................................ 71

6.1 Concluses ........................................................................................................................ 71

6.2 Trabalho Futuro ................................................................................................................. 72

Referncias ................................................................................................................................. 73

Anexo A - Esquema elctrico do circuito de controlo.................................................................. 75

VIII

IX

Anexo B - PCB ............................................................................................................................ 79

Anexo C - Material utilizado e custo ............................................................................................ 81

Anexo D - Dimensionamento de bobines .................................................................................... 83

X

Lista de Abreviaturas

DC Direct current (corrente continua)

AC Alternate current (corrente alternada)

PV Photovoltaics (fotovoltaico)

PCB Printed Circuit Board (placa de circuito impresso)

THD Total Harmonic Distortion (Taxa de distoro harmnica)

XI

XII

Lista de Figuras

Fig. 2.1 Esquema de um sistema fotovoltaico. .......................................................................... 3

Fig. 2.2 Ilustrao da injeco da corrente do conversor DC-AC na rede elctrica. ................. 4

Fig. 2.3 - Sistema fotovoltaico: a) conversor de um s andar, b) conversor de dois andares. ..... 4

Fig. 2.4 Topologias com transformador: a) e b) de alta frequncia, c) frequncia da rede. ... 5

Fig. 2.5 Tenses de sada do conversor DC-AC. (a) Tenso a dois nveis. (b) Tenso a trs

nveis. ............................................................................................................................................ 6

Fig. 2.6 Topologia em ponte completa a dois nveis. ................................................................. 6

Fig. 2.7 Topologia em meia ponte a trs nveis com conversor Boost. ..................................... 7

Fig. 2.8 Topologia de conversor Flyback com conversor DC-AC em ponte. ............................. 7

Fig. 2.9 Topologia Sunny Boy 5000TL. ...................................................................................... 8

Fig. 3.1 Conversor DC-AC de um s andar para sistemas fotovoltaicos................................. 10

Fig. 3.2 Esquema do inversor em ponte completa a vermelho. ............................................... 10

Fig. 3.3 Esquema do circuito no estado s

00

. ............................................................................ 11

Fig. 3.4 Diagramas temporais da tenso de sada do inversor, corrente na bobine e tenso da

rede. ............................................................................................................................................ 12

Fig. 3.5 Esquema do circuito: a) no estado s

10

,b) no estado s

11

. ............................................ 13

Fig. 3.6 Esquema do circuito no estado s

01

. ............................................................................ 14

Fig. 3.7 Esquema do conversor Boost a vermelho. ................................................................. 15

Fig. 3.8 Esquema dos dois conversores Boost formados por esta topologia: a) primeiro

conversor Boost, b) segundo conversor Boost. .......................................................................... 16

Fig. 3.9 Esquema do circuito do conversor Boost com T3 ligado. ........................................... 16

Fig. 3.10 Diagramas temporais da tenso e corrente na bobine L

P

do conversor Boost,

quando est a funcionar no modo de conduo contnua. ......................................................... 17

Fig. 3.11 Esquema do circuito do conversor Boost com T3 desligado. ................................... 17

Fig. 3.12 Topologia equivalente topologia em estudo. ......................................................... 19

Fig. 3.13 Formas de onda da tenso no condensador C

F

e da rede elctrica. ... . 21 ......... ..........

Fig. 3.14 Representao de f

Imax

em funo de V

Rede

(3.53). A vermelho para IRcJc < :CF2, e

a azul para IRcJc > :CF2. ......................................................................................................... 23

XIII

Fig. 3.15 Esquema elctrico do sistema de controlo do conversor. ........................................ 25

Fig. 3.16 Controlo histertico de i

LR

. ........................................................................................ 25

Fig. 3.17 Diagrama temporal do valor Q consoante a corrente i

LR

e a sua referncia. ........... 26

Fig. 3.18 Controlo histertico de i

LP

. ......................................................................................... 26

Fig. 3.19 Diagrama temporal do valor B consoante a corrente i

LP

e a sua referncia. ............ 27

Fig. 3.20 Controlo para obter o ciclo de onda da tenso da rede. ........................................... 27

Fig. 3.21 Mapas de Karnaugh para as funes de T1 e T2. .................................................... 29

Fig. 3.22 Circuito lgico de controlo dos transstores. ............................................................. 29

Fig. 3.23 Esquema elctrico do sistema de controlo da tenso no condensador C

F. w

........... 30

Fig. 3.24 Diagrama de blocos do sistema. ............................................................................... 31

Fig. 3.25 Diagrama de blocos do sistema com controlador proporcional. ............................... 31

Fig. 3.26 Root locus do sistema em cadeia aberta. ................................................................. 32

Fig. 3.27 Resposta no tempo do sistema com controlador proporcional, k=10. ...................... 32

Fig. 3.28 Resposta no tempo do sistema com controlador proporcional, k=40. ...................... 33

Fig. 3.29 Diagrama de blocos do sistema com controlador proporcional, com a perturbao

de 100 Hz. ................................................................................................................................... 33

Fig. 3.30 Resposta no tempo do sistema com controlador proporcional, k=20 e perturbao

de 100 Hz. ................................................................................................................................... 34

Fig. 3.31 Diagrama de bode do sistema em cadeia aberta com controlador proporcional,

k=20. ............................................................................................................................................ 35

Fig. 3.32 Diagrama de blocos do sistema com controlador proporcional e constante de tempo

..................................................................................................................................................... 35

Fig. 3.33 Root locus do sistema em cadeia aberta, com posicionamento do plo a 8Hz. ...... 36

Fig. 3.34 Resposta no tempo do sistema com controlador proporcional e constante de tempo,

k=2,5. ........................................................................................................................................... 37

Fig. 3.35 Resposta no tempo do sistema com controlador proporcional e constante de tempo,

k=15. ............................................................................................................................................ 38

Fig. 3.36 Diagrama de blocos de um controlador proporcional integral. ................................. 39

Fig. 3.37 Diagrama de blocos do sistema com controlador proporcional integral e constante

de tempo. ..................................................................................................................................... 39

Fig. 3.38 Root locus do sistema em cadeia aberta, com o zero posicionado em 10 Hz. ........ 40

Fig. 3.39 Root locus do sistema em cadeia aberta, com o zero posicionado em 3,18 Hz. ..... 40

Fig. 3.40 Root locus do sistema em cadeia aberta, com o zero posicionado em 1,6 Hz. ....... 41

XIV

Fig. 3.41 Root locus do sistema em cadeia aberta, com o zero posicionado em 0,8Hz. ........ 41

Fig. 3.42 Resposta no tempo do sistema com controlador proporcional integral e constante de

tempo. .......................................................................................................................................... 42

Fig. 3.43 Diagrama de bode do sistema em cadeia aberta com controlador proporcional

integral e constante de tempo. .................................................................................................... 43

Fig. 4.1 PCB do circuito de controlo. ........................................................................................ 45

Fig. 4.2 Circuito com atraso de tempo para evitar conduo simultnea dos transstores. .... 46

Fig. 4.3 Circuito equivalente para a situao em que V

I

=15 V. ............................................... 46

Fig. 4.4 Circuito equivalente para a situao em que V

I

=0 V. ................................................. 47

Fig. 4.5 Circuito para retirar uma amostra da corrente i

LR

. ......................................................... 48

Fig. 4.6 Circuito para retirar uma amostra da corrente i

LP

. ...................................................... 48

Fig. 4.7 Circuito para retirar uma amostra da tenso da rede. ................................................ 49

Fig. 4.8 Comparador com histerese no inversor, a) circuito e b) caracterstica. ................... 49

Fig. 4.9 Circuito de condicionamento do sinal de sada dos comparadores. .......................... 50

Fig. 4.10 Circuito para retirar uma amostra da tenso v

CF

....................................................... 51

Fig. 4.11 Circuito do controlador proporcional integral com constante de tempo. ................... 52

Fig. 4.12 Circuito de condicionamento do sinal de sada do controlador. ............................... 53

Fig. 4.13 Circuito para obter a referncia de corrente i

LR

. ....................................................... 54

Fig. 4.14 Circuito de segurana. .............................................................................................. 55

Fig. 4.15 Circuito de potncia. .................................................................................................. 56

Fig. 5.1 Sinais das portas dos transstores: V

oT1

a azul, V

oT3

a vermelho. .............................. 58

Fig. 5.2 Sinais das portas dos transstores: V

oT1

a azul, V

CT1

a verde, V

oT3

a vermelho, e V

cT3

a

roxo. ............................................................................................................................................. 58

Fig. 5.3 Sinal i

LR

a azul, e sinal i

LRref

a vermelho. ..................................................................... 59

Fig. 5.4 Sinal i

LR

a azul, e sinal i

LRref

a vermelho, e sinal v

AB

a roxo. ........................................ 60

Fig. 5.5 Sinal v

CF

a vermelho, e sinal V

CTR

a azul. ................................................................... 61

Fig. 5.6 Sinal i

LR

a azul, sinal i

LRref

a vermelho, e sinal V

Rede

a roxo. ....................................... 62

Fig. 5.7 Sinal v

Painel

a azul, e sinal i

LP

a verde. ......................................................................... 62

Fig. 5.8 Sinais das portas dos transstores: V

oT1

a azul e V

oT3

a vermelho. ............................ 63

Fig. 5.9 Sinais das portas dos transstores: V

oT1

a azul e V

oT3

a vermelho. ........................... 64

Fig. 5.10 Esquema elctrico do circuito para testar o inversor. ............................................... 64

XV

XVI

Fig. 5.11 Sinal i

LR

a azul 500 mA/div, e sinal i

LRref

a vermelho 500 mA/div. ............................. 65

Fig. 5.12 Sinal i

LR

a azul 1 A/div, sinal i

LRref

a vermelho 1 A/div, e sinal v

AB

a roxo 50 V/div. .. 65

Fig. 5.13 Sinal i

LR

a azul 1 A/div, sinal i

LRref

a vermelho 1 A/div, e sinal v

AB

a roxo 50 V/div. .. 66

Fig. 5.14 Esquema elctrico do circuito para testar o conversor. ............................................ 66

Fig. 5.15 Sinal i

LR

a azul 1 A/div, e sinal i

LP

a verde 1 A/div. .................................................... 67

Fig. 5.16 Sinal de tenso na carga a roxo 50 V/div. ................................................................ 68

Fig. 5.17 Sinal i

LR

a azul 1 A/div, e sinal v

CF

a vermelho 100 V/div. ........................................ 68

Fig. 5.18 Grfico do rendimento do conversor em funo da potncia de entrada. ................ 70

Fig. A.1 Circuito de ataque s portas dos transstores. ........................................................... 75

Fig. A.2 Circuito dos comparadores com histerese. ................................................................ 76

Fig. A.3 Circuito do controlador da tenso no condensador e do sistema de segurana. ...... 77

Fig. A.4 Circuito de alimentao e das entradas. .................................................................... 78

Fig. A.5 Circuito de controlo (camada superior). ...................................................................... 79

Fig. A.6 Circuito de controlo (camada inferior). ........................................................................ 80

Lista de Tabelas

Tabela 2.1 Avaliao das cinco topologias de conversores. ..................................................... 8

Tabela 3.1 Estados de funcionamento dos transstores do inversor em ponte completa. ...... 11

Tabela 3.2 Tabela com o dimensionamento da topologia. ...................................................... 24

Tabela 3.3 Nveis lgicos das tenses das portas dos transstores. ....................................... 28

Tabela 3.4 Factor de amortecimento em funo de k. ............................................................ 37

Tabela 3.5 Sobreelevao em funo de k. ............................................................................. 38

Tabela 3.6 Anlise dos parmetros do sistema conforme o posicionamento do zero. ........... 42

Tabela 4.1 - Valores dos parmetros do circuito de ataque s portas dos transstores. ............ 47

Tabela 4.2 Valores dos parmetros para o circuito de controlo histertico. ............................ 51

Tabela 4.3 Valores dos parmetros para o circuito de controlo de v

CF

. .................................. 54

Tabela 4.4 Valores dos parmetros para o circuito de segurana de v

CF

. .............................. 55

Tabela 5.1 Valor da THD da corrente i

LR

e do factor de potncia do conversor. ..................... 69

Tabela 5.2 Resultados dos ensaios para medir o rendimento do conversor. .......................... 69

Tabela A.1 Material utilizado no projecto. ................................................................................ 81

XVII

XVIII

Captulo 1

Introduo

1.1 Motivao

A importncia da energia na vida quotidiana e o aumento do seu consumo, o aumento dos

nveis de poluio, juntamente com a diminuio dos recursos da principal fonte de energia, o

combustvel fssil, tem nos ltimos anos levado a uma orientao para as energias renovveis.

A favor das energias renovveis esto os factos de estas serem inesgotveis na natureza, e

terem um impacto ambiental reduzido, quando comparado com a energia proveniente de

combustveis fosseis. Contudo, existem algumas limitaes, nomeadamente a indisponibilidade

parcial dos recursos, ou seja, por exemplo o vento no constante, a luz solar tem uma

durao limitada e varivel em cada perodo de 24 horas e as ondas do mar tm amplitudes

diferentes.

A energia fotovoltaica uma fonte de energia renovvel, e tem ganho relevncia nos ltimos

anos. A tecnologia fotovoltaica gera uma corrente quando a clula fotovoltaica iluminada por

fotes, contudo esta corrente influenciada pela intensidade luminosa e a temperatura do

ambiente. O rcio preo/rendimento dos sistemas fotovoltaicos actualmente muito elevado,

quando comparado com outras tecnologias de produo de energia elctrica, tendo

rendimentos perto de 6 % [1]. Este valor de rendimento deve-se essencialmente ao rendimento

dos painis fotovoltaicos. Para no diminuir ainda mais o rendimento destes sistemas

necessrio que os conversores que entregam esta energia rede elctrica tenham um elevado

rendimento. Para isso preciso que estes conversores consigam extrair dos painis PV a

mxima potncia, para posteriormente a entregarem rede elctrica.

A tecnologia fotovoltaica fornece uma corrente e uma tenso contnuas, pelo que para ligar

rede elctrica, ou para uso domstico, necessrio um conversor DC-AC, denominado

tambm de inversor, para efectuar a converso das grandezas contnuas para grandezas

alternadas.

1

2

1.2 Objectivos

Pretende-se com esta dissertao desenvolver um controlo para um conversor de um s andar,

que engloba um conversor DC-DC e um conversor DC-AC, para converter energia de um

painel PV para a rede elctrica monofsica. A execuo do trabalho subentende que se analise

o funcionamento do conversor, se efectue a simulao deste com o respectivo controlo, e

posteriormente se desenvolva um prottipo do conversor e do controlo para retirar resultados

experimentais.

1.3 Organizao da Dissertao

Esta dissertao est organizada em seis captulos. O primeiro captulo contm a introduo,

onde se descreve a motivao do trabalho, os objectivos gerais, e a organizao da

dissertao. O segundo captulo descreve conceitos tericos e refere quatro topologias de

conversores para sistemas fotovoltaicos. No terceiro captulo apresenta-se o conversor de um

s andar utilizado no trabalho e efectua-se a sua anlise conducente ao seu dimensionamento.

Neste captulo tambm se explica o controlo que vai ser implementado no conversor proposto.

No quarto captulo apresenta-se o circuito de controlo e o circuito de potncia, e a sua

implementao em hardware. O quinto captulo contm os resultados de simulao e os

resultados obtidos experimentalmente. O sexto e ltimo captulo apresenta as concluses do

trabalho desenvolvido, assim como as perspectivas de trabalho futuro.

Captulo 2

Conceitos Tericos e Topologias de Conversores

para Sistemas Fotovoltaicos.

2.1 Introduo

Neste captulo apresentada uma viso geral sobre conversores para sistemas fotovoltaicos.

Na seco 2.2 so descritos os elementos constituintes de um sistema fotovoltaico. A

classificao das topologias de conversores explicada na seco 2.3. Por fim na seco 2.4

feita uma viso geral sobre quatro topologias de conversores para sistemas fotovoltaicos

existentes na literatura.

2.2 Elementos Constituintes de um Sistema Fotovoltaico

Um sistema fotovoltaico constitudo por um painel fotovoltaico (PV), ou um conjunto de

painis PV, por um conversor DC-AC, denominado tambm de inversor, pelo filtro de sada, e

pela rede elctrica Fig. 2.1.

Fig. 2.1 Esquema de um sistema fotovoltaico.

Na sada do painel colocado um condensador para efectuar o desacoplamento energtico

entre o painel e o inversor. O inversor necessrio para inverter a tenso do painel PV,

convertendo a tenso e corrente continua em grandezas alternadas, para que seja possvel a

sua insero na rede elctrica. Para que o inversor injecte corrente na rede necessrio que a

tenso mdia aos seus terminais seja superior ao valor da tenso da rede elctrica, Fig. 2.2

3

Rede

Tenso

de sada

inversor

L

R

I

Fig. 2.2 Ilustrao da injeco da corrente do conversor DC-AC na rede elctrica.

2.3 Classificao das Topologias

Na literatura existem vrias topologias de conversores para sistemas fotovoltaicos. Estas so

classificadas quanto ao nmero de andares, utilizao, ou no, de transformador, e ao

nmero de nveis da tenso de sada do inversor.

2.3.1 Nmero de andares

As topologias podem ser classificadas quanto ao nmero de andares do conversor. Este pode

ser de um andar Fig. 2.3(a), ou de dois andares Fig. 2.3(b). Se for de dois andares est

implcito a utilizao de um conversor DC-DC e de um inversor. O conversor DC-DC utilizado

em muitas topologias quando se pretende elevar o nvel de tenso que fornecida pelo painel

PV. Este conversor pode ser retirado sempre que no seja necessria esta funo.

Fig. 2.3 - Sistema fotovoltaico: a) conversor de um s andar, b) conversor de dois andares.

4

2.3.2 Transformador

As topologias podem ser classificadas em topologias que utilizam transformador e topologias

sem transformador. As primeiras tm a vantagem de poder amplificar a tenso no secundrio e

possuir isolamento galvnico. Destas topologias, algumas tm transformador inserido no

conversor DC-DC Fig. 2.4 a), outras tm o transformador inserido no inversor Fig. 2.4 b) e

ainda existem topologias que utilizam transformador para fazer a interligao entre o inversor e

a rede elctrica Fig. 2.4 c). Nas duas primeiras topologias utilizado um transformador a

funcionar a alta frequncia. Na terceira topologia utiliza-se o transformador frequncia da

rede (50 Hz), o que faz com que este seja volumoso, caro e tenha mais perdas. Quando o

isolamento galvnico no importante, utilizam-se topologias sem transformador, que

conseguem ter maior rendimento e o seu fabrico torna-se mais econmico.

Fig. 2.4 Topologias com transformador: a) e b) de alta frequncia, c) frequncia da rede.

2.3.3 Nmero de nveis da tenso de sada do inversor

As topologias podem ser classificadas quanto ao nmero de nveis da tenso de sada do

inversor. Esta tenso de sada pode ter apenas dois nveis, Fig. 2.5 a), ou ser uma tenso

multi-nvel, Fig. 2.5 b), quando a tenso de sada tem 3, ou 5, ou 7 nveis. Ao possuir um

maior nmero de nveis a tenso de sada do inversor vai possuir uma distoro harmnica

menor.

5

-:

CF

:

CF

:

t

-:

CF

:

CF

:

t

Fig. 2.5 Tenses de sada do conversor DC-AC. (a) Tenso a dois nveis. (b) Tenso a trs nveis.

2.4 Topologias Existentes na Literatura

A topologia representada na Fig. 2.6 [2], utiliza apenas o inversor em ponte completa, pois a

tenso em C

P

suficientemente elevada para ser possvel injectar corrente na rede. Esta

uma topologia clssica, em que a tenso de sada tem apenas dois nveis. O inconveniente o

facto de ter de utilizar bastantes painis PV para que a tenso do conjunto atinja os 500 V.

Fig. 2.6 Topologia em ponte completa a dois nveis.

A topologia da Fig. 2.7 tem um s andar, inversor em meia ponte a trs nveis [3]. Este tipo de

inversor, com a tenso de sada a trs nveis, tem um valor de distoro harmnica que

metade do valor de distoro harmnica da topologia anterior. As desvantagens deste

conversor so necessitar de mais componentes o que leva a maiores perdas, e a dificuldade de

ter igual valor de tenso nos dois condensadores.

6

Fig. 2.7 Topologia em meia ponte a trs nveis com conversor Boost.

A topologia da Fig. 2.8 tem dois andares, contendo um conversor DC-DC, conversor Flyback, e

um inversor [4]. Esta utiliza um inversor em ponte completa com tenso de sada a trs nveis.

O conversor Flyback utilizado nesta topologia no s para elevar a tenso entrada do

inversor, mas tambm para efectuar o isolamento galvnico. O transformador desta topologia

funciona a alta frequncia.

Fig. 2.8 Topologia de conversor Flyback com conversor DC-AC em ponte.

A topologia da Fig. 2.9, Sunny Boy 5000TL [5], uma topologia que se comercializa. Esta tem

dois andares, o primeiro que inclui trs conversores DC-DC do tipo Boost, cada um para um

vector de painis PV, e no segundo andar tem um inversor em meia ponte com tenso de

sada a dois nveis, que transfere a potncia extrada do trs vectores de painis PV para a

rede elctrica.

7

Fig. 2.9 Topologia Sunny Boy 5000TL.

Na Tabela 2.1 feita uma breve avaliao das topologias atrs referidas, consoante a

classificao de topologias apresentada na seco 2.3, e outras caractersticas.

Tabela 2.1 Avaliao das cinco topologias de conversores.

Fig.

n

Nmero de

andares

Tenso mnima

do(s) PV

Condensador de

desacoplamento

Nmero de nveis

da tenso de sada

do inversor

Isolamento

galvnico

2.6 1 500 V - 2 No

2.7 1 2 x 360 V 2x(640 F a 810 V) 3 No

2.8 2 - 1x(33 F a 400 V) 3 Sim

2.9 2 150 V 2x(1200 F a 375 V) 2 No

2.5 Concluses

Um sistema fotovoltaico constitudo por um, ou mais, painis PV, por um circuito electrnico

de potncia e pela rede elctrica. Neste documento foram apresentadas quatro topologias de

conversores para ligar painis PV rede elctrica. As topologias podem ser divididas

consoante: o nmero de andares, o nmero de nveis da tenso de sada do inversor, e a

utilizao ou no de transformador, podendo este funcionar a alta frequncia ou frequncia

da rede.

8

Captulo 3

Conversor DC-AC de um s Andar para Sistemas

Fotovoltaicos.

3.1 Introduo

Neste captulo apresentada a topologia do conversor que vai ser estudada nesta dissertao,

assim como o controlo que utilizado. Na seco 3.2 apresentada a topologia do conversor e

os seus modos de funcionamento. O sistema de controlo tanto do inversor como do conversor

DC-DC so explicados na seco 3.3.

3.2 Topologia

Esta dissertao baseada numa nova topologia de conversores, para ligao de um vector de

painis PV rede elctrica monofsica, em desenvolvimento pelo grupo Sistemas Energticos

para Telecomunicaes do Instituto de Telecomunicaes - plo de Lisboa. A origem desta

advm de outra topologia desenvolvida pelo mesmo grupo de investigao, que possui num s

andar um conversor Buck-Boost e um inversor [6]. A topologia que se vai estudar contm um

conversor DC-DC do tipo Boost e um inversor em ponte completa a trs nveis, num s andar.

O conversor Boost est inserido no inversor, Fig. 3.1, o que leva a uma diminuio do nmero

de componentes, sendo esta uma vantagem na medida em que diminui o nvel de perdas. Com

esta reduo de perdas consegue-se uma optimizao do rendimento.

9

Fig. 3.1 Conversor DC-AC de um s andar para sistemas fotovoltaicos.

3.2.1 Inversor

A topologia em estudo constituda por um inversor em ponte completa, Fig. 3.2. Este

constitudo pelos transstores T1, T2, T3 e T4, pelo condensador C

F

, pelo filtro que neste caso

apenas a bobine L

R

, e pela rede elctrica monofsica.

Fig. 3.2 Esquema do inversor em ponte completa a vermelho.

As tenses v

A

e v

B

so as tenses no emissor do transstor T2 e T1 respectivamente, e v

AB

a

tenso de sada do inversor. Existem 4 estados possveis de funcionamento para os

transstores, estes esto esquematizados na Tabela 3.1. Nesta topologia o inversor tem a

tenso de sada a trs nveis, ou seja, v

AB

pode assumir os valores 0, :

CP

e -:

CP

.

10

Tabela 3.1 Estados de funcionamento dos transstores do inversor em ponte completa.

T1 T2 T3 T4 v

A

v

B

v

AB

I

LR

Nome do

estado

V

Rede

> 0 V

Rede

< 0

off on on off :

CP

0 :

CP

s

00

on off off on 0 :

CP

-:

CP

s

01

on on off off :

CP

:

CP

0 s

10

off off on on 0 0 0 s

11

3.2.1.1 Tenso da rede positiva

No caso da tenso da rede ser positiva, utilizam-se apenas os estados s

00

, s

10

e s

11

. O estado

s

00

faz com que a tenso de sada do inversor seja :

CP

, e assim, o valor da corrente na bobine

L

R

suba. Por outro lado utiliza-se o estado s

10

, ou s

11

para fazer com que a tenso de sada do

inversor seja nula, e assim, o valor da corre te na bine L

R

desa. n bo

I

Rcdc

> u (3.1)

I

AB

= I

LR

+I

Rcdc

(3.2)

No estado s

00

, Fig. 3.3,

I

AB

= :

CP

(3.3)

Fig. 3.3 Esquema do circuito no estado s

00

.

Por (3.2) e (3.3) tem-se:

I

LR

= :

CP

-I

Rcdc

(3.4)

11

i

L

(t) = I

LRncuI

+

1

I

_:

L

Jt

(3.5)

Substituindo (3.4) em (3.5) obtm-se para t

A

< t < t

B

:

i

LR

(t) = I

LR1

+

1

I

R

_(:

CP

-I

Rcdc

)Jt

(3.6)

Como a frequncia de comutao dos transstores (=20 kHz) muito superior frequncia da

rede (50Hz), ento entre t

A

e t

B

a tenso da rede aproximadamente constante, V

Rede

= cte,

pelo que:

i

LR

(t) = I

LR1

+

t

L

R

(:

CP

-I

Rcdc

),

(3.7)

isto significa que entre t

A

e t

B

a corrente i

LR

uma recta com declive positivo, Fig. 3.4, dado que

:

CP

ser sempre superior ao valor da tenso da rede. O declive dado pelo valor da tenso da

rede, pelo valor da tenso no co densador e pelo valor da bobine L

R

. n

:

AB

-:

CF

:

CF

:

RcJc

i

IR

t

A

t

B

t

C

t

t

E

t

F

Fig. 3.4 Diagramas temporais da tenso de sada do inversor, corrente na bobine e tenso da

rede.

No estado s

10

, Fig. 3.5 a), ou no estado s

11

, Fig. 3.5

I

AB

= u

b),

(3.8)

12

a) b)

Fig. 3.5 Esquema do circuito: a) no estado s

10

,b) no estado s

11

.

Por (3.2) e (3.8) tem-se:

I

LR

= -I

Rcdc

(3.9)

Substituindo (3.9) em (3.5) obtm-se para t

B

< t < t :

C

i

LR

(t) = I

LR2

+

1

I

R

_ (-I

Rcdc

)Jt (3.10)

Assumindo a simplificao acima referida, ento entre t

B

e t

C

a tenso da rede

aproximadamente constante, V

Rede

cte, pelo que: =

i

LR

(t) = I

LR2

+

t

L

R

(-I

Rcdc

),

(3.11)

isto significa que entre t

B

e t

C

a corrente i

LR

uma recta com declive negativo, Fig. 3.4. O

declive dado pelo valor da tenso da rede e pelo valor da bobine L

R

.

3.2.1.2 Tenso da rede negativa

No caso da tenso da rede ser negativa, utilizam-se apenas os estados s

01

, s

10

e s

11

. O estado

s

01

faz com que a tenso de sada do inversor seja -:

CP

e assim, o valor da corrente na bobine

L

R

desa. Por outro lado utiliza-se o estado s

10

, ou o estado s

11

para fazer com que a tenso de

sada do inversor seja nula, e assim, o valor da c ne L

R

suba. orrente na bobi

I

Rcdc

< u (3.12)

No estado s

01

, Fig. 3.6,

I

AB

= -:

CP

(3.13)

13

Fig. 3.6 Esquema do circuito no estado s

01

.

Por (3.2) e (3.13) tem-se:

I

LR

= -:

CP

-I

Rcdc

(3.14)

Substituindo (3.14) em (3.5) obtm-se para t

D

< t < t :

E

i

LR

(t) = I

LR3

+

1

I

R

_ (-:

CP

-I

Rcdc

)Jt (3.15)

Assumindo a simplificao acima referida, ento entre t

D

e t

E

a tenso da rede

aproximadamente constante, V

Rede

pe qu = cte, lo e:

i

LR

(t) = I

LR3

+

t

L

R

(-:

CP

-I

Rcdc

),

(3.16)

isto significa que entre t

D

e t

E

a corrente i

LR

uma recta com declive negativo, Fig. 3.4, dado

que :

CP

ser sempre superior ao valor da tenso da rede. O declive dado pelo valor da

tenso da rede, pelo valor da tenso no condensador e pelo valor da bobine L

R

.

No estado s

10

, Fig. 3.5 a), ou no estado s

11

, Fig. 3.5

I

AB

= u

b),

(3.17)

Por (3.2) e (3.17) tm-se:

I

LR

= -I

Rcdc

(3.18)

Substituindo (3.18) em (3.5) obtm-se para t

E

< t : t <

F

i

LR

(t) = I

LR4

+

1

I

R

_(-I

Rcdc

)Jt (3.19)

Assumindo a simplificao acima referida, ento entre t

E

e t

F

a tenso da rede

aproximadamente constante, V

Rede

= cte, pelo que :

i

LR

(t) = I

LR4

+

t

I

R

(-I

Rcdc

) (3.20)

14

Como a tenso da rede negativa, ento entre t

E

e t

F

a corrente i

LR

uma recta com declive

positivo, Fig. 3.4. O declive dado pelo valor da tenso da rede e pelo valor da bobine L

R

.

3.2.1.3 Factor de ciclo do inversor

Para garantir que a corrente seja injectada na rede de t

A

a t

C

, o valor mdio da tenso v

AB

tem

de ser superior ao valor de tenso na rede, ness po, ou seja: e intervalo de tem

:

AB

=

1

I

_ :

AB

(t)Jt =

t

C

t

A

t

B

-t

A

I

:

CP

+u :

Rcdc

(3.21)

:

Rcdc

(t = I

Rcdc

scn(t)

I = (t -t

A

+

C

-t

B

)

) (3.22)

B

) (t

I

=

t

B

-t

A

I

(3.23)

(3.24)

Sendo a tenso da rede, o perodo da funcionamento do inversor e o factor de ciclo do inversor

dado por (3.22), (3.23) e (3.24) respectivamente, obtm-se:

I

I

Rcdc

:

CP

(3.25)

3.2.2 Conversor DC-DC

A topologia em estudo tem um conversor DC-DC, do tipo Boost, inserido no inversor, de forma

a constituir uma topologia de um s andar, Fig. 3.7. O conversor Boost constitudo pelos

transstores T3 e T4, pelo condensador C

F

, pelos dodos D1, D2, pelos dodos que esto em

anti-paralelo com os transstores T1 e T2, pela bobine L

P

, e pelo painel PV (ou vector de

painis PV).

Fig. 3.7 Esquema do conversor Boost a vermelho.

15

Esta topologia ao utilizar os componentes do inversor permite ter dois conversores Boost,

Fig. 3.8. Ambos tm em comum o painel PV, o condensador C

F

e a bobine L

P

. Relativamente a

um conversor Boost convencional, estes possuem mais dois dodos, D1 e D2. Estes servem

para proteco, impedindo que a corrente do inversor afecte o funcionamento dos conversores

Boost.

Fig. 3.8 Esquema dos dois conversores Boost formados por esta topologia: a) primeiro

conversor Boost, b) segundo conversor Boost.

Assumindo que o conversor opera a um perodo T e que os componentes so ideais, vai

analisar-se o funcionamento do primeiro conversor Boost num perodo de operao, sendo que

para o segundo conversor a analise anloga.

3.2.2.1 Para t

A

< t < t

B

O transstor T3 est ligado, Fig. 3.9.

I

LP

= I

PuncI

(3.26)

PV

L

P

Fig. 3.9 Esquema do circuito do conversor Boost com T3 ligado.

A corrente na bobine do conversor Boost, I

LP

, dada por:

i

LP

(t) = I

LPncuI

+

1

I

P

_:

LP

Jt (3.27)

16

Assumindo que no instante t

A

a corrente tem o valor I

LP1

, e o valor da tenso no painel

constante, ento:

i

LP

(t) = I

LPncuI

+

1

L

P

]I

PuncI

Jt = I

LP1

+

v

Pcincl

L

P

t, (3.28)

isto significa que a corrente i

LP

uma recta com declive positivo que parte do valor inicial I

LP1

,

Fig. 3.10. O declive dado pelo valor d tenso no painel e pelo valor da bobine L

P

. a

:

Poincl

:

IP

t

:

Poincl

-:

CF

i

IP2

i

IP

t

i

IP1

t

A

t

B

t

C

Fig. 3.10 Diagramas temporais da tenso e corrente na bobine L

P

do conversor Boost, quando

est a funcionar no modo de conduo contnua.

3.2.2.2 Para t

B

< t < t

C

O transstor T3 est desligado, Fig. 3.1 1.

I

LP

= I

Poincl

-:

CP

(3.29)

Fig. 3.11 Esquema do circuito do conversor Boost com T3 desligado.

17

Assumindo que no instante t

B

a corrente tem o valor I

LP2

, e os valores das tenses no painel e

no condensador C

F

stante en por so con s, to .27) tem-se:

i

LP

(t) = I

LPncuI

+

1

L

P

(3

](I

PuncI

-:

CP

) Jt = I

LP2

+

v

Pcincl

-

CF

L

P

t, (3.30)

isto significa que a corrente i

LP

uma recta que parte do valor inicial I

LP2

, com declive negativo,

pois o valor da tenso :

CP

superior ao valor da tenso do painel PV, Fig. 3.10. O declive

dado pelo valor da tenso no painel, pelo valor da tenso no condensador C

F

, e pelo valor da

bobine L

P

.

3.2.2.3 Factor de ciclo do conversor Boost

O valor mdio da tenso na bobine L em regime permanente zero:

P

:

LP

= _ I

LP

Jt

t

C

t

A

= _ I

LP

Jt

t

B

+_ I

LP

Jt

t

C

t

B

= u

t

A

t

(3.31)

B

-t

A

=

B

I

t

C

-t

B

= (1 -

B

)I

(3.32)

(3.33)

Por (3.31), (3.32) e (3.33) em-s t e:

I

PuncI

B

I +(I

Poincl

-:

CP

) (1 -

B

)I = u (3.34)

Atravs de (3.34) podemos obter o factor de ra o conversor Boost: ciclo pa

B

=

:

CP

-I

puncI

:

CP

(3.35)

3.2.3 Conversor de um s andar

Do ponto de vista do funcionamento do inversor, o zero da tenso de sada do inversor, v

AB

=0,

pode ser obtido tanto com o estado s

10

como com o s

11

. Do ponto de vista do funcionamento do

conversor Boost estes dois estados so diferentes. A escolha do estado s

11

faz elevar o valor

da corrente na bobine L

P

, enquanto o estado s

10

faz com que o valor desta corrente desa. Este

grau de liberdade permite que no zero da tenso de sada do inversor, seja possvel o controlo

do conversor Boost.

3.2.3.1 Equilbrio energtico

O conversor Boost retira a energia do painel PV e armazena-a no condensador C

F

. O inversor

retira a energia armazenada no condensador e transfere-a para a rede elctrica. Considerando

um rendimento do sistema de 100 %, ento qualquer diferena entre a potncia fornecida pelo

painel, P

PV

, e a potncia entregue rede, P

R

, provoca uma perturbao no valor da tenso em

C

F

. Se o sistema estiver a entregar rede mais potncia do que aquela que est a ser extrada

18

do painel, P

R

>P

PV

, ento o valor da tenso em C

F

vai diminuir. Pelo contrrio, se o sistema

estiver a extrair do painel uma potncia superior quela que est a entregar rede, P

PV

>P

R

,

ento o valor da tenso em C

F

vai aumentar. O valor da tenso no condensador C

F

um

indicador do equilbrio energtico deste conversor, e utilizada no sistema de controlo, para

regular a amplitude da corrente sinusoidal injectada na rede pelo inversor.

3.2.3.2 Formas de onda da corrente e da tenso no condensador C

F

A corrente e a tenso no condensador C

F

vo ser definidas considerando que o conversor

Boost e o inversor so dois blocos independentes, ou seja, enquadram-se numa topologia de

dois andares, Fig. 3.12. Este topologia equivalente topologia de um s andar em estudo,

contudo o raciocnio para definir a corrente e a tenso no condensador C

F

torna-se mais

simples.

Fig. 3.12 Topologia equivalente topologia em estudo.

A tenso da rede dada por (3.22) em que a frequncia da rede 50 Hz. A corrente na bobine

L

R

, i

LR

, tem a componente fundamental a 50Hz, e outras componentes de alta frequncia

devido frequncia de comutao dos transstores do inversor. Considerando apenas a

componente fundamental, a corrente i

R

er r:

L

pode s dada po

i

LR

(t) = I

LR

scn(t) (3.36)

Sendo a potncia instantn a inj a n ed ctr d e ectad a r e el ica ada por:

p

Rcdc

= : i = I I scn

2

(t)

Rcdc LR Rcdc LR

scn

2

(wt) =

1

2

(3.37)

-

1

2

cos(2t) (3.38)

Pela relao trigonomtrica (3.38) pode rescrever- e a xpresso s e

p

Rcdc

= I

Rcdc

I

LR

|

1

2

(3.37) como:

-

1

2

cos(2t) ] (3.39)

Considerando um rendimento de 100 % no inversor, ento a potncia entregue rede ser

igual potncia na entrada do inversor, e assumindo que o condensador C

F

j est carregado

com :

CP

tem-se:

19

i

I

(t) :

CP

= I

Rcdc

I

LR

_

1

2

-

1

2

cos(2t) _ =

=i

I

(t) =

I

Rcdc

I

LR

2 :

CP

|1 -cos(2t) ] (3.40)

Assumindo que o conversor de um s andar est a funcionar de forma a obter um equilbrio

energtico, ou seja, o valor da potncia extrada do painel igual ao valor da potncia entregue

rede, ento o valor mdio da corrente no condensador C

F

zero. Estando o condensador C

F

a contribuir apenas com a componente alternada para a corrente i

I

(t), tem-se:

i

CP

(t) = i

=

I

Rcdc

I

LR

2 :

CP

cos(2t) (3.41)

:

c]

=

1

C

P

_i

CP

(t) Jt =

I

Rcdc

I

LR

4 C

P

:

CP

cos(2t) (3.42)

:

CP

(t) = :

CP

+

I

Rcdc

I

LR

4 C

P

:

CP

cos(2t) (3.43)

:

CP

= 2

I

Rcdc

I

LR

4 C

P

:

CP

(3.44)

Observa-se atravs da Fig. 3.13, que a tenso no condensador oscila em torno do seu valor

mdio, :

CP

, com uma frequncia que o dobro da frequncia da rede. Quando o valor da

corrente injectada na rede baixo, o painel est a fornecer mais energia do que aquela que o

conversor fornece rede, e esse excesso de energia armazenada no condensador C

F

,

fazendo subir o valor da tenso v

CF

. Quando o valor da corrente injectada na rede elevado, o

painel est a fornecer menos energia do que aquela que o conversor fornece rede, e essa

diferena de energia fornecida pelo condensador C

F

, fazendo descer o valor da tenso v

CF

.

20

:

CF

:

CF

i

IR

t

1ums

2ums

Fig. 3.13 Formas de onda da tenso no condensador C

F

e da rede elctrica.

3.2.4 Dimensionamento

No dimensionamento do conversor de um s andar so impostas algumas restries, para ser

possvel o funcionamento simultneo do inversor e do conversor Boost.

3.2.4.1 Definir o valor de u

CF

Analisando este conversor conclui-se que a capacidade de controlar a corrente injectada na

rede, i

LR

, em simultneo com a corrente vinda do painel fotovoltaico, i

LP

, est dependente da

existncia de tempos em que a tenso de sada do inversor nula, v

AB

=0, o que permite

aumentar ou diminuir o valor da corrente i

LP

. Desta forma o funcionamento do conversor Boost

est dependente do funcionamento do inversor, o que faz com que o factor de ciclo do

conversor Boost tenha de ser superior ao factor de ciclo mnimo do inversor, para que o

primeiro possa corrigir durante o tempo em que v

AB

=0 o erro na corrente i

LP

introduzido durante

o tempo que v

AB

0. Atravs das expresses do factor de ciclo do inversor (3.25) e do conversor

Boost (3.35), obtm-se:

:

CP

-I

PuncI

:

CP

>

I

Rcdc

:

CP

(3.45)

Considerando V

R

=2302 V e colocando (3.45) em ordem a :

CP

, encontra-se os valores

mnimos para a tenso no condensa ,

in

dor C

F

:

CP m

, funo da tenso mxima no painel PV: em

:

CP min

= I

Rcdc

+I

PuncI

(3.46)

3.2.4.2 Dimensionamento de C

F

O condensador C

F

dimensionado consoante o ripple de tenso que se pretende, sendo este

obtido atravs de (3.44). Colocando a expresso do ripple em ordem a C

F

, obtm-se:

21

C

P

=

I

Rcdc

I

LR

:

CP

2 :

CP

=

P

Rcdc

:

CP

:

CP

(3.47)

3.2.4.3 Dimensionamento da bobine L

R

O intervalo de variao da frequncia de funcionamento do inversor, f

I

, obtido atravs da

evoluo de i

LR

e o seu respectivo ripple, i

LR

, sendo este ltimo constante. Considerando o

caso em que v

R

positiva, ento de acordo com a Fig. 3.4 obtm-se para v

AB

= :

CP

(3.48) e

v

AB

=0 (3.49).

i

LR

+

=

:

CP

-I

Rcdc

R

I

(t

B

-t

A

) (3.48)

i

R

-

=

-I

Rcdc

L

I

R

(t -t

B

)

C

i

L

= i

+

= -i

LR

-

(3.49)

R LR

I

I

= (t

B

-t

A

) +(t

C

-t

B

) = i

LR

I

R

:

CP

(3.50)

:

CP

I

Rcdc

-I

Rcdc

2

(3.51)

Para V

Rede

=V

Rede fmax

obtm-se T

Imin

:

I

Imn

= i

LR

I

R

:

CP

:

CP

I

Rcdc ]mux

-I

Rcdc ]mux

2

(3.52)

Imux

=

1

I

Imn

=

:

CP

I

Rcdc ]mux

-I

Rcdc ]mux

2

i

LR

I

R

:

CP

(3.53)

De acordo a Fig. 3.14, o valor mximo para a frequncia de funcionamento do inversor, f

Imax

,

obtido para:

I

Rcdc ]mux

= _

:

CP

2

, I

Rcdc

>

:

CP

2

I

R

I

Rcdc

<

:

CP

cdc

,

2

(3.54)

Imux

=

`

1

1

1

1

:

CP

4 i

LR

I

R

, I

Rcdc

>

:

CP

2

:

CP

I

Rcdc

-I

Rcdc

2

:

CP

i

LR

I

R

, I

Rcdc

<

:

CP

2

(3.55)

22

:

CF

Imox

I

RcJc

Fig. 3.14 Representao de f

Imax

em funo de V

Rede

(3.53). A vermelho para F

Rede

<

u

CF

2

, e a azul

para F

Rede

>

u

CF

2

.

O dimensionamento da bobine L

R

definido para um determinado valor de ripple da corrente

i

LR

, assim como para um valor de frequncia xima de funcionam to do inversor. m en

I

R

=

`

1

1

1

1

:

CP

4 i

LR

Imux

, I

Rcdc

>

:

CP

2

:

CP

I

Rcdc

-I

Rcdc

2

:

CP

i

LR

Imux

, I

Rcdc

<

:

CP

2

(3.56)

3.2.4.4 Dimensionamento da bobine L

P

O intervalo de variao da frequncia de funcionamento do conversor Boost, f

B

, obtido

atravs da evoluo de i

LP

e o seu respectivo ripple, i

LP

, sendo este ltimo constante. De

acordo com a Fig. 3.10 obtm-se:

i

LP

+

=

I

PuncI

I

P

(t -t

A

)

B

i

LP

-

=

I

PuncI

-:

CP

(3.57)

I

P

(t -t

B

)

C

i = i

+

= -i

LP

-

(3.58)

LP LP

I

B

= (t

B

-t

A

) +(t

C

-t

B

) = i

LP

I

P

:

CP

(3.59)

:

CP

I

PuncI

-I

PuncI

2

(3.60)

Para V

Painel

=V

Painel max

obtm-se T :

Bmin

I

Bmn

= i

LP

I

P

:

CP

:

CP

I

PuncI mux

-I

PuncI mux

2

(3.61)

Bmox

=

1

I

Bmn

(3.62)

23

O dimensionamento da bobine L

P

definido para um determinado valor de ripple da corrente

i

LP

, assim como para um valor de freq mxim e funcionamento do conversor Boost. uncia a d

I

P

=

:

CP

I

PuncI mox

-I

PuncI mux

2

i

LP

Bmux

:

CP

(3.63)

3.2.4.4 Tabela com dimensionamento do conversor

Na Tabela 3.2 esto representados os valores para os quais se pretende dimensionar este

conversor.

Tabela 3.2 Tabela com o dimensionamento da topologia.

Variveis Valores

Potncia 1 kW

V

Painel

143 V

F

I max

20 kHz

F

B max

10 kHz

I

LR

6,15 A

i

LR

9,75 %

i

LP

7 A

i

LP

10 %

V

CF

500 V

v

CF

2 %

C

F

640 F

L

R

10,4 mH

L

P

14,6 mH

3.3 Sistema de Controlo

O sistema de controlo do conversor essencial, pois este que vai determinar quais os

transstores que devem estar conduo, em cada instante. Este conversor de um s andar

necessita de controlar trs variveis:

Corrente a injectar na rede, i

LR

para atravs desta controlar o valor de potncia que o

conversor est a entregar rede.

Corrente pedida ao painel PV, i

LP

para atravs desta controlar o valor de potncia que o

conversor est a retirar do painel.

Tenso no condensador C

F

, v

CF

para atravs desta conseguir que o conversor esteja a

funcionar de modo a atingir o equilbrio energtico.

24

O esquema elctrico do sistema de controlo utilizado neste conversor est representado na

Fig. 3.15.

Fig. 3.15 Esquema elctrico do sistema de controlo do conversor.

3.3.1 Sistema de controlo das correntes i

LR

e i

LP

O sistema de controlo das correntes i

LR

e i

LP

baseado num controlo histertico [7]. Este tipo

de controlo feito em modo de corrente. Este mtodo consiste essencialmente na comparao

do valor da corrente amostrada com dois nveis de referncia, tomando-se decises quando a

corrente cruza cada um desses dois nveis.

3.3.1.1 Controlo de i

LR

O controlo da corrente i

LR

consiste na comparao desta com uma corrente de referncia, i

LRref

,

atravs de um comparador com uma janela de histerese de valor i

LR

, Fig. 3.16. A forma de

obter a corrente i

LRref

referida no captulo 4.

Fig. 3.16 Controlo histertico de i

LR

.

25

Ao sinal proveniente da sada do comparador designado , este um sinal digital e pode

assumir os seguintes valores:

= _

u, i

LR

< i

LRc]

-

i

LR

2

1, i

LR

> i

LRc]

+

i

LR

2

(3.64)

No diagrama temporal da Fig. 3.17, esto representados os sinais de entrada do comparador.

i

IR

= u = 1

i

IR

rc

i

IR

i

IRrc

+

Ai

IR

2

i

IRrc

-

Ai

IR

2

Fig. 3.17 Diagrama temporal do valor Q consoante a corrente i

LR

e a sua referncia.

3.3.1.2 Controlo de i

LP

O controlo da corrente i

LP

consiste na comparao desta com uma corrente de referncia, i

LPref

,

atravs de um comparador com uma janela de histerese de valor i

LP

, Fig. 3.18. A corrente i

LPref

pode ser obtida atravs de um algoritmo de procura do ponto de potncia mxima do painel

PV.

B

Fig. 3.18 Controlo histertico d

LP

. e i

Ao sinal proveniente da sada do comparador designado B, este um sinal digital e pode

assumir os seguintes valores:

B = _

u, i

LP

< i

LPc]

-

i

LP

2

1, i

LP

> i

LPc]

+

i

LP

2

(3.65)

No diagrama temporal da Fig. 3.19, esto representados os sinais de entrada do comparador.

26

i

I

i

Prc

B = u B = 1

i

IP

IP

i

IPrc

+

Ai

IP

2

i

IPrc

+

Ai

IP

2

Fig. 3.19 Diagrama temporal do valor B consoante a corrente i

LP

e a sua referncia.

3.3.1.3 Co rolo dos transstores nt

Os sinais e B servem para controlar quais os transstores que devem estar ligados num

determinado instante. Contudo nesta topologia est inserido um inversor em ponte completa a

trs nveis, sendo necessrio ter outro sinal digital, I, que indica se a tenso da rede est no

meio ciclo positivo ou negativo:

I = _

u, :

Rcdc

< u

1, :

Rcdc

> u

(3.66)

Este sinal obtido comparando uma amostra da tenso da rede com zero, Fig. 3.20. Atravs

do controlo desta varivel consegue-se que o conversor tenha um factor de potncia quase

unitrio.

I

Fig. 3.20 Controlo para obter o ciclo de onda da tenso da rede.

Tendo os trs sinais digitais definidos possvel obter os estados dos transstores, assim como

saber o que acontece s correntes i

LR

e i

LP

durante esses mesmos estados. Na Tabela 3.3

esto representados os nveis lgicos das tenses das portas dos transstores para os estados

possveis, consoante os sinais digitais I, e B. No que diz respeito corrente i

LP

existem

alguns estados em que esta no controlada, devido ao funcionamento do conversor Boost

estar dependente do funcionamento do inversor. Estes correspondem a estados em que os

transstores das diagonais esto ligados, s

00

e s

01

. Nesta topologia os dodos de proteco D1

e D2 tm o nodo comum, logo o que tiver menor tenso de ctodo o que entra conduo.

Isto faz com que nesses estados os transstores T3 ou T4 entrem conduo, fazendo

aumentar a corrente i

LP

, independentemente do controlo.

27

Tabela 3.3 Nveis lgicos das tenses das portas dos transstores.

V B Q

Estado das

variveis

Efeito do

T1 T2 T3 T4

i

LP

i

LR

0 0 0

v

R

LP IPrc

-

i

P

< 0

i < i

L

2

i

LR

< i

LRc]

-

i

LR

2

0 0 1 1

0 0 1

v

R

LP

LP

< 0

i < i

LPc]

-

i

2

i

LR

> i

LRc]

+

i

LR

2

1 0 0 1

0 1 0

v

R

LP

< 0

i

LP

> i

LPc]

+

i

2

i

LR

< i

LRc]

-

i

LR

2

1 1 0 0

0 1 1

v

R

LP

LP

< 0

i > i

LPc]

+

i

2

i

LR

> i

LRc]

+

i

LR

2

X 1 0 0 1

1 0 0

v

R

LP

LP

> 0

i < i

IPrc

-

i

2

i

LR

< i

IRrc

-

i

LR

2

0 1 1 0

1 0 1

v

R

i

LP IPrc

-

i

P

> 0

< i

L

2

i

LR

> i

LRc]

+

i

LR

2

0 0 1 1

1 1 0

v

R

c

LP

> 0

i

LP

> i

IPr

+

i

2

i

LR

< i

IRrc

-

i

LR

2

X 0 1 1 0

1 1 1

v

R

LP Prc

LP

> 0

i > i

I

+

i

2

i

LR

> i

IRrc

+

i

LR

2

1 1 0 0

As tenses nas portas dos transstores T3 e T4 so o negado das tenses nas portas de T1 e

T2 respectivamente, devido impossibilidade de dois transstores do mesmo brao estarem

em conduo simultnea, ento necessrio apenas definir a funo de duas delas, neste

caso para T1 e T2. Os mapas de Karnaugh destas funes esto representados na Fig. 3.21,

de onde se retira as equaes (3.67) e (3.68).

28

B

I

B

I

I1 I2

u

u u u

u u u

u

1 1 1

1 1 1

1

1

uu u1 11 1u uu u1 11 1u

u

1

u

1

Fig. 3.21 Mapas de Karnaugh ra a funes de T1 e T2. pa s

I1 = B Q +v

B +v

Q

I2 = I B +v Q

(3.67)

+B Q

(3.68)

Com as equaes (3.67) e (3.68) possvel implementar em portas lgicas o circuito de

controlo dos transstores, Fig. 3.22. Para obter as funes de T3 e T4 basta uma porta lgica

not na sada das funes T1 e T2 respectivamente.

Fig. 3.22 Circuito lgico de controlo dos transstores.

3.3.2 Sistema de controlo da tenso v

CF

O controlo da tenso no condensador C

F

, v

CF

, fundamental para obter o equilbrio energtico

do sistema. Contudo apenas se ir controlar o valor mdio da tenso no condensador C

F

, e no

o valor da harmnica de 100 Hz presente nesta tenso. Neste caso considerou-se a tenso

mdia no condensador de 500 V. O circuito de controlo da tenso v

CF

est representado na

Fig. 3.23.

29

Fig. 3.23 Esquema elctrico do sistema de controlo da tenso no condensador C

F. w

De acordo com a Fig. 3.23, a equao o sistema vem dada por: d

:

CP

(t) =

1

C

P

_i

CP

Jt =

1

C

P

_(I

B

-i

I

)ut (3.69)

Aplicando a transformada de Laplace a (3.69) b o tm-se:

I

CP

(s) =

I

B

(s) -I

I

(s)

s

P

C

(3.70)

I

I

=

I

Rcdc

I

LR

2 I

CP

(3.71)

Para que exista equilbrio energtico a amplitude da corrente i

LR

tem de ser igual amplitude

do sinal v

CTR

, portanto tem-se:

I

I

=

I

Rcdc

I

C1R

2 I

CP

= u.S2S I

C1R

(3.72)

O diagrama de blocos do sistema de controlo Fig. 3.24 tem a referncia V

CFref

(s) com sinal

negativo e a realimentao com sinal positivo, para que o sistema possua realimentao

negativa.

30

1

s C

F

Fig. 3.24 Diagrama de blocos do sistema.

3.3.2.1 Controlador proporcional

Ao adicionar ao diagrama de blocos do controlador um bloco com ganho k obtm-se o

diagrama de blocos de um controlador proporcional Fig. 3.25.

1

s C

F

Fig. 3.25 Diagrama de blocos do sistema com controlador proporcional.

Para analisar a estabilidade do sistema no se considerou a perturbao I

B

(s), obtendo-se a

equao de transferncia em cadeia fechada:

I

CP

(s)

I

CPc]

(s)

=

k u,S2SC

P

s +u,u1 k u,S2SC

P

(3.73)

Com a funo de transferncia do sistema em cadeia aberta (3.74), pode utilizar-se o root locus

para determinar o valor de k, Fig. 3.26. Podemos concluir que o sistema sempre estvel para

um valor de k>0.

t

cu

(s) =

k u,S2S u.u1C

P

s

(3.74)

31

Fig. 3.26 Root locus do sistema em cadeia aberta.

De seguida analisa-se a resposta no tempo do sistema em cadeia fechada, com a introduo

da perturbao I

B

(s) para diferentes valores de k. I

B

(s) um escalo de com valor inicial 2 A e

valor final 0,5 A. Pelas Fig. 3.27 e Fig. 3.28 conclui-se que com o aumento de k o erro em

regime estacionrio na tenso v

CF

diminui. A perturbao introduzida pela corrente I

B

, faz com

que o erro em regime permanente na tenso v

CF

tambm diminua.

Fig. 3.27 Resposta no tempo do sistema com controlador proporcional, k=10.

32

Fig. 3.28 Resposta no tempo do sistema com controlador proporcional, k=40.

Na Fig. 3.29 analisa-se o sistema com a introduo da perturbao A(s), que corresponde

componente alternada de 100 Hz na corrente i

I

(3.40). Esta componente vai reflectir-se na

tenso v

CF

, fazendo com que v

CTR

possua tambm uma componente a 100 Hz, Fig. 3.30. Como

i

LR

proporcional a v

CTR

, ento a corrente a ser injectada na rede vai possuir uma distoro

harmnica maior produzida por esta componente alternada. Este facto faz com que o uso de

um controlador apenas proporcional no seja aconselhado.

1

s C

F

Fig. 3.29 Diagrama de blocos do sistema com controlador proporcional, com a perturbao de

100 Hz.

33

Fig. 3.30 Resposta no tempo do sistema com controlador proporcional, k=20 e perturbao de

100 Hz.

3.3.2.2 Controlador proporcional com constante de tempo

Para resolver o problema da componente alternada de 100 Hz na tenso v

CTR

necessrio que

o controlador tenha um ganho baixo a 100 Hz e elevado a baixa frequncia. O diagrama de

bode do sistema em cadeia aberta com controlador proporcional, para k=20, est representado

na Fig. 3.31. Pelo diagrama de bode conclui-se que para obter um ganho de -40 dB a 100 Hz

teria de se posicionar um plo quase duas dcadas antes. Contudo, quanto mais baixa for a

frequncia desse plo, mais lenta vai ser a resposta no tempo do sistema. De forma a se obter

uma relao de compromisso, vai posicionar-se a frequncia deste plo a 8 Hz e redimensionar

o ganho k para se conseguir a atenuao pretendida a 100 Hz.

34