Escolar Documentos

Profissional Documentos

Cultura Documentos

EELi03 - Experimento 04 - Júlio César Ribeiro Silva

Enviado por

Júlio0 notas0% acharam este documento útil (0 voto)

9 visualizações2 páginasDireitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

9 visualizações2 páginasEELi03 - Experimento 04 - Júlio César Ribeiro Silva

Enviado por

JúlioDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 2

Universidade Federal de Itajubá – UNIFEI Campus de Itabira

EELi03 – Laboratório de Circuitos Lógicos

Trabalho associado ao Experimento 04

Integrantes: 2020016861 – Júlio César Ribeiro Silva

Parte II: Prática

1.

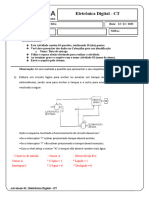

a. Montagem do circuito Full Arder na Figura 1.

Figura 1 – Circuito Full Arder.

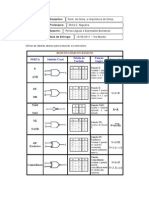

b. Tabela verdade circuito Full Arder

Entrada Saída

Cin Aj Bj Sout Cout

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Nota-se que as saídas do circuito Full Arder, LED acesso, conferem com as saídas

esperadas da tabela verdade.

2.

a. Circuito somador/subtrator de 4 bits

b. Tabela circuito somador/subtrator

Parcela 1 Parcela 2 Resultado

Seleção

Binário Binário Binário

Decimal Decimal M Decimal

A3 A2 A1 A0 A3 A2 A1 A0 S4 S3 S2 S1 S0

4 0 1 0 0 2 0 0 1 0 0 6 0 0 1 1 0

9 1 0 0 1 6 0 1 1 0 0 15 0 1 1 1 1

11 1 0 1 1 7 0 1 1 1 0 18 1 0 0 1 0

15 1 1 1 1 8 1 0 0 0 0 23 1 0 1 1 1

3. Tabela verdade para o item 3.

Os números binários da palavra B são convertidos para complemento de 2, por meio de

um conjunto de portas OU-EXCLUSIVO ligadas nas entradas da palavra binaria B. As

entradas das portas OU-EXCLUSIVO são ligadas a seleção da operação (M) e um bit

da palavra B.

Os resultados obtidos conferem com os esperados, já que o circuito executa o

complemento de 2 de forma autônoma da subtração.

Parcela 1 Parcela 2 Resultado

Seleção

Binário Binário Binário

Decimal Decimal M Decimal

A3 A2 A1 A0 A3 A2 A1 A0 S4 S3 S2 S1 S0

5 0 1 0 1 2 0 0 1 0 0 7 0 0 1 1 1

-2 1 1 1 0 6 0 1 1 0 0 4 1 0 1 0 0

-3 1 1 0 1 2 0 0 1 0 0 -1 1 1 1 1 1

-7 1 0 0 1 7 0 1 1 1 0 0 1 0 0 0 0

5 0 1 0 1 2 0 0 1 0 1 3 0 0 0 1 1

-2 1 1 1 0 7 0 1 1 1 1 9 0 0 1 1 1

3 0 0 1 1 3 0 0 1 1 1 0 0 0 0 0 0

7 0 1 1 1 7 0 1 1 1 1 0 0 0 0 0 0

Circuito somador/subtrator utilizando os CIs 74CH283 (Inclusor de 4 bits) e 74CH86

(XOR)

Você também pode gostar

- Experimento 01Documento8 páginasExperimento 01Pedro HAinda não há avaliações

- UFCG-DEE Laboratório Circuitos Lógicos Experimento Verilog CódigosDocumento5 páginasUFCG-DEE Laboratório Circuitos Lógicos Experimento Verilog CódigosGabriel NazarioAinda não há avaliações

- EELI03 - Laboratrio 3Documento3 páginasEELI03 - Laboratrio 3Vinicius MirandaAinda não há avaliações

- Codificador DecodDocumento22 páginasCodificador DecodCesar LoureiroAinda não há avaliações

- LCL Relatorio 1Documento6 páginasLCL Relatorio 1luca50% (2)

- Livro Texto - Unidade IIIDocumento48 páginasLivro Texto - Unidade IIIGeovana DaniellaAinda não há avaliações

- Laboratório CLD RevisadoDocumento61 páginasLaboratório CLD RevisadoGiovanneSiqueiraAinda não há avaliações

- Atividade 02 - Digital (2) - CopiarDocumento5 páginasAtividade 02 - Digital (2) - CopiarleandrodasilveiraoliveiraAinda não há avaliações

- EELi03 T01 Experimento 5Documento11 páginasEELi03 T01 Experimento 5João VitorAinda não há avaliações

- Codigo TesteDocumento11 páginasCodigo Testeluciel castroAinda não há avaliações

- Mapa de Karnaugh para circuitos combinacionaisDocumento7 páginasMapa de Karnaugh para circuitos combinacionaisTong ZhouAinda não há avaliações

- Sd10peac Exercícios Codificadores e DescodificadoresDocumento2 páginasSd10peac Exercícios Codificadores e Descodificadoresnuno silvestreAinda não há avaliações

- Lista de Exercicios de Circuitos LógicosDocumento6 páginasLista de Exercicios de Circuitos LógicoswighouAinda não há avaliações

- LCL Exp 3Documento9 páginasLCL Exp 3Lucas BelloAinda não há avaliações

- Circuitos CombinatóriosDocumento16 páginasCircuitos CombinatóriosPaulo RodriguesAinda não há avaliações

- LCL Codificador, DecodificadorDocumento7 páginasLCL Codificador, DecodificadoriorrannaAinda não há avaliações

- Lista - 04 - Mapas Karnaugh - ExerciciosDocumento5 páginasLista - 04 - Mapas Karnaugh - ExerciciosBruna GimenesAinda não há avaliações

- Portas Lógicas Básicas: Tabelas de Verdade e CircuitosDocumento13 páginasPortas Lógicas Básicas: Tabelas de Verdade e CircuitosguidoAinda não há avaliações

- Relatório 2 - EDDocumento11 páginasRelatório 2 - EDKeith RochaAinda não há avaliações

- Redes de Computadores I - Exercício de Paridade e CRCDocumento6 páginasRedes de Computadores I - Exercício de Paridade e CRCdont4getAinda não há avaliações

- Exercícios 1Documento7 páginasExercícios 1Thiana Tiller Reliquias GomesAinda não há avaliações

- Codificadores e Decodificadores CombinacionaisDocumento6 páginasCodificadores e Decodificadores CombinacionaisAlexandre AugustoAinda não há avaliações

- Especificacao de Materiais PLC RemotasDocumento11 páginasEspecificacao de Materiais PLC RemotasemanuelAinda não há avaliações

- Atividade de Pesquisa 01Documento7 páginasAtividade de Pesquisa 01celsotkAinda não há avaliações

- Circuitos XOR e XNORDocumento6 páginasCircuitos XOR e XNORLucas Pedro ManuelAinda não há avaliações

- exp3_LCLDocumento6 páginasexp3_LCLAna Luiza CamposAinda não há avaliações

- Atividade de Pesquisa 01 Eletronica DigitalDocumento5 páginasAtividade de Pesquisa 01 Eletronica DigitalHenrique MarquesAinda não há avaliações

- Atividade de Pesquisa 01Documento6 páginasAtividade de Pesquisa 01Juliano MartinsAinda não há avaliações

- AP2-ED-Introdução A Algebra de BooleDocumento3 páginasAP2-ED-Introdução A Algebra de BooleFrancisco Gabriel VembaneAinda não há avaliações

- Circuitos Aritméticos: Somadores, Subtratores e Complemento de DoisDocumento11 páginasCircuitos Aritméticos: Somadores, Subtratores e Complemento de DoisNathan SousaAinda não há avaliações

- Experiência 7: Circuitos Mux e DemuxDocumento12 páginasExperiência 7: Circuitos Mux e DemuxEmporio CiaAinda não há avaliações

- LD2J3 Exp6 - Circuitos Aritméticos_231018_071831Documento9 páginasLD2J3 Exp6 - Circuitos Aritméticos_231018_071831ALEX PESSOA PIMENTELAinda não há avaliações

- Atividade Portas LogicasDocumento5 páginasAtividade Portas LogicasNeto Pops100% (1)

- uDX210 manualSSRDocumento3 páginasuDX210 manualSSRroth_scribAinda não há avaliações

- Atividade Prática - Eletrônica Digital RU1567558Documento10 páginasAtividade Prática - Eletrônica Digital RU1567558Heuler LageAinda não há avaliações

- Lista de Exercicios Circuitos LógicosDocumento3 páginasLista de Exercicios Circuitos LógicosAndre BomjardimAinda não há avaliações

- Lista2 - Expressões de LógicasDocumento2 páginasLista2 - Expressões de LógicasCanal Dos BusólogosAinda não há avaliações

- Controle de unidade de corte de madeiraDocumento1 páginaControle de unidade de corte de madeiraKlause Paulino0% (1)

- SomadorDocumento1 páginaSomadorBrayanFreitasAinda não há avaliações

- Eletrônica Digital - CT - Atividade 02Documento5 páginasEletrônica Digital - CT - Atividade 02Patrik100% (2)

- Atividade de Pesquisa 01 - Passei DiretoDocumento6 páginasAtividade de Pesquisa 01 - Passei DiretoJuliano MartinsAinda não há avaliações

- Relatório 7 SegmentosDocumento9 páginasRelatório 7 SegmentosStefano ViégasAinda não há avaliações

- Atividade 3Documento3 páginasAtividade 3Guilherme Ramos da SilvaAinda não há avaliações

- G Atividade 02 - DigitalDocumento6 páginasG Atividade 02 - DigitalrgomesgianiniAinda não há avaliações

- Atividade Mapa de Veitch-Karnaugh I (Gabriel)Documento3 páginasAtividade Mapa de Veitch-Karnaugh I (Gabriel)xmarcos.mf05Ainda não há avaliações

- p6 PDFDocumento3 páginasp6 PDFNinja RoyaleAinda não há avaliações

- Circuito decodificador 8421 no display 7 segmentosDocumento7 páginasCircuito decodificador 8421 no display 7 segmentosFelipe SantosAinda não há avaliações

- uDX210 ManualreléDocumento3 páginasuDX210 Manualreléroth_scribAinda não há avaliações

- P1 B (Para Os Alunos Com RA Final Par) : Fatec de Itaquera Prof. Miguel RealeDocumento3 páginasP1 B (Para Os Alunos Com RA Final Par) : Fatec de Itaquera Prof. Miguel Realematheus alves dos santosAinda não há avaliações

- Ep01 2021Documento1 páginaEp01 2021no name100% (1)

- Relatório 04 - EletrônicaDocumento16 páginasRelatório 04 - Eletrônicaedvandofilho2Ainda não há avaliações

- Pratica 1Documento10 páginasPratica 1Luna JnanaAinda não há avaliações

- Codigos BinariosDocumento12 páginasCodigos BinariosWanderson BrumAinda não há avaliações

- LedDocumento3 páginasLedThiago HenriqueAinda não há avaliações

- Relatorio Circuitos DigitaisDocumento2 páginasRelatorio Circuitos DigitaisMichelli IoccaAinda não há avaliações

- Tabela Verdade Encoder Da Torre - Galaxy 15sDocumento1 páginaTabela Verdade Encoder Da Torre - Galaxy 15sMatheus BorgesAinda não há avaliações

- AT02 Zedekias NobregaDocumento2 páginasAT02 Zedekias NobregaZedekias NobregaAinda não há avaliações

- Desenho e Implementação de uma Unidade Aritmética Lógica (ALU) de 4 bitsDocumento13 páginasDesenho e Implementação de uma Unidade Aritmética Lógica (ALU) de 4 bitsRicardo AragãoAinda não há avaliações

- Geradores Sncronos - Cap11aDocumento7 páginasGeradores Sncronos - Cap11aBruna XavierAinda não há avaliações

- EELi03 - Experimento 07 - Júlio César Ribeiro SilvaDocumento2 páginasEELi03 - Experimento 07 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- EELi03 - Experimento 03 - Júlio César Ribeiro SilvaDocumento3 páginasEELi03 - Experimento 03 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- Simplifique expressões booleanas e monte circuitos lógicosDocumento10 páginasSimplifique expressões booleanas e monte circuitos lógicosJúlioAinda não há avaliações

- EELi03 - Experimento 01 - Júlio César Ribeiro SilvaDocumento10 páginasEELi03 - Experimento 01 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- Miniteste - Semana 4 - Revisão Da TentativaDocumento8 páginasMiniteste - Semana 4 - Revisão Da TentativaManoel SantanaAinda não há avaliações

- Trigonometria - Lista de exercíciosDocumento9 páginasTrigonometria - Lista de exercíciosDéborah Domingos da Rocha100% (1)

- AMOSTRAS Atividades Adaptadas de Matemática 8º Ano Inove Na EscolaDocumento10 páginasAMOSTRAS Atividades Adaptadas de Matemática 8º Ano Inove Na Escolainovenaescola100% (4)

- Simulados de Geometria e Matemática do Ensino FundamentalDocumento5 páginasSimulados de Geometria e Matemática do Ensino FundamentalAldemy GuimarãesAinda não há avaliações

- Fórmula de Bhaskara - Guia completo sobre o método para resolver equações do 2o grauDocumento3 páginasFórmula de Bhaskara - Guia completo sobre o método para resolver equações do 2o grauJorge HonzAinda não há avaliações

- Curso Vitória - P.A. e P.G.-Exercícios de RevisãoDocumento10 páginasCurso Vitória - P.A. e P.G.-Exercícios de RevisãoClaudio Mariano Silva MarianoAinda não há avaliações

- Apostila Nivelamento 2017b PDFDocumento46 páginasApostila Nivelamento 2017b PDFSuene OliveiraAinda não há avaliações

- Historia Das Equações MesopotâmicasDocumento16 páginasHistoria Das Equações Mesopotâmicasluis cassimooAinda não há avaliações

- EsPCEx Soluções Questões MatemáticaDocumento22 páginasEsPCEx Soluções Questões MatemáticaRamon Da MattaAinda não há avaliações

- Determinando valores trigonométricos e resolvendo problemas geométricosDocumento7 páginasDeterminando valores trigonométricos e resolvendo problemas geométricosFilipa VieiraAinda não há avaliações

- Matriz - Foco Na AprendizagemDocumento10 páginasMatriz - Foco Na AprendizagemCaetano RodriguesAinda não há avaliações

- Afa 98 - MatemáticaDocumento5 páginasAfa 98 - Matemáticafabiorj88Ainda não há avaliações

- Resolução de problemas de matemática pré-calculo com explicações detalhadasDocumento6 páginasResolução de problemas de matemática pré-calculo com explicações detalhadasCacis UnstopableAinda não há avaliações

- PolaresDocumento9 páginasPolaresjuliaocbvAinda não há avaliações

- Resolução da prova de matemática da fase 1 do vestibular da UFBA/UFRB-2007Documento12 páginasResolução da prova de matemática da fase 1 do vestibular da UFBA/UFRB-2007AndréAinda não há avaliações

- Análise Harmónica e ComplexaDocumento68 páginasAnálise Harmónica e ComplexaValige Pedro Valige Faria100% (2)

- Caderno Minitestes Questões Aula LógicaDocumento19 páginasCaderno Minitestes Questões Aula LógicaMário OliveiraAinda não há avaliações

- Matemática 3º Ano Do Ensino Médio2017Documento2 páginasMatemática 3º Ano Do Ensino Médio2017Ulisses Marçal de CarvalhoAinda não há avaliações

- Matemática - Provas anteriores da ESA sobre funções e progressõesDocumento10 páginasMatemática - Provas anteriores da ESA sobre funções e progressõesEstevao Ribeiro100% (1)

- Cálculo Diferencial e Integral IDocumento172 páginasCálculo Diferencial e Integral IPedro JohnsonAinda não há avaliações

- Operações com radicais e racionalização de fraçõesDocumento4 páginasOperações com radicais e racionalização de fraçõesWander ArrudaAinda não há avaliações

- Equações Incógnitas e EquaçõesDocumento39 páginasEquações Incógnitas e EquaçõesJoice Santos100% (1)

- Áreas de figuras geométricasDocumento3 páginasÁreas de figuras geométricasJosé Domingos LealAinda não há avaliações

- Ficha 2 Bolzano 12Documento3 páginasFicha 2 Bolzano 12nunomsafigueiredoAinda não há avaliações

- Cálculo Diferencial e Integral II - Armando Righetto e Antonio Sérgio FerraudoDocumento333 páginasCálculo Diferencial e Integral II - Armando Righetto e Antonio Sérgio FerraudoRomáryo Almeida Cavalcanti83% (6)

- Documento de EdusalinoDocumento552 páginasDocumento de Edusalinoeduardo assis100% (2)

- Resumão Matematica Tecnico Edificações SenaiDocumento8 páginasResumão Matematica Tecnico Edificações SenaiMilton Santos100% (1)

- Exercicios2024Documento36 páginasExercicios2024Pedro Alcinda TimaneAinda não há avaliações

- Cálculos geométricos de figuras planasDocumento3 páginasCálculos geométricos de figuras planasEdinardo NayAinda não há avaliações

- Múltiplos e DivisoresDocumento6 páginasMúltiplos e DivisoresAdauto Pereira JúniorAinda não há avaliações