Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista 03 ArqComp

Enviado por

Jader Lucas PerezDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lista 03 ArqComp

Enviado por

Jader Lucas PerezDireitos autorais:

Formatos disponíveis

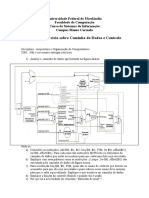

Universidade Federal de Mato Grosso do Sul Curso de Anlise de Sistemas a Disciplina: Arquitetura de Computadores I Professor: Ricardo Santos Lista

de exerc cios 3

1. Com base na tabela a seguir, responda: IF 300ps 200ps ID 400ps 150ps EX 350ps 120ps MEM 500ps 190ps WB 100ps 140ps

(I) (II)

(a) Qual o tempo do ciclo de clock em um processador com e sem pipeline (monociclo)? e (b) Qual a latncia total de uma instruo lw em um processador com e sem pipeline (monoe e ca ciclo)? 2. Baseado na sequncia de instrues a seguir, responda: e co (I) lw $1, 40($6) add $6, $2, $2 sw $6, 50($1) lw $5, -16($5) sw $5, -16($5) add $5, $5, $5

(II)

(a) Indique os tipos de dependncias(verdadeira - de dados -, antidependncia, de sa e e da). (b) Suponha que no exista o forwarding no pipeline de execuo. Indique onde os conitos a ca ocorrem e adicione bolhas(instrues nop) para elimin-los. co a 3. Observe a tabela de tempos a seguir: Classe Load word Store word Formato R Branch Responda: (a) Qual o tempo do ciclo caso este grupo de instrues fossem implementadas no MIPS co monociclo? (b) Qual seria o tempo do ciclo caso este grupo de instrues fossem implementadas no MIPS co multiciclo pipeline? (c) Mostre de quanto a razo de ganho ou perda entre as duas abordagens anteriores caso e a fosse executadas, em sequncia e sem conitos, as instrues lw, add e sw. e co 4. Observe o seguinte segmento de cdigo em C: o a = b + e; c = b + f; Fetch 200ps 200ps 200ps 200ps Reg. Load 100ps 100ps 100ps 100ps ALU 200ps 200ps 200ps 200ps Data Access 200ps 200ps Reg. Write 100ps 100ps

Gerando o cdigo MIPS relativo ao segmento anterior assumindo todas as variveis em o a memria e endereveis com osets de $t0 temos: o ca lw lw add sw lw add sw $t1, $t2, $t3, $t3, $t4, $t5, $t5, 0($t0) 4($t0) $t1, $t2 12($t0) 8($t0) $t1, $t4 16($t0) # # # # # # # b e a a f c c <- mem <- mem = b + e -> mem <- mem = b + f -> mem

Identique os conitos no cdigo MIPS acima e reordene as instrues para evitar qualquer o co stall (bolha, pausa) no pipeline. 5. Para a sequncia de cdigos a seguir, informe se eles iro obrigatoriamente ter stalls, podero e o a a evitar stalls usando apenas forwarding ou podem executar diretamente sem ambos. (a) (b) lw $t0, 0($t0) add $t1, $t0, $t0 add $t1, $t0, $t0 addi $t2, $t0, 5 addi $t4, $t1, 5 addi addi addi addi addi $t1, $t2, $t3, $t3, $t5, $t0, $t0, $t0, $t0, $t0, 1 2 2 4 5

(c)

6. A partir da mquina de estados nitos bsica da unidade de controle do processador MIPS mula a ticiclo, indique quais alteraes (incluso de novos estados, incluso de novos sinais de controle, co a a contedo dos sinais de controle em cada novo estado) so necessrias para que a unidade de u a a controle tenha suporte ` instruo jr. a ca 7. Quais so as condies necessrias e sucientes que devem existir no pipeline do processador a co a MIPS para que a unidade de forwarding seja utilizada? 8. Baseando-se na tabela de latncias do exerc (1) e no trecho de cdigo apresentado no exerc e cio o cio (2), informe o tempo necessrio para execuo desse trecho de cdigo na via de dados monociclo, a ca o multiciclo e pipeline (caso ocorram stalls, considere as bolhas no pipeline) do MIPS. 9. Existe alguma diferena entre o CPI (Ciclos por Instruo) entre um processador monociclo e c ca um processador multiciclo pipeline? Explique.

Você também pode gostar

- case2: Motores 1.6L e 1.8L do VW Gol, Parati e Santana 1993-1996Documento4 páginascase2: Motores 1.6L e 1.8L do VW Gol, Parati e Santana 1993-1996Fabricio Lima75% (4)

- Apostila de PLC AC500 Módulo IDocumento38 páginasApostila de PLC AC500 Módulo IdepimentaAinda não há avaliações

- Lógica de Automação IndustrialDocumento61 páginasLógica de Automação IndustrialHiago bragaAinda não há avaliações

- Exercícios de Arquitetura de ComputadoresDocumento5 páginasExercícios de Arquitetura de ComputadoresDuarlem RobertoAinda não há avaliações

- Haida Lorencini 346656 0Documento25 páginasHaida Lorencini 346656 0haidaAinda não há avaliações

- Exercícios AOC II Parte 1Documento5 páginasExercícios AOC II Parte 1msancorAinda não há avaliações

- ListaExercíciosArquiteturaComputadoresDocumento21 páginasListaExercíciosArquiteturaComputadoresoctaviooliAinda não há avaliações

- DAQmx NI USB 6008 - Aquisição de dadosDocumento5 páginasDAQmx NI USB 6008 - Aquisição de dadosVirgilioAinda não há avaliações

- It - Calandra Hidráulica - 3000 MMDocumento5 páginasIt - Calandra Hidráulica - 3000 MMCristyan Reis100% (1)

- Visagismo - Imagem Humana Como Meio de ComunicaçãoDocumento13 páginasVisagismo - Imagem Humana Como Meio de ComunicaçãoLigia MouraAinda não há avaliações

- Lista Exercicio Caminho Dados ControleDocumento4 páginasLista Exercicio Caminho Dados ControleJonathan BorgesAinda não há avaliações

- 2 ExercíciosACIIIDocumento5 páginas2 ExercíciosACIIIMarlon Bento AzevedoAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento2 páginasArquitetura e Organização de ComputadoreshaidaAinda não há avaliações

- Trabalho MIPSDocumento11 páginasTrabalho MIPSWilson GarciaAinda não há avaliações

- Exercicios Estatistica BioestatisticaDocumento10 páginasExercicios Estatistica Bioestatisticaapi-3724336Ainda não há avaliações

- Exercicios Aula 2Documento2 páginasExercicios Aula 2Leonardo MenegonAinda não há avaliações

- Dicas de Curso Hipath 3000Documento19 páginasDicas de Curso Hipath 3000Davi VitorAinda não há avaliações

- ProvaModelo SMP 2021 Freq2Documento4 páginasProvaModelo SMP 2021 Freq2Pedro SilvaAinda não há avaliações

- Arquitetura de computadores - QuestõesDocumento13 páginasArquitetura de computadores - QuestõesSergio de Oliveira0% (2)

- Atividade InstrumentacaoDocumento9 páginasAtividade Instrumentacaomarcos.pedroso498Ainda não há avaliações

- Lista 43 ControleDocumento8 páginasLista 43 ControleMatheus AganeteAinda não há avaliações

- 5a Lista Exercicios Erro em Regime PermanenteDocumento2 páginas5a Lista Exercicios Erro em Regime PermanentesergiojgsAinda não há avaliações

- Introducao Robotica V5 09jan2022Documento19 páginasIntroducao Robotica V5 09jan2022MauricioAinda não há avaliações

- Lista de Exercícios CLPDocumento11 páginasLista de Exercícios CLPMarcos Ap Chaves FerreiraAinda não há avaliações

- p2021 - 22-P02 (Exercícios Propostos)Documento13 páginasp2021 - 22-P02 (Exercícios Propostos)Erivaldo da SilvaAinda não há avaliações

- Aula 5 - Exercicios 8085Documento16 páginasAula 5 - Exercicios 8085Paulo EduardoAinda não há avaliações

- UNIFEI Programação Embarcada Exame Funções Matemática Timer Display AD ChavesDocumento3 páginasUNIFEI Programação Embarcada Exame Funções Matemática Timer Display AD ChavesAlexandre KennedyAinda não há avaliações

- APX3 - 2021-2 - Gabarito - Organização de ComputadoresDocumento7 páginasAPX3 - 2021-2 - Gabarito - Organização de ComputadoresDBM 3/20 COLUBANDEAinda não há avaliações

- Lista de Exercício - P2 - Controle - Linear - IDocumento6 páginasLista de Exercício - P2 - Controle - Linear - IVinicius RamosAinda não há avaliações

- Microcontroladores 2 Exercicios Macro e Microarquitetura v2Documento4 páginasMicrocontroladores 2 Exercicios Macro e Microarquitetura v2Marcelo LimaAinda não há avaliações

- Avaliação Final - Trabalho - Modelagem A Projeto - InTRODUÇÃO A TEORIA de CONTROLEDocumento4 páginasAvaliação Final - Trabalho - Modelagem A Projeto - InTRODUÇÃO A TEORIA de CONTROLEWermersonAinda não há avaliações

- Lista1 (1)Documento7 páginasLista1 (1)Tiago Rodrigues MendonçaAinda não há avaliações

- Instrumentação e controle em processos industriaisDocumento19 páginasInstrumentação e controle em processos industriaisMarcos AfonsoAinda não há avaliações

- 2013 2014-So-Exame Normal PDFDocumento3 páginas2013 2014-So-Exame Normal PDFAlfredo SoldadinhoAinda não há avaliações

- SO 1718 Exame2Documento13 páginasSO 1718 Exame2uxksnsuauunvjuabwbAinda não há avaliações

- AI Ex01 1617Documento2 páginasAI Ex01 1617José PedroAinda não há avaliações

- Lista 2 - 2017-02Documento4 páginasLista 2 - 2017-02Wanderson RamosAinda não há avaliações

- CLP-Questões-Técnico-EletrotécnicaDocumento5 páginasCLP-Questões-Técnico-EletrotécnicabetoAinda não há avaliações

- Controle de MIT com CLP WEG Clic02Documento17 páginasControle de MIT com CLP WEG Clic02Victor Tavares AlvarengaAinda não há avaliações

- Respostas SIMULADO Linguagem de Programação - PythonDocumento17 páginasRespostas SIMULADO Linguagem de Programação - PythonCézar100% (1)

- SistemaControleMediçãoDocumento8 páginasSistemaControleMediçãoJunior LoveAinda não há avaliações

- IntroduçãoDocumento7 páginasIntroduçãocleuberrjAinda não há avaliações

- PRIMEIRA AVALIAÇÃO OAC 2022 ManhãDocumento4 páginasPRIMEIRA AVALIAÇÃO OAC 2022 ManhãAllan O BirutaAinda não há avaliações

- Sistemas Digitais: Lista de Exercícios 1Documento4 páginasSistemas Digitais: Lista de Exercícios 1w ifAinda não há avaliações

- Tarefas 1 DriversDocumento3 páginasTarefas 1 DriversDj-Dénny DjrAinda não há avaliações

- Laboratorio de Sistemas DigitaisDocumento32 páginasLaboratorio de Sistemas DigitaisEduardo Sanches SalesAinda não há avaliações

- Conjunto de Instrucoes PIC 16F877ADocumento36 páginasConjunto de Instrucoes PIC 16F877ANando100% (1)

- Exercícios AC1 MIPSDocumento7 páginasExercícios AC1 MIPSCristina Cunha0% (1)

- Redes Wilson Lab - 2014Documento48 páginasRedes Wilson Lab - 2014marco gomesAinda não há avaliações

- Lista 3Documento3 páginasLista 3renan correa de.mouraAinda não há avaliações

- Projeto e simulação de compensadores por avanço e atraso de faseDocumento8 páginasProjeto e simulação de compensadores por avanço e atraso de fasecaAinda não há avaliações

- ACL NAT Questoes Padrao CCNADocumento14 páginasACL NAT Questoes Padrao CCNAJose Soares50% (2)

- TP2 AtmDocumento2 páginasTP2 AtmBrenda CarolineAinda não há avaliações

- Avaliação de ACL em roteador CiscoDocumento5 páginasAvaliação de ACL em roteador CiscoLeonardo BorgesAinda não há avaliações

- 0w94ijsf 11Documento6 páginas0w94ijsf 11Twi tchAinda não há avaliações

- 09 CFRM CompDocumento8 páginas09 CFRM CompNobre NetoAinda não há avaliações

- 6.2 Trabalho Pratico BIPDocumento13 páginas6.2 Trabalho Pratico BIPAnderson Job LoefflerAinda não há avaliações

- Programação I - Testes, Condições e CiclosDocumento13 páginasProgramação I - Testes, Condições e CiclosJesse FreitasAinda não há avaliações

- Manual do usuário do programa EstacaDocumento24 páginasManual do usuário do programa EstacaEduardo FonsecaAinda não há avaliações

- Prancha Do ProjetoDocumento1 páginaPrancha Do ProjetoJader Lucas PerezAinda não há avaliações

- Modos Gregos DominadoDocumento11 páginasModos Gregos DominadoLeo MoraisAinda não há avaliações

- Guia Meu Espaco CorretorDocumento10 páginasGuia Meu Espaco CorretorJader Lucas PerezAinda não há avaliações

- DILSONDocumento1 páginaDILSONJader Lucas PerezAinda não há avaliações

- Apostila IfmsDocumento40 páginasApostila IfmsDiego CorreiaAinda não há avaliações

- Sistemas de Controle e Automação 2013 - Tema 3 - Erro de Regime EstacionárioDocumento17 páginasSistemas de Controle e Automação 2013 - Tema 3 - Erro de Regime EstacionárioJader Lucas PerezAinda não há avaliações

- PowerWorld Simulation (Transmission Line (Documento1 páginaPowerWorld Simulation (Transmission Line (Jader Lucas PerezAinda não há avaliações

- Direito Noturno 2013-1Documento10 páginasDireito Noturno 2013-1Jader Lucas PerezAinda não há avaliações

- TCC F6 Formulario de Acompanhamento Individual Do Aluno de TCCDocumento2 páginasTCC F6 Formulario de Acompanhamento Individual Do Aluno de TCCJader Lucas PerezAinda não há avaliações

- Saxofone - Partitura - Clássicos - 18 Solos para Saxofone EruditoDocumento32 páginasSaxofone - Partitura - Clássicos - 18 Solos para Saxofone EruditoJader Lucas Perez100% (3)

- A Central TelefônicaDocumento5 páginasA Central TelefônicaJader Lucas PerezAinda não há avaliações

- Java Web Start - Grupo de Usuários JavaDocumento8 páginasJava Web Start - Grupo de Usuários JavaEdmar BregagnoliAinda não há avaliações

- Persistência de dados com Java e Hibernate AnnotationsDocumento37 páginasPersistência de dados com Java e Hibernate AnnotationsJadson Souza FariaAinda não há avaliações

- Energia Vários MEE - GNF PDFDocumento317 páginasEnergia Vários MEE - GNF PDFsilveira_manuelAinda não há avaliações

- Wellcare WXS-B200Documento3 páginasWellcare WXS-B200Rafael MarquesAinda não há avaliações

- TV 2Documento24 páginasTV 2Dionei CardozoAinda não há avaliações

- Diagrama Elétrico SpeeduinoDocumento2 páginasDiagrama Elétrico SpeeduinoBinotto PerformanceAinda não há avaliações

- QUESTAO Potenciacao 8 CDocumento7 páginasQUESTAO Potenciacao 8 CReinaldo JúniorAinda não há avaliações

- VermiculitaDocumento4 páginasVermiculitaJoão DantasAinda não há avaliações

- Windows 7 aplicativos e ferramentasDocumento6 páginasWindows 7 aplicativos e ferramentasmirandespinheiroAinda não há avaliações

- Catalogo Peças Nmax-160-Abs-2020 - B554Documento61 páginasCatalogo Peças Nmax-160-Abs-2020 - B554RegisBarbieri100% (2)

- Introdução A IHCDocumento26 páginasIntrodução A IHCSidney MoreiraAinda não há avaliações

- Controlador FE50RP: manual de operação otimizado paraDocumento8 páginasControlador FE50RP: manual de operação otimizado paraFernando CarvalhoAinda não há avaliações

- Hábitos e resíduos para reciclarDocumento9 páginasHábitos e resíduos para reciclarhelofAinda não há avaliações

- Grupo 5T-Trabalho Ciclo CombinadoDocumento15 páginasGrupo 5T-Trabalho Ciclo Combinadohugod1982Ainda não há avaliações

- Data Schit RELÉ MKB - 3 L RoHS.Documento3 páginasData Schit RELÉ MKB - 3 L RoHS.Otavio CastroAinda não há avaliações

- Fiat Marea Weekend orçamentoDocumento1 páginaFiat Marea Weekend orçamentoTruckPartsAinda não há avaliações

- Garantia e Controle de QualidadeDocumento14 páginasGarantia e Controle de QualidadeRomulo CeleriAinda não há avaliações

- Detecção de descontinuidades em soldas e processos de fabricaçãoDocumento3 páginasDetecção de descontinuidades em soldas e processos de fabricaçãoWilker Frazao100% (1)

- Arduino - Aula 1 - Atividade 6 Trabalhando Com LED e Lei de Ohm - Alura - Cursos Online de TecnologiaDocumento3 páginasArduino - Aula 1 - Atividade 6 Trabalhando Com LED e Lei de Ohm - Alura - Cursos Online de TecnologiaGaby DudaAinda não há avaliações

- Requerimento Anexo I TaurusDocumento1 páginaRequerimento Anexo I Taurusanon-491249100% (2)

- Manual HabilDocumento470 páginasManual HabilDivanil Marins100% (1)

- 4.2.1 - 4.2.2. Escoamento de Interno - Tubos e DutosDocumento71 páginas4.2.1 - 4.2.2. Escoamento de Interno - Tubos e Dutosricardaum100% (1)

- Calculando Medidas-PneusDocumento3 páginasCalculando Medidas-PneusPHRFragosoAinda não há avaliações

- Frações de solo e densidadesDocumento13 páginasFrações de solo e densidadesAfonso PraganaAinda não há avaliações

- Contemporary Translation Theories: 2nd Revised Edition, by Edwin Gentzler. Clevedon: Multilingual Matters, 2001.Documento4 páginasContemporary Translation Theories: 2nd Revised Edition, by Edwin Gentzler. Clevedon: Multilingual Matters, 2001.Vigvald NTAinda não há avaliações

- Catálogo de eixos de comando de válvulas IndecoDocumento1 páginaCatálogo de eixos de comando de válvulas IndecoCAIOELEUTERIOCEOAinda não há avaliações

- Requisito 10 - Melhoria - Blog Da QualidadeDocumento4 páginasRequisito 10 - Melhoria - Blog Da QualidadeNatalícia AzevedoAinda não há avaliações

- Hermenêutica - Portfólio de Apoio (3NA)Documento11 páginasHermenêutica - Portfólio de Apoio (3NA)Douglas FrancoAinda não há avaliações

- Gerada em 22/11/2022 11:04:54: GRRF - Guia de Recolhimento Rescisório Do FGTSDocumento1 páginaGerada em 22/11/2022 11:04:54: GRRF - Guia de Recolhimento Rescisório Do FGTSProfessora Andreia Marqueto100% (1)