Escolar Documentos

Profissional Documentos

Cultura Documentos

Arquivo 283

Enviado por

Anildo Eldivar De Oliveira SarmentoTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Arquivo 283

Enviado por

Anildo Eldivar De Oliveira SarmentoDireitos autorais:

Formatos disponíveis

RETIFICADOR ELEVADOR/ABAIXADOR ISOLADO DE ESTGIO NICO

COM CORREO DO FATOR DE POTNCIA

Janderson Duarte, Leandro Michels, Cassiano Rech e Marcello Mezaroba

Ncleo de Processamento de Energia Eltrica - nPEE Departamento de Engenharia Eltrica

Universidade do Estado de Santa Catarina UDESC - CCT

Campus Universitrio Prof. Avelino Marcante s/n Joinville/SC - Brasil

CEP 89223-100 Telefone (47) 4009-7844

E-mails: janderson_duarte@yahoo.com.br, michels@ieee.org, cassiano@ieee.org, mezaroba@joinville.udesc.br

Resumo Este artigo apresenta um retificador de

corrente isolado de estgio nico com correo do fator

de potncia. O conversor proposto pode operar como

abaixador ou elevador de tenso, dependendo dos nveis

da tenso de entrada e da tenso de sada. Este artigo

apresenta a anlise terica do conversor, bem como,

resultados experimentais baseado em um prottipo de 3,5

kW.

Palavras-Chave Correo do Fator de Potncia,

Flyback - Full Bridge, Retificador de Corrente.

SINGLE-STAGE ISOLATED HIGH

POWER FACTOR STEP-UP/STEP-DOWN

CONVERTER

Abstract This paper presents a single-stage isolated

current rectifier with power factor correction, based on

full bridge and flyback topologies. The proposed

converter can operate as a step-down or a step-up

converter, according to the input and output voltage

levels. This paper presents the theoretical analysis of the

converter as well as experimental results based on a

3.5 kW prototype.

Keywords Current fed rectifier, full bridge flyback,

power factor correction.

I. INTRODUCO

Conversores CA-CC isolados com correo do fator de

potncia tm sido largamente utilizados em equipamentos

eletrnicos que necessitam de correo do fator de potncia e

isolao galvnica. Estes conversores so uma alternativa

para os tradicionais retificadores isolados a diodo que

drenam correntes pulsadas das fontes CA. Estes formatos de

corrente introduzem harmnicas de corrente indesejveis,

distores de tenso e interferncias eletromagnticas na rede

eltrica [1]. Filtros passivos podem ser utilizados para

amenizar estes problemas com alta eficincia e baixo custo,

mas os mesmos so volumosos e pesados devido

principalmente ao tamanho dos elementos magnticos e

capacitores, que operam com a freqncia da rede [2].1

A soluo convencional para se conseguir elevado fator de

potncia e isolao galvnica a utilizao de um conversor

1

Artigo submetido em 12/11/2009. Reviso em 12/04/2010. Aceito para

publicao em 13/04/2010 por recomendao do editor Fernando L. M.

Antunes.

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

de dois estgios, composto por um conversor PFC (Power

Factor Correction) pr-regulador elevador e um conversor

CC-CC isolado [3]-[18]. Entretanto, possvel reduzir custos

e volume utilizando um conversor em estgio nico, com

correo do fator de potncia e isolao galvnica [19]- [33].

Um possvel conversor isolado estgio nico para

correo do fator de potncia o Flyback - Push-Pull isolado

com entrada em corrente [29]. Este conversor isolado possui

alto fator de potncia e pode operar como elevador ou

abaixador. Entretanto, devido caracterstica Push-Pull, este

conversor tem algumas desvantagens que limitam sua

aplicao somente para baixas potncias: problema de

saturao do transformador e tenses elevadas nas chaves.

Outra configurao estgio nico o conversor FullBridge - Boost [30]-[33]. Este conversor possui isolao

galvnica em alta freqncia e alto fator de potncia. Porm,

as chaves so submetidas a altos nveis de tenso quando elas

so bloqueadas por circuitos de proteo, no caso de falhas.

Alm disso, esta topologia somente opera como elevador de

tenso.Como uma tentativa de superar estas desvantagens,

este artigo prope um retificador de corrente isolado do tipo

Full-Bridge Flyback com correo do fator de potncia. As

principais caractersticas do conversor proposto so:

conversor estgio nico;

alto fator de potncia;

isolao galvnica;

freqncia de chaveamento constante;

operao como elevador ou abaixador;

possibilidade de operar com altos nveis de potncia;

no necessita de um circuito auxiliar para reduzir a

corrente de partida (inrush).

II. TOPOLOGIA PROPOSTA

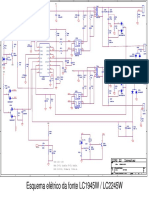

A Figura 1 mostra um circuito simplificado do conversor

proposto. O conversor composto pelos diodos retificadores

da rede (D1, D2, D3 e D4), um indutor acoplado flyback (LC),

quatro chaves principais (S1, S2, S3 e S4), um transformador

full-bridge (T1), dois diodos flyback (D5 e D6), quatro diodos

full-bridge (D7, D8, D9 e D10) e um capacitor de filtro de

sada (Co).

A relao de transformao de ambos os componentes

magnticos igual (N:1), como ilustrado na Figura 1.

Conseqentemente, a tenso de sada referida para o primrio

do transformador dada por:

(1)

Vo ' = NVo

Este conversor ser analisado em modo de conduo

contnua (CCM). Para este modo de conduo existem dois

67

diferentes modos de operao, dependendo dos nveis de

tenso de entrada e de sada, como mostrado na Figura 2.

SF

:1

PF

1

ac

in

:1

3

10

Fig. 1 Conversor proposto.

Fig. 2 Modos de operao do conversor.

(a) Elevador. (b) Elevador/abaixador.

O conversor opera no modo elevador quando a tenso de

entrada retificada menor que a tenso de sada referida para

o primrio do transformador (Vo). O conversor opera no

modo abaixador quando a tenso de entrada maior que Vo.

Considerando que a freqncia de chaveamento muito

maior do que a freqncia da referncia, a tenso de entrada

pode ser assumida como constante para um ciclo de

chaveamento. Em conseqncia, neste intervalo de tempo, o

conversor proposto pode ser analisado como um conversor

CC-CC.

A. Operao em Modo elevador

Neste modo de operao, as chaves principais operam

com razo cclica 0,5 < D 1,0, onde D definido como:

t

D= c

(2)

Ts

onde tc o tempo de conduo das chaves principais e Ts o

perodo de chaveamento.

As etapas de operao so apresentadas como segue.

Primeira Etapa (0 t tc TS/2): Durante esta etapa

todas as chaves esto conduzindo e a tenso de entrada

aplicada no primrio do indutor, como pode ser observado na

Figura 3(a). A corrente iLPF cresce linearmente e LC armazena

energia. No h transferncia de energia da fonte de entrada

para a carga, e somente o capacitor de sada fornece energia

para a carga.

Segunda Etapa (tc TS/2 t TS/2): Nesta etapa,

apresentada na Figura 3(b), as chaves S2 e S3 esto

bloqueadas e as chaves S1 e S4 ainda esto conduzindo. A

tenso no primrio do indutor (Vin NVo)/2 e a corrente no

primrio do indutor decresce linearmente. Nesta etapa, a

corrente que circula no primrio do indutor e no primrio do

transformador a mesma. Similarmente, a corrente em

ambos os enrolamentos secundrios a mesma. As correntes

68

de primrio e secundrio esto relacionadas pela relao de

transformao, que deve ser a mesma para o indutor

acoplado e para o transformador, como descrito

anteriormente. Durante esta etapa, h transferncia de

energia da fonte de entrada para a sada atravs de D5 e D10.

Terceira Etapa (TS/2 t tc): Todas as chaves esto

conduzindo novamente e, portanto, esta etapa idntica a

primeira etapa.

Quarta Etapa (tc t TS): Nesta etapa, apresentada na

Figura 3(c), as chaves S1 e S4 esto bloqueadas e as chaves S2

e S3 ainda esto conduzindo. A tenso no primrio do indutor

(Vin NVo)/2 e a corrente no primrio do indutor decresce

linearmente. A corrente nos enrolamentos primrios do

indutor acoplado e do transformador a mesma, bem como a

corrente em seus respectivos enrolamentos secundrios.

Durante esta etapa, h transferncia de energia da fonte de

entrada para a sada atravs de D6 e D9.

As principais formas de onda para o modo elevador so

apresentadas na Figura 4. importante mencionar que a

definio de modo de conduo relacionada com a corrente

de magnetizao iLC=iLpf + iLsf. Como pode ser observado na

Figura 4, a corrente de magnetizao em Lc contnua, mas a

corrente de entrada (iLpf ) apresenta uma descontinuidade no

seu formato.

B. Operao no Modo Abaixador

Neste modo, as chaves principais operam com uma razo

cclica 0 < D 0.5. As etapas de operao para este modo

so analisadas como segue.

(a)

(b)

(c)

Fig. 3 Etapas de operao no modo elevador.

(a) Primeira e Terceira etapas. (b) Segunda etapa. (c) Quarta etapa.

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

c- s/2

LPF

m

M/2

in

m/2

0

in-

LPF

)/2

atravs do transformador, D8 e D9, como mostrado na Figura

5(c).

Quarta Etapa (tc + TS/2 t TS): A quarta etapa

idntica a segunda etapa.

As principais formas de onda para o modo abaixador

podem ser vistas na Figura 6. Observe que a definio de

modo de conduo tambm relacionada a corrente de

magnetizao em Lc. Neste modo de operao a corrente de

magnetizao contnua, mas a corrente de entrada

descontnua.

LC

LC

III. ANLISE EM REGIME PERMANENTE

0

(-

in+

)/2

LSF

0

(

in+

m/2

M/2

in/

)/2

M/2

S1

in+

)/2

o

o

LS

in-

M/2

m/2

LS

0

(-

M/2

m/2

m/2

M/2

LP

)/2

)/2

m/2

)/

in-

-1/3(

o+ in

(4)

Como apresentado na Figura 2, a transio entre os modos

elevador e abaixador ocorre quando a tenso de entrada

retificada atinge o valor da tenso de sada referida para o

lado primrio.

D7

)/2

Vo

2D

=

V in

N

M/2

2

(

Por outro lado, o ganho CC de tenso no modo abaixador

:

G dow n =

LP

0

(- in( in+

m/2

S1

0

(

O ganho CC de tenso no modo elevador de operao :

V

D

(3)

Gup = o =

Vin N (1 D)

LSF

D7

)

-

o

M/2

m/2

D6

D6

(- in- o )/2

(-4 in- o)/

3

M/2

0

(

in-

(-

in-

m/2

D9

(a)

o)/3

o

D9

)/2

0

c- s/2

s/2

Fig. 4 Formas de onda tericas para o modo elevador.

Primeira Etapa (0 t tc): Durante esta etapa,

apresentada na Figura 5(a), as chaves S1 e S4 esto

conduzindo e S2 e S3 esto bloqueadas. A tenso no primrio

do indutor (Vin NVo) e a corrente iLPF cresce linearmente.

H transferncia de energia da fonte de entrada para a sada

atravs do transformador, D7 e D10.

Segunda Etapa (tc t TS/2): Nesta etapa, todas as

chaves esto bloqueadas, como ser observado na Figura 5(b).

O secundrio do indutor assume a corrente, e fornece energia

para a sada atravs de D5, D6, D9 e D10. A tenso aplicada no

secundrio do indutor Vo e a corrente decresce

linearmente.

Terceira Etapa (TS/2 t tc + TS/2): Durante esta etapa,

as chaves S2 e S3 esto conduzindo, e S1 e S4 ainda esto

bloqueadas. Novamente, a tenso no primrio do indutor

(Vin NVo) e a corrente iLPF cresce linearmente. H

transferncia de energia da fonte de entrada para a sada

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

(b)

(c)

Fig. 5 Etapas de operao no modo abaixador.

(a) Primeira etapa. (b) Segunda e quarta etapas. (c) Terceira etapa.

69

A Figura 8 mostra o comportamento da razo cclica para

meio perodo da rede eltrica, considerando N = 1, Vo = 200 V

e VP = 311 V. Portanto, pode ser observado que a transio

entre o modo elevador e abaixador do conversor suave.

4

c

2

s/2

Ganho (G) 10

0

in-

9

M

LPF

LPF

o

LC

LC

4

3

0

LSF

in+

LSF

in/

Modo Abaixador

G down =2D/N

Modo Elevador

G up =D/N(1-D)

0.1

0.2

0.3

0.4

0.5

0.6

Razo Cclica (D)

0.7

0.8

0.9

Fig. 7 Ganho de tenso CC versus razo cclica.

o

o)/2

o

S1

S1

D (wt)

1

0.9

LP

o

0.8

LP

Modo Elevador

0.7

0.6

M

o

LS

0.5

LS

0.4

m

0.3

M

o

0.1

D7

IV. CONSIDERAES DE PROJETO

D9

M/2

/2

D6

0

D6

o

in/

s/2

s/2

Fig. 6 Formas de onda tericas para o modo abaixador.

De (3) e (4) possvel verificar que a transio ocorre

quando a razo cclica atinge 0,5, como pode ser visto na

Figura 7, a qual mostra a curva do ganho CC de tenso para

ambos os modos.

Alm disso, utilizando (3), a razo cclica para o modo

elevador pode ser estimada da seguinte expresso:

Vo '

(5)

D(t ) =

Vo '+ VP sin(t )

onde VP o valor de pico da tenso de entrada e 1 t 2.

Por outro lado, utilizando (4), o comportamento da razo

cclica para o modo abaixador pode ser obtida de:

Vo '

(6)

D (t ) =

2 VP sin(t )

onde 0 t < 1 ou 2 < t .

70

/2

(wt)

M/2

in/

Fig. 8 Razo cclica para meio ciclo da rede eltrica.

D9

Modo Abaixador

0.2

D7

Os principais parmetros a serem projetados para o

conversor proposto so a relao de transformao do

transformador e do indutor acoplado, a indutncia do indutor

acoplado e a capacitncia de sada.

Devido ao ganho de tenso CC deste conversor, a relao

de transformao pode variar em uma grande faixa, desta

forma a relao de transformao pode ser calculada em

funo de diferentes especificaes. Uma tima relao de

transformao pode ser calculada de forma a minimizar as

perdas nas chaves principais ou limitar a mxima tenso

sobre elas. Como a otimizao no o principal objetivo

deste artigo, uma relao de transformao unitria (N=1) foi

adotada para o transformador e o indutor acoplado.

Alm disso, a indutncia LC deve ser determinada para

limitar a mxima ondulao de corrente no indutor acoplado

iLC. A mxima ondulao na corrente de magnetizao iLC

ocorre no modo abaixador, de modo que a indutncia pode

ser calculada por (7), utilizando a tenso aplicada no

primrio do indutor acoplado neste modo de operao:

LC =

0,5VPTS

2iLC

(7)

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

Alm disso, a capacitncia de sada pode ser calculada em

funo da mxima ondulao da tenso de sada permitida

utilizando a seguinte expresso:

Co =

Po

4 f rVo Vo

(8)

onde Po a potncia de sada e fr a freqncia da tenso de

entrada.

V. VERIFICAO EXPERIMENTAL

A. Descrio do prottipo

Um prottipo de um retificador de corrente isolado FullBridge Flyback foi implementado em laboratrio para

verificar o desempenho do conversor proposto sob condies

prticas. O prottipo implementado apresentado na Figura

9, e seu diagrama esquemtico mostrado na Figura 10.

S2 e S3. Os padres de modulao para ambos os modos so

apresentados na Figura 11.

A estratgia de controle utilizada para este conversor o

controle por valores mdios instantneos [35]-[37],

utilizando a corrente de entrada como parmetro de controle.

O conversor possui controle da corrente de entrada e da

tenso de sada. Um diagrama de blocos simplificado da

estratgia de controle tambm apresentado na Figura 10. A

sada do controlador de tenso multiplicada por uma

amostra da tenso da rede retificada e seu resultado a

referncia para a malha de corrente. O controlador de

corrente fora a corrente de entrada a seguir a referncia de

corrente, que est em fase com a tenso de entrada retificada.

A sada do controlador de tenso aumenta ou diminui a

amplitude da referncia de corrente de acordo com o erro de

tenso, de forma que a tenso CC de sada regulada de

acordo com o valor de referncia de tenso.

As especificaes de projeto deste prottipo so

apresentadas na TABELA 1 e os principais componentes

utilizados no prottipo so especificados na TABELA 2. O

sistema de controle foi implementado em no DSP

TMS320F2812 da Texas Instruments. Circuitos de drivers

SKHI20OPA da Semikron foram utilizados e uma placa de

interface foi includa para adaptar os sinais do DSP para o

circuito de potncia.

TABELA 1

Especificaes de projeto

Po = 3,5 kW

Tenso de sada

Vin = 311sin(t) V

Tenso de entrada

Ondulao mxima da tenso de

sada

Freqncia de entrada

Vo = 4 V

fr = 60 Hz

fs = 75 kHz

Fig. 9 Prottipo desenvolvido.

= 90 %

Freqncia de chaveamento

Ondulao mxima da corrente

de entrada

Eficincia

N = 1

Relaes de transformao

iLC = 8,88 A

Para a implementao foi necessria a incluso de

circuitos de grampeamento do tipo RCD, ou seja, uma

associao de resistores, capacitores e diodos que visam

manter a tenso dos semicondutores dentro do limite seguro

de operao, conforme pode ser visto na Figura 10. Tambm

foi necessrio um circuito de grampeamento para limitar a

tenso em todos os semicondutores, por que a energia

armazenada nas indutncias de disperso do transformador e

do indutor acoplado causa elevados transientes de tenso nos

semicondutores. Uma vez que este conversor opera com

elevados nveis de potncia, a energia armazenada nas

indutncias de disperso elevada. Contudo, como esta

energia no tem um caminho natural para se dissipar,

necessrio utilizar circuitos de grampeamento de tenso. O

snubber de Undeland [34] foi escolhido para limitar a tenso

nas chaves, e circuitos grampeadores RCD individuais para a

proteo dos diodos, como apresentado na Figura 10.

Os sinais de comando das chaves principais so obtidos

atravs da comparao entre o sinal de controle e dois sinais

dente-de-serra defasados entre eles de 180, como ilustrado

na Figura 10. Os sinais dente-de-serra so levados entrada

de dois diferentes comparadores. As outras entradas dos

comparadores so conectadas ao mesmo sinal de controle. A

sada de um comparador o sinal de comando de S1 e S4

enquanto a sada do outro comparador o sinal de comando

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

Potncia de sada

Vo = 400 V

TABELA 2

Parmetros de circuito e descrio dos componentes

S1 , S2 , S3 , S4

D5, D6, D7, D8,

D9, D10

D1, D2, D3, D4

Chaves: IRGP50B60PD

Diodos: HFA16TB120

Ponte retificadora: SK50B08

Co

Capacitor eletroltico: 6 x 470F/400V

LF

Indutor toroidal: P de ferro, L=100H, 32 espiras

Cf

Indutor

acoplado

Capacitor de polipropileno: 5F

Indutor de ferrite: IP6-EE65/91, L=200H, 16

espiras, indutncia de disperso total = 12H

Transformador de ferrite: IP6-EE65/91, 10 espiras,

indutncia de disperso total = 4H

Transformador

Dsnu1-Dsnu6 and

Dund1-Dund4

Cund1,Cund2

Diodos: MUR4100

Capacitor de polipropileno : 4,7nF

Rsnu3-Rsnu6

Resistor: 90k/3W

Rsnu1, Rsnu2

Resistor: 156k/3W

Cgr

Capacitor eletroltico : 73 F/750V

Rgr

Resistor: 3,3k/600W

71

RCD

RCD

gr

RCD

RCD

gr

und1

und2

snu1

snu2

snu4

snu3

3.3k 73uF

und1

und3

c

1:1

4.7nF

snu1

und2

4.7nF

und4

snu1

1.2nF 156k

snu2

6

snu2

1.2nF 156k

snu3

7

snu3

snu4

snu4

8

1.2nF 90k

1.2nF 90k

1:1

15.6

100uH

RCD

5uF

11uF

3

RCD

2.9mF

1

snu6

snu5

snu5

snu5

1.2nF 90k

1

0

snu6

snu6

1.2nF 90k

Driver

1

PWM

+

+

-

Controlador

de tenso

Controlador

de corrente

1, 4

1

2

2, 3

3

4

DSP/ C

Fig. 10 Diagrama esquemtico do prottipo e estrutura do controle.

corrente de entrada de 3,6% e o fator de potncia de

entrada 0,99.

A Figura 14 mostra a tenso na chave S1 e a corrente no

primrio do indutor. Pode-se observar o formato descontnuo

da corrente no primrio do indutor acoplado, e que sua

freqncia o dobro da freqncia de chaveamento.

Tambm pode-se notar a alta tenso na chave durante seu

bloqueio devido as indutncias de disperso nos elementos

magnticos, justificando o uso de circuitos grampeadores.

Alm disso, o desempenho do conversor proposto foi

analisado para uma tenso de sada menor.

Fig. 11 Estratgia de modulao PWM.

a)modo elevador; b)modo abaixador

B. Resultados Experimentais

A Figura 12 mostra as formas de onda da tenso de

entrada e a corrente de entrada com uma carga resistiva de

58,6 , uma tenso de sada de 400V e tenso nominal de

entrada. O valor da carga foi escolhido de forma que o

conversor opere com potncia nominal de entrada e tenso

nominal de sada. O espectro harmnico da corrente de

entrada mostrado na Figura 13, cujos valores so

comparados com limites impostos pela norma IEC61000-3-2

(classe A) [1]. Neste ponto de operao, o conversor opera

somente no modo elevador e todas as harmnicas de corrente

atendem as especificaes dadas em [1], como pode ser visto

na Figura 14. A taxa de distoro harmnica total (THD) da

72

Fig. 12 Tenso de entrada/sada e corrente de entrada

(100 V/div, 10 A/div, 2.5 ms/div).

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

Fig. 13 Espectro de harmnicas da corrente de entrada para o modo

elevador e os limites da norma IEC61000-3-2 Classe A.

Fig. 16 Espectro de harmnicas da corrente de entrada para o modo

elevador/abaixador e os limites da norma IEC61000-3-2 Classe A.

Fig. 14 Corrente no primrio do indutor e tenso na chave S1

(50 V/div, 5 A/div, 2.5 s/div).

Fig. 17 Corrente de entrada e tenso de sada

(10A/div, 5V/div, 50ms/div).

Fig. 15 Tenso de entrada e sada e corrente de entrada

(100 V/div, 20 A/div, 2.5 ms/div).

Fig. 18 Corrente de entrada e tenso de sada

(10A/div, 5V/div, 50ms/div).

Utilizando uma tenso de sada de 200V o conversor

proposto opera em ambos os modos (modos elevador e

abaixador). A resistncia de carga foi ajustada para 30,5 .

O valor da resistncia de carga escolhida foi utilizando o

critrio de manter a corrente nos diodos de sada dentro do

valor projetado. A Figura 15 mostra a tenso de entrada e

sada e a corrente de entrada para este ponto de operao.

A Figura 16 mostra o espectro harmnico da corrente de

entrada apresentada na Figura 15 e comparada com os

limites especificados pela norma IEC61000-3-2. Neste caso,

A THD da corrente de entrada 7,7% e o fator de potncia

de entrada 0,98. As harmnicas 13, 15 e 19 no atendem os

limites da norma IEC61000-3-2 Classe A.

Como pode ser observado na Figura 15 e Figura 16, a

THD da corrente de entrada aumenta quando o conversor

opera no modo abaixador. A corrente de entrada distorcida

por que parte da energia armazenada no primrio do indutor

acoplado, na primeira e terceira etapas, no transferida para

o secundrio do indutor acoplado nas outras etapas. Isto

ocorre por que existe um caminho de menor impedncia

atravs do snubber de Undeland. Conseqentemente, a

escolha do snubber de Undeland para este conversor no foi

eficiente para o modo abaixador.

A Figura 17 mostra a corrente de entrada e a tenso de

sada durante uma variao de carga de 244 para 122 . A

tenso de sada foi medida no modo Ca para melhor

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

73

visualizao. A Figura 18 apresenta as mesmas formas de

onda para uma mudana de carga de 122 para 244 .

Ambos os resultados mostram que o sistema em malha

fechada apresentou-se satisfatrio.

Os resultados experimentais demonstram que as

indutncias de disperso tm uma significante influncia na

eficincia do conversor. A eficincia de 75% foi obtida

devido a tecnologia utilizada para a construo do indutor

acoplado e do transformador. Algumas sugestes para

resolver estes problemas em trabalhos futuros so

apresentadas: 1) implementar um conversor isolado para

regenerar a energia armazenada no capacitor Cgr do snubber

de Undeland, transferindo esta energia para a sada, ou 2)

utilizar transformador e indutor acoplado planar com baixa

indutncia de disperso [38] e utilizar circuitos grampeadores

RCD em cada chave.

VI. CONCLUSES

Das anlises e resultados apresentados neste artigo

demonstrado que o retificador de corrente isolado full-bridge

flyback satisfaz as especificaes propostas, que so:

conversor estgio nico, alto fator de potncia, isolao

galvnica, componentes magnticos operando em alta

freqncia, controle da tenso de sada, corrente de pr-carga

controlvel, operao como elevador ou abaixador e nmero

reduzido de chaves (custo cerca de 40% menor que uma

topologia Boost mais um Full-Bridge). Adicionalmente, a

modulao e a estratgia de controle so simples e podem ser

implementadas utilizando processos tanto analgicos quanto

digitais.

Comparando o conversor proposto com o conversor

Flyback - Push-Pull pode-se verificar que o conversor

proposto possui menores esforos de tenso nas chaves, pode

operar com nveis maiores de potncia e o transformador no

possui problemas de saturao. Alm disso, comparando-o

com o conversor Full-Bridge Boost possvel observar que

a topologia proposta tambm pode operar como um

conversor abaixador e as chaves no so submetidas a altos

nveis de tenso quando todas as chaves so bloqueadas, pois

existe um caminho natural de circulao da corrente do

indutor atravs de seu enrolamento secundrio.

Trabalhos futuros iro explorar solues para melhorar a

eficincia do conversor, que baixa devido s elevadas

indutncias de disperso existentes no circuito. Os autores

acreditam que a topologia apresentada pode ser uma

alternativa vivel para a utilizao como estgio de entrada

isolado em fontes de alimentao CA e sistemas ininterruptos

de energia.

REFERNCIAS

[1] Norma internacional, Electromagnetic compatibility

(EMC) - Part 3-2 - Limits for harmonic current

emissions (equipment input current up to and including

16 A per phase), IEC Standard 61000-3-2, 2005.

[2] N. Takeuchi, K. Matsui, F. Ueda, H. Mori, A novel

PFC circuit using ladder type filter employing only

passive devices, in IEEE APEC 2008, pp. 1005-1009,

Feb. 2008.

74

[3] K. I. Hwu, Y. T. Yau, An interleaved AC-DC

Converter Based on Current Tracking, IEEE Trans. Ind.

Electron., vol. 56, pp. 1456-1463, May, 2009.

[4] M. Brunoro, J. L. F. Vieira, Fonte de Alimentao CCCC 0-50V/0-10A em Ponte Completa com Controle por

Deslocamento de Fase e Comutao ZVS, Eletrnica

de Potncia Sobraep, vol. 4, n.1, Set. 1999.

[5] C.M. Wang, A new Single-Phase ZCS-PWM Boost

Rectifier with High Power Factor and Low Conduction

Losses, IEEE Trans. Ind. Electron., vol. 53, pp. 500510, Apr. 2006.

[6] D. C. Martins, A. H. de Oliveira, Retificador Trifsico

Isolado com Correo do Fator de Potncia Empregando

o Conversor CC-CC Sepic em Conduo Contnua

Eletrnica de Potncia, vol. 6, n.1, Dez. 2001.

[7] D. C. Martins, M. M. Casaro, I. Barbi, Retificador

Trifsico Isolado com Alto Fator de Potncia Utilizando

o Conversor Zeta no Modo de Conduo Contnua

Eletrnica de Potncia, vol. 6, n.1, Dez. 2001.

[8] E. H. Ismail, Bridgeless SEPIC Rectifier with Unity

Power Factor and Reduced Conduction Losses, IEEE

Trans. Ind. Electron., vol. 56, pp. 1147-1157, Apr. 2009.

[9] F. J. M. de Seixas, I. Barbi, Retificador Trifsico

Isolado em Alta Freqncia e Com Baixa Distoro de

Corrente na Rede Eletrnica de Potncia, vol. 7,

n.1,Nov. 2002.

[10] Y.K. Lo, J.-Y. Lin, S.-Y. Ou, Switching Frequency

Control for Regulated Discontinuous-Conduction-Mode

Boost Rectifiers, IEEE Trans. Ind. Electron., vol. 54,

pp. 760-768, Apr. 2007.

[11] C. H. V. Treviso, L. R. Barbosa, A. A. Pereira, J. B.

Vieira Jr., L. C. Freitas Retificador de 6KW, Fator de

Potncia Unitrio, Trifsico, Comutao no Dissipativa

na Converso CC-CC e Controle Sincronizado em

Freqncia Eletrnica de Potncia, vol. 8, n.1, Jun.

2003.

[12] D. S. Oliveria Jr., R. P. T. Bascop, I. Barbi, C. E. A.

Silva, On the Study of the Dynamics of the ZVS ThreePhase DC/DC Converter Eletrnica de Potncia, vol.

11, n.1, Mar. 2006.

[13] R. P. T. Bascop, D. S. Oliveria Jr., C. G. C. Branco, F.

L. M. Antunes, A High Frequency Transformer

Isolation UPS System with 110V/220V Input Voltage

Eletrnica de Potncia, vol. 11, n.1, Nov. 2006.

[14] F. C. Lee, B. H. Cho, R. B. Ridley, V. Vlatkovic, J. A.

Sabat, Design Considerations for High-Voltage, HighPower, Full-Bridge, Zero-Voltage-Switching PWM

Converter, in IEEE APEC90, pp. 275-184, Mar. 1990.

[15] R. Redl, N. Sokal, L. Balogh, A Novel Soft-Switching

Full-Bridge DC/DC Converter: Analysis, Design

Considerations and Experimental Results at 1.5 kW, 100

kHz, IEEE Trans. Power Electron., vol. 6, pp. 408-418,

Jul. 1991.

[16] J. B. Wang, R. Li, Joe Chen, Efficiency comparison of

the Full Bridge converters in considered magnetic

saturation, in IEEE IECON, pp. 717-722, Nov. 2008.

[17] L. Zhu, A Novel Soft-Commutating Isolated Boost

Full-Bridge ZVS-PWM DC-DC Converter for

Bidirectional High Power Applications, IEEE Trans.

Power Electron., vol. 21, pp. 422-429, Mar. 2006.

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

[18] K. Jin, X. Ruan, M. Yang, M. Xu, A Hibrid Fuel Cell

Power System, IEEE Trans. Ind. Electron., vol. 56, pp.

1212-1222, Apr. 2009.

[19] G. Moschopoulos, A Simple AC-DC PWM Full-Bridge

Converter with Integrated Power-Factor Correction,

IEEE Trans. Ind. Electron., vol. 50, pp. 1290-1297, Dec.

2003.

[20] D. A. Ruiz-Caballero, I. Barbi Um Conversor CC-CC

Flyback-Push-Pull Melhorado Alimentado em Corrente

Eletrnica de Potncia, vol. 4, n.1, Set. 1999.

[21] T.-F. Wu, J.-C. Hung, S.-Y. Tseng, Y.-M. Chen, A

Single-Stage Fast Regulator with PFC Based on an

Asymmetrical Half-Bridge Topology, IEEE Trans. Ind.

Electron., vol. 52, pp. 139-150, Feb. 2005.

[22] F. E. Bisogno, A. R. Seidel, T. B. Marchesan, R. N. do

Prado, Reator Eletrnio para Iluminao Fluorescente

Boost Push-Pull com Alto Fator de Potncia

Empregando um nico Interruptor, Eletrnica de

Potncia, vol. 8, n.1, Jun. 2003.

[23] M. A. Dalla Costa, J. M. Alonso, J. C. Miranda, J.

Garcia, G. D. Lamar, A Single-Stage High-PowerFactor Electronic Ballast Based on Integrated Buck

Flyback Converter to Supply Metal Halide Lamps,

IEEE Trans. Ind. Electron., vol. 55, pp. 1112-1122, Mar.

2008.

[24] H. E. Ismail, J. A. Sabzali, A. M. Al-Saffar, BuckBoost-Type Unity Power Factor Rectifier with Extended

Voltage Conversion Ratio, IEEE Trans. Ind. Electron.,

vol. 55, pp. 1123-1132, Mar. 2008.

[25] A. Fernandez, J. Sebastian, M. M. Hernando, D. G.

Lamar, M. A. Perez de Azpeitia, M. Rodriguez,

Modeling of an AC-to-DC Converter with a SingleStage Power Factor Correction, IEEE Trans. Ind.

Electron., vol. 55, pp. 3064-3076, Aug. 2008.

[26] M. G. Egan, D. L. OSullivan, J. G. Hayes, M. J.

Willers, C. P. Henze, Power-Factor-Corrected SingleStage Inductive Charger for Electric Vehicle Batteries,

IEEE Trans. Ind. Electron., vol. 54, pp. 1217-1226, Apr.

2007.

[27] I. Barbi, D. Ruiz-Caballero, A new ZVS-PWM

clamping mode isolated non pulsating input and output

current DC-to-DC power converter in IEEE

INTELEC99, 20-1, June 5-10, 1999.

[28] A. H. Weinberg, P.R. Boldo, A high power, high

frequency, DC to DC converter for space applications,

in IEEE APEC92, pp. 1140-1147, Jul. 1992.

[29] G. V. T. Bascop, Conversor Flyback-Push-Pull

Alimentado em Corrente com Correo de Fator de

Potncia, Dissertao de Mestrado, Universidade

Federal de Santa Catarina, Brasil, 1996.

[30] A. Mousavi, P. Das, G. Moschopoulos, A ZCS-PWM

Full-Bridge

Boost

Converter

for

Fuel-Cell

Applications,

in

IEEE

APEC

2009,

pp. 459-464, Feb. 2009.

[31] J.-F. Chen, R.-Y. Chen, T.-J Liang, Study and

Implementation of a Single-Stage Current-Fed Boost

PFC Converter With ZCS for High Voltage

Eletrnica de Potncia, vol. 15, no. 2, Maio de 2010

Applications, IEEE Trans. Power Electron., vol. 23, pp.

379-386, Jan. 2008.

[32] L. Zhu A novel soft-commutating Isolated Boost FullBridge ZVS-PWM DC-DC converter for bidirectional

high power applications, IEEE Trans. Power Eletron.,

vol. 21, no. 2, pp. 422-429, Mar. 2006.

[33] P. Em-Sung, J. C. Sung, J. M. Lee, B. H Cho, A softswitching active clamp scheme for isolated full-bridge

boost converter, in IEEE APEC04, vol. 2, pp. 10671070, 2004.

[34] T. M. Undeland, Switching stress reduction in power

transistor converters, in IEEE IAS Annual Meeting, p.

383-391, 1976.

[35] P. Chrin, C. Bunlaksananusorn, Novel Current

Feedforward Average Current Mode Control Technique

to Improve Output Dynamic Performance of DC-DC

Converters, in IEEE PEDS 2007, pp. 1416-1421, Nov.

2007.

[36] W. R. Erickson, D. Maksimovic, Fundamentals of

power electronics, Second Edition, University of

Colorado, 2001.

[37] W. Tang, F. C. Lee, R. B. Ridley, Small-signal

modeling of average current-mode control, in IEEE

APEC92, pp. 747-755, 1992.

[38] E. Maset, A. Ferreres, J. B. Ejea, E. Sanches-Kilders, J.

Jordam, V. Esteve, 5 kW Weinberg converter for

battery discharging in high-power communications

satellites, in IEEE PESC2005, pp. 69-75, 2005.

DADOS BIOGRFICOS

Janderson Duarte, Formou-se em Engenharia Eltrica e

obteve o ttulo de Mestre em Engenharia Eltrica pela

Universidade Estadual de Santa Catarina (UDESC), em 2006

e 2009 respectivamente. Desde 2009 professor colaborador

da Universidade Estadual de Santa Catarina (UDESC).

Leandro Michels, obteve os ttulos de engenheiro eletricista

(2002) e doutor em engenharia eltrica (2006), ambos pela

Universidade Federal de Santa Maria (UFSM), RS, Brasil.

Atuou no perodo de 2005 a 2007 como professor substituto

junto ao Departamento. de Eletrnica e Computao na

mesma universidade, onde atualmente professor adjunto.

membro da SBA e SOBRAEP.

Cassiano Rech. Formou-se em Engenharia Eltrica e obteve

os ttulos de Mestre e Doutor em Engenharia Eltrica pela

Universidade Federal de Santa Maria (UFSM), Santa Maria,

Rio Grande do Sul, Brasil, em 1999, 2001 2005,

respectivamente, onde atualmente atua como professor

adjunto

Marcello Mezaroba, Recebeu os graus de Engenheiro

Eletricista, Mestre e Doutor em Engenharia Eltrica em

1996, 1998 e 2001 respectivamente, pela Universidade

Federal de Santa Catarina (UFSC). Atualmente Professor

Associado no Departamento de Engenharia Eltrica da

Universidade Estadual de Santa Catarina (UDESC)

desenvolvendo atividades de pesquisa junto ao Ncleo de

Processamento de Energia Eltrica (nPEE). membro da

SOBRAEP e do IEEE.

75

Você também pode gostar

- Nicolau Dyrjawoj - M PDFDocumento157 páginasNicolau Dyrjawoj - M PDFAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- M FL 40631501Documento6 páginasM FL 40631501Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Pdvpic (6R1) (1) 29 08 07Documento1 páginaPdvpic (6R1) (1) 29 08 07Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Manual Técnico 9650 9750STS Diágnosticos y Pruebas Hasta SeDocumento2.838 páginasManual Técnico 9650 9750STS Diágnosticos y Pruebas Hasta SeAnildo Eldivar De Oliveira Sarmento100% (18)

- LCD hbtv-4203Documento27 páginasLCD hbtv-4203Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Minicontatores: solução para manobras elétricas compactas e eficientesDocumento40 páginasMinicontatores: solução para manobras elétricas compactas e eficientesAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Manual Condicionador Ar SplitDocumento20 páginasManual Condicionador Ar SplitfabioclAinda não há avaliações

- Philips fwc100 PDFDocumento23 páginasPhilips fwc100 PDFAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Terras PDF Publicacao 17Documento8 páginasTerras PDF Publicacao 17Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Especificações Técnicas LEDs ToshibaDocumento79 páginasEspecificações Técnicas LEDs ToshibaCarlos67% (3)

- Circuito inversor VCC com controle de brilho e entrada de alimentaçãoDocumento12 páginasCircuito inversor VCC com controle de brilho e entrada de alimentaçãoAnildo Eldivar De Oliveira Sarmento100% (1)

- Marcatto CoelhoDocumento10 páginasMarcatto CoelhoInstituto Mauá de TecnologiaAinda não há avaliações

- Antropometria: Necessidade de Constantes Investigações para A Efetiva Contribuição Na Área Da ErgonomiaDocumento14 páginasAntropometria: Necessidade de Constantes Investigações para A Efetiva Contribuição Na Área Da ErgonomiaAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Aplicação da célula de Hull para análise eletroquímicaDocumento8 páginasAplicação da célula de Hull para análise eletroquímicaAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Treinamento técnico em baterias automotivas: principais componentes e funçõesDocumento36 páginasTreinamento técnico em baterias automotivas: principais componentes e funçõesbstrellowAinda não há avaliações

- 55.00 Tinta Pronta Lazzudur Poliuretano Automotivo 26Documento1 página55.00 Tinta Pronta Lazzudur Poliuretano Automotivo 26Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Informações técnicas motores Fiat e DodgePistão MHE-25180E-25180E-25180E-25180Pistão MLP-1829-ATP-1829-ATP-1829-ATP-1829-ATQuantidade dos cilindros4444Ø dos cilindros, mm76,0076,0076,0076,00Curso, mmDocumento20 páginasInformações técnicas motores Fiat e DodgePistão MHE-25180E-25180E-25180E-25180Pistão MLP-1829-ATP-1829-ATP-1829-ATP-1829-ATQuantidade dos cilindros4444Ø dos cilindros, mm76,0076,0076,0076,00Curso, mmredscorpion180% (5)

- Fonte de alimentação controlada por microcontroladorDocumento76 páginasFonte de alimentação controlada por microcontroladormagraodias100% (2)

- Determinacao Potencia MotoresDocumento7 páginasDeterminacao Potencia Motoresvogel_maldonadoAinda não há avaliações

- REGULAGEM DAS ABERTURAS DA BORBOLETA DO AFOGADORDocumento11 páginasREGULAGEM DAS ABERTURAS DA BORBOLETA DO AFOGADORaronroqueAinda não há avaliações

- Metalizacao A Alto Vacuo Brochure PDFDocumento12 páginasMetalizacao A Alto Vacuo Brochure PDFAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Ligações soldadasDocumento61 páginasLigações soldadasFilipe BastosAinda não há avaliações

- Email repetido terra.com.brDocumento53 páginasEmail repetido terra.com.brAnildo Eldivar De Oliveira Sarmento100% (2)

- Manual CHT ECDocumento83 páginasManual CHT ECWood_Araruama96% (25)

- Semp Toshiba LEM5Documento16 páginasSemp Toshiba LEM5Anildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Catálogo Carburadores Brosol Todos Os CarrosDocumento22 páginasCatálogo Carburadores Brosol Todos Os CarrosMário Andrade100% (1)

- RP 54na48pDocumento51 páginasRP 54na48pAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Monografia DefinitivaDocumento53 páginasMonografia DefinitivaAnildo Eldivar De Oliveira SarmentoAinda não há avaliações

- Manual da Central de Alarmes Safira L-XXXADocumento61 páginasManual da Central de Alarmes Safira L-XXXAReinaldo Souza0% (1)

- Transformador TrifásicoDocumento36 páginasTransformador TrifásicoNuno Lopes100% (2)

- INNOVCABLE CABO RV K PIVOT - IRRIGAÇÃO 06 - 1kV XLPE - PVC 90°C 1Documento5 páginasINNOVCABLE CABO RV K PIVOT - IRRIGAÇÃO 06 - 1kV XLPE - PVC 90°C 1Glauco AmancioAinda não há avaliações

- Catalogo de Nobreak SMS Station IIDocumento2 páginasCatalogo de Nobreak SMS Station IIHarley SantosAinda não há avaliações

- Curso Lumine - Procedimento para utilização do softwareDocumento34 páginasCurso Lumine - Procedimento para utilização do softwareIngridy Patrícia Carvalho SantanaAinda não há avaliações

- Audio Amps m3 A6 ProjectDocumento19 páginasAudio Amps m3 A6 ProjectJoão Pedro de Sá FlorentinoAinda não há avaliações

- Manual Posicionador SMARDocumento74 páginasManual Posicionador SMARJunior Ventura100% (1)

- Índice de partes para elevadores e escadasDocumento270 páginasÍndice de partes para elevadores e escadasWander Gomes67% (6)

- Check List nr12Documento3 páginasCheck List nr12jvborgptcAinda não há avaliações

- Tutorial Comunicação CLP s7 Com Nexto Altus Via ModbusDocumento11 páginasTutorial Comunicação CLP s7 Com Nexto Altus Via ModbusLucas BragaAinda não há avaliações

- Configuração de LEDs, teclado e displays no PIC16F877ADocumento4 páginasConfiguração de LEDs, teclado e displays no PIC16F877AEvandro Fernandes LedemaAinda não há avaliações

- Cubículos MT SF6 Catálogo TécnicoDocumento12 páginasCubículos MT SF6 Catálogo TécnicoFabianoAinda não há avaliações

- Diagrama Unifilar simplificadoDocumento27 páginasDiagrama Unifilar simplificadoLarissaAinda não há avaliações

- 2.2 Orientacoes Projeto SubestacaoDocumento5 páginas2.2 Orientacoes Projeto SubestacaoEL Projetos e Interiores Emanoel LucenaAinda não há avaliações

- Catálogo Peças Diversas - WertuoDocumento13 páginasCatálogo Peças Diversas - Wertuomarianilsasousamoreira458Ainda não há avaliações

- Manual Gerador BrancoDocumento21 páginasManual Gerador BrancoMauricio T. PinheiroAinda não há avaliações

- Hangar MmaDocumento35 páginasHangar MmaAlisson RamosAinda não há avaliações

- Relatório 2 - Correção Do Fator de PotênciaDocumento4 páginasRelatório 2 - Correção Do Fator de PotênciaericlesmauricioAinda não há avaliações

- Visita técnica à subestação da Cermoful descreve sistemas de energia elétricaDocumento10 páginasVisita técnica à subestação da Cermoful descreve sistemas de energia elétricaJOÃO PAULOAinda não há avaliações

- Canticle 2Documento7 páginasCanticle 2Inok Pinto QUICAXIAMOAinda não há avaliações

- Folha de DadosDocumento2 páginasFolha de DadosMarcos CalegariAinda não há avaliações

- Sucatas de cabos e fios de alumínioDocumento47 páginasSucatas de cabos e fios de alumínioFelipe CarlosAinda não há avaliações

- Experimento 1 - Osciloscópio de Raios CatódicosDocumento6 páginasExperimento 1 - Osciloscópio de Raios CatódicosMurilo Aguiar SilvaAinda não há avaliações

- Circuitos em SérieDocumento5 páginasCircuitos em SérieLuiz Lemes Barbosa NetoAinda não há avaliações

- Funcionamento Forno MicroondasDocumento23 páginasFuncionamento Forno MicroondastecjadirAinda não há avaliações

- Manual operação GPSDocumento33 páginasManual operação GPSjorgeAinda não há avaliações

- Gs - OC16 SG 406Documento2 páginasGs - OC16 SG 406itamarpereiraAinda não há avaliações

- Apostila de Cabeamento Estruturado - AnhangueraDocumento39 páginasApostila de Cabeamento Estruturado - AnhangueraRafael SalvagniAinda não há avaliações

- Burkert CatalogoDocumento91 páginasBurkert CatalogoMarcio Zanetti100% (1)

- Andre Silva Projeto MestradoDocumento146 páginasAndre Silva Projeto MestradorjiiAinda não há avaliações