Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista de Exerccios 2 - Memorias Barramentos E-S e Logica Digital

Enviado por

LucasTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lista de Exerccios 2 - Memorias Barramentos E-S e Logica Digital

Enviado por

LucasDireitos autorais:

Formatos disponíveis

UNIVERSIDADE FEDERAL DA PARAÍBA

CENTRO DE INFORMÁTICA

DISCIPLINA: Arquitetura de Computadores I

PROFESSOR: Ewerton Salvador

LISTA DE EXERCÍCIOS II

“Memória, Barramentos, Dispositivos de Entrada/Saída e Lógica Digital”

1. Quais das organizações de memória relacionadas a seguir são possíveis? Quais são razoáveis?

Justifique sua resposta.

a. 10 bits no campo de endereço, 1024 células, células de 8 bits

b. 10 bits no campo de endereço, 1024 células, células de 12 bits

c. 9 bits no campo de endereço, 1024 células, células de 10 bits

d. 11 bits no campo de endereço, 1024 células, células de 10 bits

e. 10 bits no campo de endereço, 10 células, células de 1024 bits

f. 1024 bits no campo de endereço, 10 células, células de 10 bits

2. Encontre a codificação de Hamming com paridade par para os dígitos decimais de 0 a 9.

3. A velocidade de transferência de dados entre o processador e a memória ligada a ele é ordens de

magnitude maior que a velocidade de transferência entre o processador e os dispositivos de E/S.

Explique como essa diferença de velocidade pode causar ineficiência. Como a ineficiência pode ser

evitada?

4. Um fabricante de terminais anuncia que seu terminal colorido mapeado a bit pode exibir 224 cores

diferentes. Acontece que ele também anuncia que o hardware usa somente um byte para cada pixel.

Como isso é possível?

5. Considere um texto ASCII com paridade par sendo transmitido assincronamente à velocidade de

2880 caracteres por segundo, usando um modem de 28.800 bps. Nessa situação, pergunta-se: qual a

porcentagem dos bits recebidos que efetivamente carregam informação?

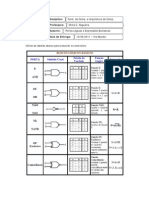

6. Considere a tabela-verdade abaixo para a função F de 3 variáveis:

A B C F

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 1

a) Represente a função F acima na notação de equação booleana

b)Desenhe o diagrama lógico da função F

7. Desenhe o diagrama lógico para um demultiplexador de 2 bits, um circuito cuja única linha de

entrada é diretamente relacionada para uma das quatro linhas de saúda dependendo do estado das duas

linhas de controle.

8. Um chip MSI comum é um somador de 4 bits. Um exemplo de uso desse tipo de chip é a conexão

de quatro desses chips para formar um somador de 16 bits. Quantos pinos você espera que tenha o chip

do somador de 4 bits? Por quê?

9. Uma ULA de 16 bits é composta de 16 ULAs de 1 bit, cada uma com um tempo de adição de 10

nanossegundos. Se houver 1 nanossegundo adicional de atraso de propagação de uma ULA para a

seguinte, quanto tempo leva para aparecer o resultado de uma soma de 16 bits

10. Qual a diferença entre um latch e um flip-flop?

Você também pode gostar

- Lista de Exercicios de Circuitos LógicosDocumento6 páginasLista de Exercicios de Circuitos LógicoswighouAinda não há avaliações

- Exercícios 1Documento7 páginasExercícios 1Thiana Tiller Reliquias GomesAinda não há avaliações

- Lista de Exercicios - Mux e DemuxDocumento3 páginasLista de Exercicios - Mux e DemuxLuìs100% (1)

- Livro Texto - Unidade IIIDocumento48 páginasLivro Texto - Unidade IIIGeovana DaniellaAinda não há avaliações

- Lista de Exercícios MatrizesDocumento2 páginasLista de Exercícios MatrizesViniciusAinda não há avaliações

- 04 ProcessadorDocumento122 páginas04 ProcessadorRamon NepomucenoAinda não há avaliações

- Lab-03 Guia para Prelab-03Documento8 páginasLab-03 Guia para Prelab-03Evandro Fernandes LedemaAinda não há avaliações

- Atividade de Pesquisa 01Documento6 páginasAtividade de Pesquisa 01Juliano MartinsAinda não há avaliações

- Circuitos CombinatóriosDocumento16 páginasCircuitos CombinatóriosPaulo RodriguesAinda não há avaliações

- Trabalho Gustavo InformaticaDocumento6 páginasTrabalho Gustavo InformaticaDani MeloAinda não há avaliações

- Atividade de Pesquisa 01Documento7 páginasAtividade de Pesquisa 01celsotkAinda não há avaliações

- Exercicio 20200610 GabDocumento6 páginasExercicio 20200610 Gabdont4getAinda não há avaliações

- Lab 2 # 1 Parte (1) Eletrônica DigitalDocumento8 páginasLab 2 # 1 Parte (1) Eletrônica DigitalgabrielgomesgblAinda não há avaliações

- LCL Relatorio 1Documento6 páginasLCL Relatorio 1luca50% (2)

- AP2-ED-Introdução A Algebra de BooleDocumento3 páginasAP2-ED-Introdução A Algebra de BooleFrancisco Gabriel VembaneAinda não há avaliações

- Exp 05 - LCLDocumento4 páginasExp 05 - LCLAna Luiza CamposAinda não há avaliações

- Codificador DecodDocumento22 páginasCodificador DecodCesar LoureiroAinda não há avaliações

- Xor XnorDocumento6 páginasXor XnorLucas Pedro ManuelAinda não há avaliações

- Portas Lógicas BásicasDocumento13 páginasPortas Lógicas BásicasguidoAinda não há avaliações

- LCL Exp 3Documento9 páginasLCL Exp 3Lucas BelloAinda não há avaliações

- Exp3 LCLDocumento6 páginasExp3 LCLAna Luiza CamposAinda não há avaliações

- EELi03 - Experimento 02 - Júlio César Ribeiro SilvaDocumento10 páginasEELi03 - Experimento 02 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- Exp 2 - VerilogDocumento5 páginasExp 2 - VerilogGabriel NazarioAinda não há avaliações

- Prática.1 Eletronica DigitalDocumento5 páginasPrática.1 Eletronica DigitalRoberto OliveiraAinda não há avaliações

- Atividade 08.1 Obrigatória 02Documento3 páginasAtividade 08.1 Obrigatória 02felipe.matAinda não há avaliações

- Codigos BinariosDocumento12 páginasCodigos BinariosWanderson BrumAinda não há avaliações

- Experimento 01Documento8 páginasExperimento 01Pedro HAinda não há avaliações

- Relatório Eletrônica DigitalDocumento8 páginasRelatório Eletrônica DigitalFlavia Rodrigues GabrielAinda não há avaliações

- Avaliação Final DigitalDocumento5 páginasAvaliação Final DigitalGeorge MaxwellAinda não há avaliações

- Ep01 2021Documento1 páginaEp01 2021no name100% (1)

- (1.0) KIT 2 - Decodificador - e - DisplayDocumento1 página(1.0) KIT 2 - Decodificador - e - DisplayBRENNAND DE AZEVEDO VENCESLAUAinda não há avaliações

- Atividade 3Documento3 páginasAtividade 3Um nome InteligenteAinda não há avaliações

- Atividade de Pesquisa 01 Eletronica DigitalDocumento5 páginasAtividade de Pesquisa 01 Eletronica DigitalHenrique MarquesAinda não há avaliações

- Atividade de Pesquisa 01 - Passei DiretoDocumento6 páginasAtividade de Pesquisa 01 - Passei DiretoJuliano MartinsAinda não há avaliações

- Lista de Exercícios LPAPDocumento1 páginaLista de Exercícios LPAPalberto maisAinda não há avaliações

- SEL0414 Lista4Documento1 páginaSEL0414 Lista4ban neleAinda não há avaliações

- Projeto FinalDocumento16 páginasProjeto FinalRob ColaresAinda não há avaliações

- Avaliação Final Digital (1) - CopiarDocumento5 páginasAvaliação Final Digital (1) - CopiarleandrodasilveiraoliveiraAinda não há avaliações

- Atividade 02 - Digital (2) - CopiarDocumento5 páginasAtividade 02 - Digital (2) - CopiarleandrodasilveiraoliveiraAinda não há avaliações

- Lab 2 # 2 Parte (1) - Eletrônica DigitalDocumento6 páginasLab 2 # 2 Parte (1) - Eletrônica DigitalgabrielgomesgblAinda não há avaliações

- LCL Codificador, DecodificadorDocumento7 páginasLCL Codificador, DecodificadoriorrannaAinda não há avaliações

- Laboratório CLD RevisadoDocumento61 páginasLaboratório CLD RevisadoGiovanneSiqueiraAinda não há avaliações

- Relatório 7 SegmentosDocumento9 páginasRelatório 7 SegmentosStefano ViégasAinda não há avaliações

- Relatório - P3Documento4 páginasRelatório - P3Luciano VarandaAinda não há avaliações

- Relatorios 3Documento7 páginasRelatorios 3Tong ZhouAinda não há avaliações

- Relatório DisplayDocumento10 páginasRelatório DisplayrzagottaniAinda não há avaliações

- FlipFlop Tipo RS SíncronoDocumento2 páginasFlipFlop Tipo RS SíncronoarturvilaresAinda não há avaliações

- Aula 05 - Prova de Desempenho Didático - UNIFESSPADocumento27 páginasAula 05 - Prova de Desempenho Didático - UNIFESSPAKamello AssisAinda não há avaliações

- Teste 1 - Electronica DigitalDocumento2 páginasTeste 1 - Electronica DigitalDosmito Joao DesmaAinda não há avaliações

- Relatório 1 Laboratório de Circuitos LógicosDocumento5 páginasRelatório 1 Laboratório de Circuitos LógicosiorrannaAinda não há avaliações

- Atividade 02 - Digital (Patrik Anderson Lourenço de Paula)Documento5 páginasAtividade 02 - Digital (Patrik Anderson Lourenço de Paula)Patrik100% (2)

- Xor XnorDocumento6 páginasXor XnorAntónio GomesAinda não há avaliações

- Atividade Portas LogicasDocumento5 páginasAtividade Portas LogicasNeto Pops100% (1)

- Avaliação de Pesquisa 01 - Eletrônica DigitalDocumento10 páginasAvaliação de Pesquisa 01 - Eletrônica DigitalLucelio PachecoAinda não há avaliações

- Avaliação Final Eletrônica DigitalDocumento4 páginasAvaliação Final Eletrônica DigitalLipe Souza cfssAinda não há avaliações

- Atividade de Pesquisa 02 - Eletrônica DigitalDocumento9 páginasAtividade de Pesquisa 02 - Eletrônica DigitalJuliano Martins100% (5)

- Prova 1Documento21 páginasProva 1ENERGOSAinda não há avaliações

- Lista2 - Expressões de LógicasDocumento2 páginasLista2 - Expressões de LógicasCanal Dos BusólogosAinda não há avaliações

- Lista de Exerccios 1 - Linguagens e Processador - 2023-2Documento1 páginaLista de Exerccios 1 - Linguagens e Processador - 2023-2LucasAinda não há avaliações

- Atividades de Química - 2 Ano - 13 SemanaDocumento1 páginaAtividades de Química - 2 Ano - 13 SemanaLucasAinda não há avaliações

- Lista de Exercicios - AssemblyDocumento1 páginaLista de Exercicios - AssemblyLucasAinda não há avaliações

- Arte BarrocaDocumento19 páginasArte BarrocaLucasAinda não há avaliações

- Direitos Civis, Politicos e SociaisDocumento27 páginasDireitos Civis, Politicos e SociaisLucasAinda não há avaliações

- Filosofia 1ºano 3º BimestreDocumento17 páginasFilosofia 1ºano 3º BimestreLucasAinda não há avaliações

- Lista 2 - FísicaDocumento3 páginasLista 2 - FísicaLucasAinda não há avaliações

- O Homem Como Um Ser PolíticoDocumento27 páginasO Homem Como Um Ser PolíticoLucasAinda não há avaliações

- Atividade Leis de Newton - 1 SérieDocumento3 páginasAtividade Leis de Newton - 1 SérieLucasAinda não há avaliações

- Atividade 03Documento1 páginaAtividade 03LucasAinda não há avaliações

- Arquivo de QuestõesDocumento1 páginaArquivo de QuestõesLucasAinda não há avaliações

- Prova 1 2021 1Documento2 páginasProva 1 2021 1LucasAinda não há avaliações

- Estrada de Catete, KM 19, Viana. Luanda - Angola: Quimicoil, LdaDocumento12 páginasEstrada de Catete, KM 19, Viana. Luanda - Angola: Quimicoil, LdaMárcio JorgeAinda não há avaliações

- Roda Da VidaDocumento7 páginasRoda Da VidaJana LagoeiroAinda não há avaliações

- O Que É ComununicaçãoDocumento6 páginasO Que É ComununicaçãoLiliane LuizaAinda não há avaliações

- Pedreiro REV0Documento2 páginasPedreiro REV0Alexandre MonteiroAinda não há avaliações

- Apresentação Artigo TCCDocumento13 páginasApresentação Artigo TCCAlexandre CastanheiraAinda não há avaliações

- ATIVIDADE DE REVISÃO 7º AnoDocumento3 páginasATIVIDADE DE REVISÃO 7º AnoSilvana Andrade FontesAinda não há avaliações

- Unidades de ConservacaoDocumento123 páginasUnidades de ConservacaoChristina FerreiraAinda não há avaliações

- (Estudo Dirigido) Leitura Do PoemaDocumento1 página(Estudo Dirigido) Leitura Do Poemaplatiny8Ainda não há avaliações

- EAD2020 BrCAST01 AnaCristinaGalesDocumento48 páginasEAD2020 BrCAST01 AnaCristinaGalesGabriel MaiaAinda não há avaliações

- Experimento Nº7Documento7 páginasExperimento Nº7Diane RégisAinda não há avaliações

- Plano de Aulas - Design de Padronagem DSG1151Documento3 páginasPlano de Aulas - Design de Padronagem DSG1151rickarturAinda não há avaliações

- A Lacuna Do Meio Excluido - Paul Hiebert PDFDocumento14 páginasA Lacuna Do Meio Excluido - Paul Hiebert PDFLeader GlobalAinda não há avaliações

- Teste de Preparação PSPO I™ - Modo Real - Mikhail LapshinDocumento22 páginasTeste de Preparação PSPO I™ - Modo Real - Mikhail LapshinRosana DiasAinda não há avaliações

- ABNT NBR 9575.2010 - Impermeabilização - Seleção e ProjetoDocumento14 páginasABNT NBR 9575.2010 - Impermeabilização - Seleção e ProjetoGUSTAVO LOBO FECCIAinda não há avaliações

- Exposto, Descoberto e Desclassificado Civilizações Perdidas eDocumento393 páginasExposto, Descoberto e Desclassificado Civilizações Perdidas eBernard CoutinhoAinda não há avaliações

- Relatório TermodinâmicaDocumento11 páginasRelatório TermodinâmicaMailson Arruda De AzevedoAinda não há avaliações

- O Papel Da Veracidade Divina No Sistema CartesianoDocumento1 páginaO Papel Da Veracidade Divina No Sistema CartesianoisabelmouradAinda não há avaliações

- Relatorio de Estagio Ilidio Artur Final RETDocumento37 páginasRelatorio de Estagio Ilidio Artur Final RETIlidio ArthurAinda não há avaliações

- Roteiro 2013 Leitura e Escrita PDFDocumento80 páginasRoteiro 2013 Leitura e Escrita PDFAnderson CPSAinda não há avaliações

- Destilação de Uma Mistura BináriaDocumento19 páginasDestilação de Uma Mistura BináriaIzabella BarbozaAinda não há avaliações

- d190f1e8b413eee57e51b0298e0e0a3eDocumento39 páginasd190f1e8b413eee57e51b0298e0e0a3ewilliamkleinpaul700Ainda não há avaliações

- AMS Visão Geral Dos Sistemas de DirecionamentoDocumento144 páginasAMS Visão Geral Dos Sistemas de DirecionamentoSUELENAinda não há avaliações

- Modelo - Rounds Clínicos - Unidade 2Documento7 páginasModelo - Rounds Clínicos - Unidade 2Karla BandeiraAinda não há avaliações

- Questionário Arte Na Pré História Unidade IIIDocumento13 páginasQuestionário Arte Na Pré História Unidade IIIBiblioteca PedrocarliAinda não há avaliações

- Objetivos Da Aula: Conceito de AnatomiaDocumento9 páginasObjetivos Da Aula: Conceito de AnatomiaSamara MoraesAinda não há avaliações

- Como Fazer Amigos e Influenciar Pessoas - As Técnicas de Dale CarnegieDocumento4 páginasComo Fazer Amigos e Influenciar Pessoas - As Técnicas de Dale CarnegieMauro Lúcio Martins100% (2)

- Revisão de FilosofiaDocumento4 páginasRevisão de FilosofiaAnaluzia DamiaoAinda não há avaliações

- Normas Da Língua PortuguesaDocumento19 páginasNormas Da Língua PortuguesaO Maggo Na vozAinda não há avaliações

- 1 3+-+exercícios PDFDocumento4 páginas1 3+-+exercícios PDFIgor Augusto100% (1)

- Registo de LaboratoriosDocumento149 páginasRegisto de LaboratoriosMadina MussagyAinda não há avaliações