Escolar Documentos

Profissional Documentos

Cultura Documentos

Série Prova P4 EAI 21 2019

Enviado por

t01g04Descrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Série Prova P4 EAI 21 2019

Enviado por

t01g04Direitos autorais:

Formatos disponíveis

EAI-21-2019: Série para a Prova P4

1Q: Usando funções MSI, FF’s e portas, projete uma fechadura digital ( ver figura 1 –

esquema) que se a sequência 50, 100 e 200 for feita à tranca se abre (saída Z3=1) caso

contrário à tranca não se abre (saída Z3=0). Duas saídas Z1 e Z2 mostram se a sequência

está correta. Quando Z1=1 e Z2=0 a sequência está errada; quando Z1=0 e Z2=1 a

sequência está correta; quando Z1=Z2=0 inicio da sequência deve ser introduzida;

quando Z1=Z2=1 é fim da sequência e está correta. A entrada X de 8 bits é usada para

gerar a sequência (entrada BCD). A variável inicio=0, a fechadura está trancada; para

inicio=1, começa a leitura do código (X). A variável inicio é síncrona.

Z1

X (8 bits)

M. S. S.

Fechadura Z2

Inicio digital

Z3

Clk

Figura 1 – Esquema da fechadura digital.

2Q: Usando somente um contador 74163, Mux’s e portas, projete um contador

binário de quatro bits com deslocamento bidirecional, onde a sua tabela de operações

está descrita na figura 2.

Es1 Es2

clk Dir Des Q1 Q2 Q3 Q4

P0 P1 P2 P3 0 x x Q1 Q2 Q3 Q4

load

clk

74163 1 x x Q1 Q2 Q3 Q4 Dir

Contador /

Q0 Q1 Q2 Q3 Des Deslocador

x 0 (Q1 Q2 Q3 Q4)N+1 clk

Q0 Q1 Q2 Q3

1 1 Es1 Q1 Q2 Q3

0 1 Q2 Q3 Q4 Es2

Figura 2 – Contador com deslocamento bidirecional

3Q: Usando FF’s de sua preferência e portas, projete um divisor de frequência

programável com ciclo de trabalho simétrico (50% alto e 50% baixo), descrito na figura

3.

X1 X2 Dividido por

X1 z 0 0 1

X2 0 1 2

Divisor

1Hz 1 0 3

1 1 4

Figura 3 – Tabela de operações do divisor programável

4Q: Usando funções MSI, Flip-Flops T e portas projetar um contador

síncrono de código de Gray de 4 bits de módulo variável com inicio zero.

Dados: converte binário para GrayG2=B2; G1=B2B1; G0=B1B0

O valor módulo está codificado em binário puro.

Obs: Ilustrando o módulo variável com inicio zero: Por exemplo, com módulo=5

(Binário (4) Gray (6)), então temos: 013260.......

5Q: Um estacionamento de um shopping tem duas entradas e duas saídas e comporta

100 automóveis. Defina as variáveis de entrada e saída do sistema digital síncrono e

projete este sistema para controlar o número de automóveis estacionados. O sistema

controla a entrada e saída dos automóveis e mostra o número de vagas existentes. Use

funções MSI, portas e Flip-Flops de sua preferência.

6Q: O esquema abaixo é um somador binário serial, sintetize a MEFS modelo Moore

minimizada usando portas e flip-flops JK.

Dados: QN+1=JQN’ + K’QN

A B

Somador

completo

Cout de 1 bit Cin

MEFS

Moore

Cout S CLK

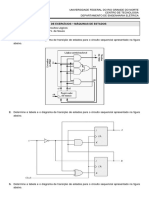

7Q: A figura 7 mostra o circuito lógico de uma MEFS modelo Moore e a

sua tabela de transição de estados, Pede-se a tabela de operações do flip-

flop Y da variável de estado Q3.

1

D1 Q1

Q1 A

B

Q1Q2Q3 00 01 11 10 Z

000 100 100 101 101 0

Z

D2 Q2 100 110 110 101 101 0

B

Q2 101 100 100 111 111 0

110 110 110 111 101 1

A Y3 Q3 111 100 110 111 111 1

Q3 (b)

CLK

(a)

Figura 7. MEFS modelo Moore: a) circuito lógico; b) tabela de transição de estados.

8Q: Faça o grafo de transição de estados de uma máquina de estado finito (MEF)

modelo Mealy que converte serialmente o código BCD no código Excesso-3. A MEF

tem uma entrada (x) e uma saída (y). Exemplos de conversão: 0000 0011; 1000

1011; 0101 1000.

MEF sincrona - Mealy

X Conversor serial Y

BCD Excesso-3

CLK

9Q: Usando a técnica de redes iterativa sequencial sintetize uma célula básica de um

contador síncrono binário crescente de N bits. Descreva o esquema células do

controlador de N bits

10Q: Seja uma macro-célula de um dispositivo programável composta de um FF JK e

lógica adicional (ver Figura 10). Através das entradas M e N esta macro-célula é

reconfigurável por programação. Projete esta macro-célula com o menor número de

portas NAND e Inversoras, onde ela realiza as seguintes operações: se M=N=0 a macro-

célula é um simples FF JK; se M=N=1 a macro-célula é um FF JK invertido, isto é à

saída da macro-célula é invertida; se M=0 e N=1, a macro-célula é um simples FF D; se

M=1 e N=0, a macro-célula é um simples FF T.

Obs: as equações características dos FFs são: QN+1=JQN´ + K´QN , QN+1=D e

QN+1=TQN.

Tabela de Reconfiguração

M N W Z Q Macro-célula

0 0 J K Q M N

W J Q

0 1 D --- Q Bloco

Lógico Flip-Flop

K

1 1 J K Q Z

Clk Q

1 0 T --- Q

Figura 10. Macro-célula de um dispositivo programável.

Você também pode gostar

- Ra115408 Ra109882 Ra107975Documento19 páginasRa115408 Ra109882 Ra107975Gabriel PavanAinda não há avaliações

- Sim 1Documento8 páginasSim 1Ana OchoaAinda não há avaliações

- Projetos Em Clp Ladder Baseado No Twidosuite Parte IvNo EverandProjetos Em Clp Ladder Baseado No Twidosuite Parte IvAinda não há avaliações

- Aula 3 Carboidratos em AlimentosDocumento60 páginasAula 3 Carboidratos em AlimentosGiliardy BrazAinda não há avaliações

- Como Vender Produtos Digitais Com o Google Drive e o PayPalDocumento11 páginasComo Vender Produtos Digitais Com o Google Drive e o PayPalMateus DuarteAinda não há avaliações

- Atividade - Teste Estilo de NegociaçãoDocumento3 páginasAtividade - Teste Estilo de NegociaçãoBazar Kawaii100% (1)

- Fototerapia 001Documento16 páginasFototerapia 001Jose MairenaAinda não há avaliações

- Lista 03 - Mecânica Dos FluidosDocumento2 páginasLista 03 - Mecânica Dos FluidosKatty BastosAinda não há avaliações

- Lista FinalDocumento9 páginasLista Final4paracompranoaliexpressAinda não há avaliações

- 007 ContadoresDocumento5 páginas007 ContadoresBruna FerreiraAinda não há avaliações

- Apostila de Eletrônica DigitalDocumento92 páginasApostila de Eletrônica DigitalValdo NunesAinda não há avaliações

- LE4: Circuitos Sequencias: Latches (Aula 5-1)Documento5 páginasLE4: Circuitos Sequencias: Latches (Aula 5-1)anyaAinda não há avaliações

- EEL5105 Lab4Documento22 páginasEEL5105 Lab4Gabriel BritoAinda não há avaliações

- Electronica Digital - D.timaneDocumento31 páginasElectronica Digital - D.timaneAnaciano SafoAinda não há avaliações

- Eletronica Digital CTE ParobeDocumento13 páginasEletronica Digital CTE ParobeFelipe FigueiróAinda não há avaliações

- Relatorio Projeto ContadorDocumento11 páginasRelatorio Projeto ContadorDiegoAinda não há avaliações

- Estudo de Caso de Processo de Manufatura Com S7300 Parte1Documento3 páginasEstudo de Caso de Processo de Manufatura Com S7300 Parte1kaduthewayAinda não há avaliações

- Aula 16Documento9 páginasAula 16Ïlïdïö GlxAinda não há avaliações

- Material de Contador SincronosDocumento30 páginasMaterial de Contador SincronosAldair LinoAinda não há avaliações

- Exp 3 - Gabriel Nazario GonçalvesDocumento5 páginasExp 3 - Gabriel Nazario GonçalvesGabriel NazarioAinda não há avaliações

- Preparação Do Laboratório 3Documento10 páginasPreparação Do Laboratório 3Max SousaAinda não há avaliações

- Manual 3 - Circuitos Sequenciais Assíncrono - ContadoresDocumento20 páginasManual 3 - Circuitos Sequenciais Assíncrono - ContadoresGabriel BeiresAinda não há avaliações

- Roteiro 9Documento11 páginasRoteiro 9José MatheusAinda não há avaliações

- Exercicios 2Documento20 páginasExercicios 2matheus mendonçaAinda não há avaliações

- Registradores e ContadoresDocumento34 páginasRegistradores e ContadoresWalterson SantosAinda não há avaliações

- Biblioteca 1828563Documento20 páginasBiblioteca 1828563Franz C SchreiberAinda não há avaliações

- Estudo de Caso de Processo de Manufatura Com S71200 Parte1Documento4 páginasEstudo de Caso de Processo de Manufatura Com S71200 Parte1Carlos SoaresAinda não há avaliações

- Gabarito Exercicio Classe P3 2022Documento7 páginasGabarito Exercicio Classe P3 2022Roger MeloAinda não há avaliações

- 4 Curso de Eletrônica Básica ParteDocumento22 páginas4 Curso de Eletrônica Básica PartePaulo Celestino de LimaAinda não há avaliações

- Modelo Pre RelatorioDocumento6 páginasModelo Pre RelatorioAlexson Sandro Vieira Cardoso JuniorAinda não há avaliações

- ContadoresDocumento21 páginasContadoressergioAinda não há avaliações

- Lista de Exercícios - Circuitos Digitais - ResoluçãoDocumento22 páginasLista de Exercícios - Circuitos Digitais - ResoluçãoElder SantosAinda não há avaliações

- Null 4Documento1 páginaNull 4Anivaldo SamboAinda não há avaliações

- LSD TesteModeloDocumento2 páginasLSD TesteModeloMargarida ToureiroAinda não há avaliações

- Lista de Exercícios - Máquinas de EstadoDocumento4 páginasLista de Exercícios - Máquinas de EstadoThiago AbrantesAinda não há avaliações

- Unidade Lógica e Aritmética (ULA) 8 BitsDocumento11 páginasUnidade Lógica e Aritmética (ULA) 8 BitsnataliaAinda não há avaliações

- Relatório 3Documento38 páginasRelatório 3Felix GabrielAinda não há avaliações

- Contadores Assíncronos e SíncronosDocumento10 páginasContadores Assíncronos e SíncronosVALERIA MARIA DE OLIVEIRA DA SILVAAinda não há avaliações

- Exame 1 Época - AC 21010 - 2017Documento5 páginasExame 1 Época - AC 21010 - 2017Ana FernandesAinda não há avaliações

- Prova 10 ED 1 Prova 2 EtapaDocumento3 páginasProva 10 ED 1 Prova 2 Etapahenrique silvaAinda não há avaliações

- Exemplo 1 Multiplicador BinarioDocumento12 páginasExemplo 1 Multiplicador BinariomoabrjAinda não há avaliações

- Relatório Exp DAC R-2RDocumento16 páginasRelatório Exp DAC R-2RMatheus ZimmerAinda não há avaliações

- GABARITO SIMULADO P2-SIST DIG (2s2022)Documento2 páginasGABARITO SIMULADO P2-SIST DIG (2s2022)iron hAinda não há avaliações

- Serie Problemas 2023Documento12 páginasSerie Problemas 2023Rafael MedeirosAinda não há avaliações

- Contadores Slides ÚteisDocumento16 páginasContadores Slides ÚteisCyro PereiraAinda não há avaliações

- Relé de Distância PDFDocumento12 páginasRelé de Distância PDFLeandro Mesquita CoelhoAinda não há avaliações

- Contadores DigitaisDocumento5 páginasContadores DigitaisRicardo AkermanAinda não há avaliações

- Relatório Projeto1 IncompletoDocumento6 páginasRelatório Projeto1 IncompletoMMO PlayEasyAinda não há avaliações

- Apostila Completa 2017 02Documento86 páginasApostila Completa 2017 02Lucas MunizAinda não há avaliações

- Cronometro DigitalDocumento5 páginasCronometro DigitalJosevaldo ArrudaAinda não há avaliações

- LEL - SD - Teste 1Documento3 páginasLEL - SD - Teste 1LeoAinda não há avaliações

- Lista de Exercícios 01 - Elétrica - 05 Abril 2023 - 1-1Documento7 páginasLista de Exercícios 01 - Elétrica - 05 Abril 2023 - 1-1Vinicius MatheusAinda não há avaliações

- Multiplexor e DemultiplexorDocumento17 páginasMultiplexor e DemultiplexorKelvin TanguneAinda não há avaliações

- Contadores AssincronosDocumento30 páginasContadores AssincronosGabriel ConjoAinda não há avaliações

- Controle Digital PDFDocumento23 páginasControle Digital PDFTiago Bauermann StaudtAinda não há avaliações

- 2 - ContadoresDocumento34 páginas2 - Contadoresfamilia unidaAinda não há avaliações

- Pratica ED - 3 - 2018Documento3 páginasPratica ED - 3 - 2018Samuel SilveiraAinda não há avaliações

- Exp04 BCD 7segmentosDocumento6 páginasExp04 BCD 7segmentosxdapocalypseAinda não há avaliações

- Aula 15 - Contadores Sincronos PDFDocumento40 páginasAula 15 - Contadores Sincronos PDFJoão VictorAinda não há avaliações

- Exercicios AOCO FEUPDocumento106 páginasExercicios AOCO FEUPRiverdale FanAinda não há avaliações

- Rel 2 - Eletronica DigitalDocumento13 páginasRel 2 - Eletronica Digitaltine.felipe1Ainda não há avaliações

- 07 Circuitos Sequenciais - ContadoresDocumento18 páginas07 Circuitos Sequenciais - ContadoresJefferson Eduardo LuizAinda não há avaliações

- Monitorando Através Do Visual C# O Barômetro Com O Stm32f103c8 Programado No ArduinoNo EverandMonitorando Através Do Visual C# O Barômetro Com O Stm32f103c8 Programado No ArduinoAinda não há avaliações

- Biomateriais Aplicados A ImplantodontiaDocumento10 páginasBiomateriais Aplicados A ImplantodontiaSergio S SouzaAinda não há avaliações

- Brayton 1Documento5 páginasBrayton 1Ismael TorresanAinda não há avaliações

- Relatório Força MagnéticaDocumento6 páginasRelatório Força MagnéticaVinícius HolandaAinda não há avaliações

- Peticao Inicial de Aposentadoria Por Idade RuralDocumento8 páginasPeticao Inicial de Aposentadoria Por Idade RuralDeyla CarvalhoAinda não há avaliações

- Teorias Sobre e AgressividadeDocumento6 páginasTeorias Sobre e Agressividadejoao100017Ainda não há avaliações

- Material de Apoio para Dep JA-AventureirosDocumento10 páginasMaterial de Apoio para Dep JA-AventureirosCleo Roger HeckAinda não há avaliações

- Sistema de Don't StarveDocumento4 páginasSistema de Don't StarveLeptos PiroseAinda não há avaliações

- A Globalização e o Estado Nacional - Bob JessopDocumento38 páginasA Globalização e o Estado Nacional - Bob JessopMelissa CmbhAinda não há avaliações

- MINIBESTDocumento3 páginasMINIBESTCarol BrisolaAinda não há avaliações

- Diariooficial 11 88 91 1Documento4 páginasDiariooficial 11 88 91 1Dom RodriguesAinda não há avaliações

- Antropologia Bíblica TRABALHODocumento5 páginasAntropologia Bíblica TRABALHORicardo KarenAinda não há avaliações

- Aula 4 - Michael Porter cp01Documento30 páginasAula 4 - Michael Porter cp01Angela GarciaAinda não há avaliações

- Cartilha para Fazer RÁDIO COMUNITÁRIA Com C MaiúsculoDocumento43 páginasCartilha para Fazer RÁDIO COMUNITÁRIA Com C MaiúsculorodrigojacobusAinda não há avaliações

- Apostila 02 - 8a FisicaDocumento4 páginasApostila 02 - 8a Fisicaedusf1000Ainda não há avaliações

- Dissertação Luisa Saad PDFDocumento147 páginasDissertação Luisa Saad PDFFernando CalegariAinda não há avaliações

- Conhecimentos Específicos - Administração Pública PDFDocumento88 páginasConhecimentos Específicos - Administração Pública PDFThiago AssisAinda não há avaliações

- MC9 EPI20140308 CAP150 DpiDocumento6 páginasMC9 EPI20140308 CAP150 Dpirita_mendes_10% (1)

- Programação Semanal AtualDocumento18 páginasProgramação Semanal AtualHaroldo Lage VieiraAinda não há avaliações

- Ensaio TorçãoDocumento24 páginasEnsaio TorçãoCícero DumAinda não há avaliações

- Plano de Ação Do Proemi Da Ee Vilmar Vieira Matos PDFDocumento9 páginasPlano de Ação Do Proemi Da Ee Vilmar Vieira Matos PDFclamenceAinda não há avaliações

- JF93-94G Service Manual - PortDocumento32 páginasJF93-94G Service Manual - PortMarcelo C. OliveiraAinda não há avaliações

- Vamos Testar Seu EntendimentoDocumento4 páginasVamos Testar Seu EntendimentoAlexandre MouraAinda não há avaliações

- Plano de Curso de LibrasDocumento3 páginasPlano de Curso de LibrasAlexandre VelosoAinda não há avaliações

- Estudo de Caso - ParmalatDocumento2 páginasEstudo de Caso - ParmalatEllen GonzagaAinda não há avaliações

- Praticas Aquaticas NatacaoDocumento72 páginasPraticas Aquaticas NatacaoVictor Seramucin100% (3)