Escolar Documentos

Profissional Documentos

Cultura Documentos

MM 12 LeticiaLeonel

Enviado por

Letícia Leonel0 notas0% acharam este documento útil (0 voto)

9 visualizações1 páginaTítulo original

MM_12_LeticiaLeonel

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

9 visualizações1 páginaMM 12 LeticiaLeonel

Enviado por

Letícia LeonelDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 1

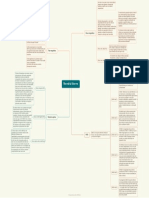

uscar instrução: o processador lê uma

B

instrução da memória (registrador, cache,

memória principal).

Interpretar a instrução: a instrução é

decodificada para determinar qual ação é

requerida.

m conjunto moderado de registradores

U

uniformes, mais do que são encontrados bter os dados: a execução de uma

o

em alguns sistemas CISC, porém menos do instrução pode requerer leitura de dados

que encontrados em muitos sistemas RISC. da memória ou um módulo de E/S.

Os requisitos que lhe são exigidos:

odelo carregar/armazenar (load/store) de

M rocessar os dados: a execução de uma

p

processamento de dados, no qual as instrução pode requerer efetuar alguma

operações executam apenas com os operação aritmética ou lógica com os

operandos nos registradores e não dados.

diretamente na memória. Todos os dados

precisam ser carregados em registradores ravar os dados: os resultados de uma

g

antes que uma operação possa ser execução podem requerer gravar dados

efetuada; o resultado então pode ser usado para memória ou um módulo E/S.

para o processamento posterior ou

armazenado em memória. ara fazer essas coisas, deve estar claro que

P

Organização do processador

o processador precisa armazenar alguns

ma instrução uniforme de tamanho fi xo

U dados temporariamente. Ele deve lembrar

de 32 bits para o conjunto padrão e 16 bits a posição da última instrução executante

para o conjunto de instruções Thumb. para que possa saber onde obter a

próxima instrução a ser executada. Ele

ara tornar cada instrução de

P precisa armazenar instruções e dados

processamento de dados mais fl exível, um temporariamente enquanto uma instrução

deslocamento ou uma rotação pode pré- está sendo executada. Em outras palavras,

processar um dos registradores de origem. o processador precisa de uma pequena

Para suportar esse recurso efi cientemente, memória interna.

a unidade aritmética lógica (ALU) e

Processador ARM

unidades de deslocamento são separadas.

m sistema de computador emprega uma

U

hierarquia de memória. Em níveis mais

m número pequeno de modos de

U altos da hierarquia, a memória é mais egistradores visíveis ao usuário:

R

endereçamento com todos os endereços rápida, menor e mais cara (por bit). Dentro possibilitam que o programador de

de carga/armazenamento sendo do processador, existe um conjunto de linguagem de máquina ou assembly

determinados a partir dos registradores e registradores que funcionam como um minimize as referências à memória, pela

campos da instrução. Endereçamento nível de memória acima da memória otimização do uso de registradores.

indireto ou indexado envolvendo valores principal e da cache dentro desta

na memória não é usado. hierarquia. Os registradores no egistradores de controle e estado: usados

R

processador desempenham dois papéis pela unidade de controle para controlar a

odos de endereçamento com

M operação do processador e por programas

autoincremento e autodecremento são privilegiados do Sistema Operacional para

usados para melhorar a operação controlar a execução de programas.

de laços de repetição dos programas.

ão há uma separação clara de

N

xecução condicional das instruções

E registradores nessas duas categorias. Por

minimiza a necessidade das instruções de exemplo, em algumas máquinas, o

desvios condicionais, melhorando assim a contador de programas é visível ao

efi ciência do pipeline, porque a limpeza usuário (por exemplo, o x86) mas, em

do pipeline é reduzida. muitos outros, não é. No entanto, para o

propósito da discussão que segue,

usaremos essas categorias.

organização dos registradores inclui os

A

seguintes tipos de registradores: propósito egistradores de propósito geral podem

R

geral, segmento, Flags, ponteiro da ser atribuídos para uma variedade de

funções pelo programador. Algumas vezes,

instrução, numérico, controle, estado,

palavra de marcação,

Estrutura e função seu uso dentro do conjunto de instruções é

ortogonal para a operação. Isto é, qualquer

mento de interrupção dentro de um

a

do processador registrador de uso geral pode conter um

operando para qualquer opcode. Isso

processador é uma facilidade oferecida permite o verdadeiro uso dos registradores

para suportar o sistema operacional. Isso de propósito geral.

permite que uma aplicação seja suspensa Família de processadores x86 Organização dos registradores

para que uma variedade de condições de

interrupção possa ser atendida e depois egistradores de dados podem ser usados

R

seja reiniciada. apenas para guardar dados

e não podem ser empregados para

calcular o endereço de um operando.

ste processo é também chamado de

E ma linha de montagem tira a vantagem

U egistradores de endereços podem

R

pipelining, porque assim como em uma do fato de que um produto passa por ser, de certa forma, de uso geral ou podem

tubulação, novas entradas são aceitas num vários estágios da produção. Ao implantar o ser dedicados para um modo de

lado antes que as entradas aceitas processo de produção em uma linha de ipeline de instrução é semelhante ao uso

P endereçamento em particular.

anteriormente apareçam como saídas do montagem, produtos em vários estágios de uma linha de montagem numa planta

outro lado. podem ser trabalhados simultaneamente. industrial.

xiste uma variedade de registradores do

E

processador que são empregados para

m hazard de pipeline ocorre quando o

U controlar a operação do processador.

pipeline, ou alguma parte dele, precisa Grande parte deles, na maioria das

parar porque as condições não permitem a máquinas, não é visível ao usuário. Alguns

execução contínua. Tal parada do pipeline podem ser visíveis às instruções da

é também conhecida como bolha de máquina executadas no modo de controle

pipeline. Existem três tipos de hazards: ou de sistema operacional.

recurso, dados e controle.

m dos principais problemas ao se

U

projetar um pipeline de instruções é uscar: lê a próxima instrução da memória

B

garantir um fluxo estável de instruções para dentro do processador

Pipeline de instruções

para os estágios iniciais do pipeline. O

primeiro impedimento, é a instrução xecutar: interpreta opcode e efetua a

e

condicional de desvio condicional. Até que m ciclo de instrução

U operação indicada.

a instrução seja executada de fato, é inclui os seguintes estágios:

impossível dizer se o desvio será tomado

Interromper: se as interrupções estão

ou não. habilitadas e uma interrupção ocorre, salva

o estado do processo atual a atende a

m exemplo instrutivo de um pipeline de

U interrupção.

instruções é o de Intel 80486. Ele

eitura, estágio de decodificação 1, estágio

L implementa um pipeline de cinco execução de uma instrução pode

A

de decodificação 2, execução e escrita. estágios: Ciclo da instrução envolver um ou mais operandos na

memória, onde cada um deles requer um

acesso à memória. Além disso, se o

endereçamento indireto é usado, então

acessos adicionais à memória são

necessários.

Você também pode gostar

- Guia Instalacao ANM 24 Net Portugues 02-20 SiteDocumento2 páginasGuia Instalacao ANM 24 Net Portugues 02-20 SiteMilton Pereira Dos SantosAinda não há avaliações

- Guia Instalacao ANM 24 Net Portugues 01-23 SiteDocumento2 páginasGuia Instalacao ANM 24 Net Portugues 01-23 SiteHumberto ClaudinoAinda não há avaliações

- Guia de Instalação - ANM 24 NET (ANM 24 NET)Documento2 páginasGuia de Instalação - ANM 24 NET (ANM 24 NET)rogeriop1986Ainda não há avaliações

- Fonte de AlimentacaoDocumento3 páginasFonte de AlimentacaobrenoAinda não há avaliações

- ADSS LAb 1Documento4 páginasADSS LAb 1Symon CovitchAinda não há avaliações

- Manual P6010 - P8010Documento2 páginasManual P6010 - P8010aless2056Ainda não há avaliações

- CIS Framework - Mapa MentalDocumento1 páginaCIS Framework - Mapa MentalDTS2 Ger Seg CibernéticaAinda não há avaliações

- PDE - Perfil de Desempenho Da Edificação - Residencial CozumelDocumento14 páginasPDE - Perfil de Desempenho Da Edificação - Residencial CozumelThalles Morais100% (4)

- Projeto ModelDocumento1 páginaProjeto Modelguilhermeferreira.empreendedorAinda não há avaliações

- React - Cheat SheetDocumento1 páginaReact - Cheat SheetLuiz Augusto Silva Dos SantosAinda não há avaliações

- 27 4N - Inc - Cbmerj - Irb - 11pav-Spda-SpdaDocumento1 página27 4N - Inc - Cbmerj - Irb - 11pav-Spda-SpdaPatrícia AraújoAinda não há avaliações

- 4 - Atividades de ControleDocumento1 página4 - Atividades de Controlekarloseduardo165Ainda não há avaliações

- Mapa MentalDocumento1 páginaMapa MentalLucas LopesAinda não há avaliações

- 2° Pavimento - Fiação - Elétrica-Model-3Documento1 página2° Pavimento - Fiação - Elétrica-Model-3Abidan GomesAinda não há avaliações

- Sentidos - FECHAMENTO TUTDocumento1 páginaSentidos - FECHAMENTO TUTLavínia SantanaAinda não há avaliações

- Prancha 01Documento1 páginaPrancha 01Carlos FelipeAinda não há avaliações

- Plano de Açao QualidadeDocumento1 páginaPlano de Açao QualidadeMIKAELLY MARQUES DA COSTAAinda não há avaliações

- 5 - Informação e ComunicaçãoDocumento1 página5 - Informação e Comunicaçãokarloseduardo165Ainda não há avaliações

- Lista Exercicios Fisica DDP Potencia Energia Eletrica Especifica FisicaDocumento6 páginasLista Exercicios Fisica DDP Potencia Energia Eletrica Especifica FisicamasterbsbAinda não há avaliações

- Efab BDocumento36 páginasEfab Bandi_lb945388% (8)

- 03 Execução - Mezanino e Área ExternaDocumento1 página03 Execução - Mezanino e Área ExternaEsdras souzaAinda não há avaliações

- Projeto FotovoltaicoDocumento1 páginaProjeto FotovoltaicoAdeylson Júnior Andrade Ramos50% (2)

- Diagrama Gca Servidor 450Documento1 páginaDiagrama Gca Servidor 450Silvanei AngeloAinda não há avaliações

- Guia Boas Praticas CT 500-01-17 SiteDocumento9 páginasGuia Boas Praticas CT 500-01-17 SiteJoão NicoliniAinda não há avaliações

- Projeto Elétrico CREAS-ModelDocumento1 páginaProjeto Elétrico CREAS-ModelDean DeanAinda não há avaliações

- Relatório InicialDocumento11 páginasRelatório InicialGuilherme BenevidesAinda não há avaliações

- Com Met PB 06 R00Documento1 páginaCom Met PB 06 R00delta duxAinda não há avaliações

- DESENHOSDocumento10 páginasDESENHOSJoão Henrique CarvalhoAinda não há avaliações

- Aterramento VMI PHILIPSDocumento3 páginasAterramento VMI PHILIPSRobson QuinagliaAinda não há avaliações

- Mpam-som&Vídeo-04-04-Planta de Locação e Fiação - Som - PisoDocumento1 páginaMpam-som&Vídeo-04-04-Planta de Locação e Fiação - Som - PisoHenrique Mendes da Rocha LopesAinda não há avaliações

- 5.encarte IFT Técnicas de Corte Direcional em EIRDocumento2 páginas5.encarte IFT Técnicas de Corte Direcional em EIRLeticia CarollyneAinda não há avaliações

- Vigas Fundação - Piscina-ModelDocumento1 páginaVigas Fundação - Piscina-ModelRicardo Alves (Rico)Ainda não há avaliações

- Projeto FotovoltaicoDocumento1 páginaProjeto Fotovoltaicokafiacalheiros50% (2)

- Esquema Da TV de Plasma LG 42PJ350Documento1 páginaEsquema Da TV de Plasma LG 42PJ350brayanethorAinda não há avaliações

- Roteiro Do Estuário Do TejoDocumento197 páginasRoteiro Do Estuário Do TejoPedro Antão100% (3)

- Projeto Executivo E E Luis Lopes de Carvalho - PDF RevisadoDocumento1 páginaProjeto Executivo E E Luis Lopes de Carvalho - PDF RevisadoaltengenhariaAinda não há avaliações

- Aferição de Nível de FluidoDocumento4 páginasAferição de Nível de FluidoEdmundo SouzaAinda não há avaliações

- Prontuário SN25099Documento229 páginasProntuário SN25099Victor DiasAinda não há avaliações

- Tudo Nosso 1Documento3 páginasTudo Nosso 1carllamaaraAinda não há avaliações

- Hardware IntroduçãoDocumento1 páginaHardware IntroduçãoMarcela Maraschin GrizottiAinda não há avaliações

- Eletrico 007 119 2023 R0Documento1 páginaEletrico 007 119 2023 R0Rafaela GomesAinda não há avaliações

- Tpf-34s31, Tpf32s55 e Tpw3280 Manual TécnicoDocumento62 páginasTpf-34s31, Tpf32s55 e Tpw3280 Manual Técnicoapi-3697672100% (1)

- Fonte Potencia Tsa210Documento1 páginaFonte Potencia Tsa210Antonio Fernandes de JesusAinda não há avaliações

- CoronéDocumento1 páginaCoronéFabio SouzaAinda não há avaliações

- Movimento CompostoDocumento6 páginasMovimento CompostoPedro NevesAinda não há avaliações

- Fonte Potencia Tsa420Documento1 páginaFonte Potencia Tsa420Antonio Fernandes de JesusAinda não há avaliações

- ATDF TEL LO 1104 PLA 3SS R01 Layout1Documento1 páginaATDF TEL LO 1104 PLA 3SS R01 Layout1David PinheiroAinda não há avaliações

- Tiny Epic Kingdoms - Livro de Regras Oficial Traduzido DiagramadoDocumento6 páginasTiny Epic Kingdoms - Livro de Regras Oficial Traduzido DiagramadoLufe MasAinda não há avaliações

- Detalhamento Dos Muros-ModelDocumento1 páginaDetalhamento Dos Muros-ModelRicardo Alves (Rico)Ainda não há avaliações

- Introdução À Engenharia de Software 1Documento31 páginasIntrodução À Engenharia de Software 1Josiane maraAinda não há avaliações

- Manual-de-Instrucoes-W09D - r0 ManualDocumento6 páginasManual-de-Instrucoes-W09D - r0 ManualElder GoncalvesAinda não há avaliações

- WEG Dispositivo Supervisor de Isolamento 10004636891 PTDocumento2 páginasWEG Dispositivo Supervisor de Isolamento 10004636891 PTBruno A.Ainda não há avaliações

- Nstalações Imbologia (NBR 5444) : Como IndicadoDocumento1 páginaNstalações Imbologia (NBR 5444) : Como IndicadoGuilherme SorianiAinda não há avaliações

- Guia - CIE 1125 - 1250 - 2500 - 02-23 - SiteDocumento2 páginasGuia - CIE 1125 - 1250 - 2500 - 02-23 - Siterafael.202411835Ainda não há avaliações

- Plataforma Esmeralda-2 2Documento1 páginaPlataforma Esmeralda-2 2Gustavo SousaAinda não há avaliações

- Esquema Elétrico - 2042 e 2842 PDFDocumento80 páginasEsquema Elétrico - 2042 e 2842 PDFjose breno vieira silva50% (4)

- MM 13 LeticiaLeonelDocumento1 páginaMM 13 LeticiaLeonelLetícia LeonelAinda não há avaliações

- Capitulo6 - Xmind - WorksDocumento1 páginaCapitulo6 - Xmind - WorksLetícia LeonelAinda não há avaliações

- MM 9 LeticiaLeonelDocumento1 páginaMM 9 LeticiaLeonelLetícia LeonelAinda não há avaliações

- Capitulo7 - Xmind - WorksDocumento1 páginaCapitulo7 - Xmind - WorksLetícia LeonelAinda não há avaliações

- A Arte de Escutar As CriançasDocumento63 páginasA Arte de Escutar As CriançasBarbara Raquel Prado Gimenez CorreaAinda não há avaliações

- Catálogo de Produtos - Ikeplast EmbalagensDocumento76 páginasCatálogo de Produtos - Ikeplast EmbalagensSuperfood CentroAinda não há avaliações

- Livoltek GT1-3K-S GT1-6K-D (Wi-Fi Incluso)Documento1 páginaLivoltek GT1-3K-S GT1-6K-D (Wi-Fi Incluso)Edson Feitosa LealAinda não há avaliações

- 04-Treinamento T Cnico TVC PHILCO TV14 TV 14E10Documento16 páginas04-Treinamento T Cnico TVC PHILCO TV14 TV 14E10Marco KersulAinda não há avaliações

- Gengibre Saúde InformaçõesDocumento14 páginasGengibre Saúde InformaçõesJuliana Esteves SantosAinda não há avaliações

- Avaliação Da Disciplina Ritmo e Dança - Professora MonalyseDocumento2 páginasAvaliação Da Disciplina Ritmo e Dança - Professora Monalysemonalyse carineAinda não há avaliações

- Tabela de Treino - LeandroTwin - RicardDocumento331 páginasTabela de Treino - LeandroTwin - RicardGabriel Andrade100% (9)

- Tratado Completo de Prestidigitação e Ilusionismo by J. PeixotoDocumento462 páginasTratado Completo de Prestidigitação e Ilusionismo by J. PeixotoRodrigo FontanelliAinda não há avaliações

- Catalogo Inox ParDocumento20 páginasCatalogo Inox ParMichel PereiraAinda não há avaliações

- Módulo 04Documento158 páginasMódulo 04MAILSON JANOCAAinda não há avaliações

- Atividades Complementares de PA e PGDocumento17 páginasAtividades Complementares de PA e PGReginaldo CoelhoAinda não há avaliações

- A Calibração Na ComunicaçãoDocumento2 páginasA Calibração Na Comunicaçãobeyou_acttodayAinda não há avaliações

- Classificacao Das Cadeias Organicas-1Documento2 páginasClassificacao Das Cadeias Organicas-1André CamargoAinda não há avaliações

- Guia de OndaDocumento70 páginasGuia de OndaEmília Targa Nunes GalvãoAinda não há avaliações

- Dissertacao ACGiannecchiniDocumento321 páginasDissertacao ACGiannecchiniRafa SouzaAinda não há avaliações

- Informações para Instalação Da OP30XDocumento2 páginasInformações para Instalação Da OP30XGabriel JanuárioAinda não há avaliações

- Uma Introdução Axiomática Dos Conjuntos - Antônio de Andrade e Silva PDFDocumento313 páginasUma Introdução Axiomática Dos Conjuntos - Antônio de Andrade e Silva PDFRichardVitaldaSilvaAinda não há avaliações

- Deus Quer Falar Contigo: Princípios para Uma Maior Intimidade Com DeusDocumento20 páginasDeus Quer Falar Contigo: Princípios para Uma Maior Intimidade Com DeusLoja Virtual Canção NovaAinda não há avaliações

- 4 - Apostila de Maquinas EletricasDocumento111 páginas4 - Apostila de Maquinas EletricasJediel Vagne da SilvaAinda não há avaliações

- Prova PB Ciencias 2ano Manha 2bim PDFDocumento4 páginasProva PB Ciencias 2ano Manha 2bim PDFDucarmo Flor100% (7)

- Franco - Coordenação Pedagógica - Uma Práxis em Busca de Sua IdentidadeDocumento15 páginasFranco - Coordenação Pedagógica - Uma Práxis em Busca de Sua IdentidadeBeatriz Gomes Nadal100% (1)

- 7 Razões para Participar Da Santa Ceia Do SenhorDocumento1 página7 Razões para Participar Da Santa Ceia Do SenhorRicardoAlexandrePereiraAinda não há avaliações

- Programa EQ741 PDFDocumento2 páginasPrograma EQ741 PDFewertonemmanuel2Ainda não há avaliações

- Lista 2 Mat CorrigidaDocumento7 páginasLista 2 Mat CorrigidaLeandroAinda não há avaliações

- PoligonosDocumento3 páginasPoligonosAndreia Lourenço100% (1)

- 165 Anos de O Livro Dos EspíritosDocumento19 páginas165 Anos de O Livro Dos EspíritosJovian FerreiraAinda não há avaliações

- Dicas Sped FiscalDocumento47 páginasDicas Sped FiscalPolkas PolkusAinda não há avaliações

- Lista de Material de ConsumoDocumento2 páginasLista de Material de ConsumoMarlon MichelAinda não há avaliações

- Rad SolosDocumento10 páginasRad SolosCarmen Regina CorreiaAinda não há avaliações

- ValorizaçãoDocumento16 páginasValorizaçãoDercioAinda não há avaliações

- Guia Definitivo Para Dominar o Bitcoin e as CriptomoedasNo EverandGuia Definitivo Para Dominar o Bitcoin e as CriptomoedasNota: 4 de 5 estrelas4/5 (5)

- Liberdade digital: O mais completo manual para empreender na internet e ter resultadosNo EverandLiberdade digital: O mais completo manual para empreender na internet e ter resultadosNota: 5 de 5 estrelas5/5 (10)

- Consultoria Especializada e Estratégias De Trade De ForexNo EverandConsultoria Especializada e Estratégias De Trade De ForexAinda não há avaliações

- Inteligência artificial: O guia completo para iniciantes sobre o futuro da IANo EverandInteligência artificial: O guia completo para iniciantes sobre o futuro da IANota: 5 de 5 estrelas5/5 (6)

- Lean Game Development: Desenvolvimento enxuto de jogosNo EverandLean Game Development: Desenvolvimento enxuto de jogosAinda não há avaliações

- Sua Primeira Startup: O Guia de Negócios Startup, da Ideia ao LançamentoNo EverandSua Primeira Startup: O Guia de Negócios Startup, da Ideia ao LançamentoAinda não há avaliações

- Quero ser empreendedor, e agora?: Guia prático para criar sua primeira startupNo EverandQuero ser empreendedor, e agora?: Guia prático para criar sua primeira startupNota: 5 de 5 estrelas5/5 (26)

- Gerenciamento da rotina do trabalho do dia-a-diaNo EverandGerenciamento da rotina do trabalho do dia-a-diaNota: 5 de 5 estrelas5/5 (2)

- Crie seu mercado no mundo digital: Aprenda a viver de e-commerce com a estratégia que levou inúmeros negócios on-line a sair do zero e ultrapassar os R$ 100 mil em vendas por mêsNo EverandCrie seu mercado no mundo digital: Aprenda a viver de e-commerce com a estratégia que levou inúmeros negócios on-line a sair do zero e ultrapassar os R$ 100 mil em vendas por mêsNota: 4.5 de 5 estrelas4.5/5 (6)

- Segurança Da Informação DescomplicadaNo EverandSegurança Da Informação DescomplicadaAinda não há avaliações

- Python e mercado financeiro: Programação para estudantes, investidores e analistasNo EverandPython e mercado financeiro: Programação para estudantes, investidores e analistasNota: 5 de 5 estrelas5/5 (3)

- Introdução Às Redes De Computadores: Modelos Osi E Tcp/ipNo EverandIntrodução Às Redes De Computadores: Modelos Osi E Tcp/ipAinda não há avaliações

- Análise técnica de uma forma simples: Como construir e interpretar gráficos de análise técnica para melhorar a sua actividade comercial onlineNo EverandAnálise técnica de uma forma simples: Como construir e interpretar gráficos de análise técnica para melhorar a sua actividade comercial onlineNota: 4 de 5 estrelas4/5 (4)

- Inteligência artificial: Como aprendizado de máquina, robótica e automação moldaram nossa sociedadeNo EverandInteligência artificial: Como aprendizado de máquina, robótica e automação moldaram nossa sociedadeNota: 5 de 5 estrelas5/5 (3)

- Arduino prático: 10 projetos para executar, aprender, modificar e dominar o mundoNo EverandArduino prático: 10 projetos para executar, aprender, modificar e dominar o mundoNota: 3.5 de 5 estrelas3.5/5 (4)

- Análise de Dados para Negócios: Torne-se um Mestre em Análise de DadosNo EverandAnálise de Dados para Negócios: Torne-se um Mestre em Análise de DadosAinda não há avaliações

- Legislação De Segurança Do Trabalho: Textos SelecionadosNo EverandLegislação De Segurança Do Trabalho: Textos SelecionadosAinda não há avaliações

- Fundamentos de Segurança da Informação: com base na ISO 27001 e na ISO 27002No EverandFundamentos de Segurança da Informação: com base na ISO 27001 e na ISO 27002Nota: 5 de 5 estrelas5/5 (8)