Escolar Documentos

Profissional Documentos

Cultura Documentos

Trabalho Relogio

Enviado por

Felipe Vieira0 notas0% acharam este documento útil (0 voto)

5 visualizações6 páginasrelogio eletronico

Título original

trabalho relogio

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentorelogio eletronico

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

5 visualizações6 páginasTrabalho Relogio

Enviado por

Felipe Vieirarelogio eletronico

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 6

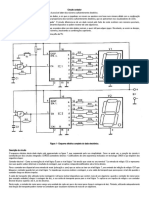

CIRCUITO DIVISOR DE FREQÊNCIA

Este circuito destina-se a receber o sinal de onda retangular de 60Hz e transformá-la em

um pulso por minuto.

Este pulso é obtido dividindo-se 60Hz (16.666666667ms) por 3600 obtendo

0,0166666666666667Hz.

Usando t=1/f teremos como resultado 59,99999999999988s (1 minuto).

Assim teremos 1 pulso a cada minuto para alimentar o circuito contador.

A divisão por 3600 vem através de uma lógica combinacional que leva em conta a

existência dos 12 FLIP-FLOPS no 4040. Usamos as portas de peso 16, 512, 1024, 2048

para obtermos assim os 3600.

Com 3 portas AND do CI4081 conseguimos efetuar essa lógica combinacional, e na

saída deles temos um pulso a cada 3600 pulsos da entrada.

Foi utilizado ainda as saídas Q6 e Q1, que dividem a frequência por 64 e 2

respectivamente, fazendo assim o ajuste lento e o ajuste rápido do relógio.

O pino 11 (reset) do CI 4081 é ligado à saída do circuito combinacional. Assim, a cada

pulso gerado por minuto ele recomeça a contagem do minuto.

Na saída de Q6 temos ainda um LED conectado, o que representaria os segundos dos

relógio, mas como a divisão não é exata (60/64 = 0,9375) ele pisca com um certo atraso

servindo assim somente para sabermos que o circuito esta em funcionamento.

CI4040

O CI 4040 é tecnicamente um chip contador de ripple binário de 12 estágios, em

palavras simples, um dispositivo que irá produzir uma saída de frequência atrasada

calculada em resposta a cada pulso aplicado em sua entrada de clock. Este atraso é

incrementado na taxa de 2 ^ (n) onde n é a ordem de pinagem na seqüência de suas

saídas.

Totalmente armazenadas 12 saídas que dividem os relógios de entrada na taxa 2 ^ (n)

onde n = a ordem de pinagem começando de Q1 até Q12.

O sequenciamento acima das saídas acontece em resposta a cada borda descendente do

clock aplicado em sua pinagem de entrada de clock CP. O CI responderá até mesmo a

um pulso de clock de queda relativamente lenta.

Uma única entrada de reset mestre assíncrono (MR) que redefine todas as saídas para

zero quando uma lógica alta é aplicada, enquanto uma lógica baixa constante permite

que o IC permaneça ativo.

O IC torna-se totalmente operacional com Vdd tão baixo quanto 3V e sustenta uma

característica operacional constante mesmo em voltagens em torno de 15V.

Pinouts Q1 a Q12 são as saídas do IC.

Vss é o pino de aterramento.

Vdd é o pino positivo.

MR é a pinagem de redefinição

CP é a entrada do relógio.

Saída Incremento Divisão

Q1 2^1 2

Q2 2^2 4

Q3 2^3 8

Q4 2^4 16

Q5 2^5 32

Q6 2^6 64

Q7 2^7 128

Q8 2^8 256

Q9 2^9 512

Q10 2^10 1024

Q11 2^11 2048

Q12 2^12 4096

As saídas assinaladas são as usadas no projeto do relógio.

CI 4081

O CI 4081 é constituído de 4 portas AND (E) com duas entradas em cada uma delas.

A alimentação é feita através do pino 14 e o aterramento no pino 7.

Este CI é usado para criar circuitos lógicos combinacionais.

No projeto do relógio foi utilizado 3 portas AND.

Você também pode gostar

- Contadores AssíncronosDocumento11 páginasContadores AssíncronosIvanir Ferreira da SilvaAinda não há avaliações

- Relogio Digital Cefet PBDocumento2 páginasRelogio Digital Cefet PBLuciene Ferreira Bezerrq FerreiraAinda não há avaliações

- Circuito Integrado CI - 4060Documento11 páginasCircuito Integrado CI - 4060luizempresa0% (1)

- Projeto e Implementação de Um Relógio Digital Utilizando PLDDocumento5 páginasProjeto e Implementação de Um Relógio Digital Utilizando PLDWeslley AlmeidaAinda não há avaliações

- Desenvolvendo Uma Lombada Eletrônica Para Apresentar A Velocidade Com ArduinoNo EverandDesenvolvendo Uma Lombada Eletrônica Para Apresentar A Velocidade Com ArduinoAinda não há avaliações

- RELATORIO Eletrônica Digital 5Documento14 páginasRELATORIO Eletrônica Digital 5Anna KroviskiAinda não há avaliações

- Projetos Com Esp8266 Programado Em Arduino - Parte XxvNo EverandProjetos Com Esp8266 Programado Em Arduino - Parte XxvAinda não há avaliações

- PCI 100A - Descrição de Funcionamento REV.BDocumento4 páginasPCI 100A - Descrição de Funcionamento REV.BDeivid MiquelinoAinda não há avaliações

- Relatório 3.12Documento18 páginasRelatório 3.12Felix GabrielAinda não há avaliações

- Rol DigDocumento8 páginasRol DigGomes MassinguilAinda não há avaliações

- Como Projetar Um Amplificador Classe AB - UFPEDocumento7 páginasComo Projetar Um Amplificador Classe AB - UFPEEdu Ardo100% (1)

- Relatório Contador Síncrono em AnelDocumento16 páginasRelatório Contador Síncrono em AnelFelix GabrielAinda não há avaliações

- Zero Cross Detector DesignDocumento11 páginasZero Cross Detector DesignRodrigoBernardoAinda não há avaliações

- Cópia de Circuito ContadorDocumento5 páginasCópia de Circuito ContadorRonaldo RochaAinda não há avaliações

- P3 Aplicações Do CI 555Documento7 páginasP3 Aplicações Do CI 555Aline MartinsAinda não há avaliações

- 4 Multímetro Como Detector de RelâmpagosDocumento3 páginas4 Multímetro Como Detector de RelâmpagosRobsonNunesDalColAinda não há avaliações

- Relatório 3.1Documento30 páginasRelatório 3.1Felix GabrielAinda não há avaliações

- Relatório PWMDocumento16 páginasRelatório PWMEduardo MorenoAinda não há avaliações

- Projetos Em Clp Ladder Baseado No Twidosuite Parte IvNo EverandProjetos Em Clp Ladder Baseado No Twidosuite Parte IvAinda não há avaliações

- CI 555 - Modo MonoestavelDocumento9 páginasCI 555 - Modo MonoestavelAlpha2designerAinda não há avaliações

- Projeto SemáforosDocumento7 páginasProjeto SemáforosAna Beatriz CunhaAinda não há avaliações

- Trabalho de Laboratório 3 Parte 2Documento1 páginaTrabalho de Laboratório 3 Parte 2AmíchelDeJesusSalomãoAinda não há avaliações

- Desenvolvendo Um Semáforo Com Temporização Controlada Por Sms Aplicado A Engenharia De Tráfego Com O ArduinoNo EverandDesenvolvendo Um Semáforo Com Temporização Controlada Por Sms Aplicado A Engenharia De Tráfego Com O ArduinoAinda não há avaliações

- Projetos Com Esp32 Programado Em Arduino - Parte XxvNo EverandProjetos Com Esp32 Programado Em Arduino - Parte XxvAinda não há avaliações

- Biblioteca 1828563Documento20 páginasBiblioteca 1828563Franz C SchreiberAinda não há avaliações

- Relogio Digital PDFDocumento2 páginasRelogio Digital PDFRogério Ferreira BritoAinda não há avaliações

- ExercÃ-cios ResExercÃ-cios ResolvidoolvidosDocumento77 páginasExercÃ-cios ResExercÃ-cios ResolvidoolvidosGian Do Atacado Silveira0% (1)

- O Circuito Integrado 555Documento7 páginasO Circuito Integrado 555Cutelaria ArtesanalAinda não há avaliações

- Projetos Com Esp8266 Programado Em Lua - Parte XxvNo EverandProjetos Com Esp8266 Programado Em Lua - Parte XxvAinda não há avaliações

- Relatório de Potência - Unidade IDocumento14 páginasRelatório de Potência - Unidade Ipão pão pãpAinda não há avaliações

- Banco de QuestõesDocumento20 páginasBanco de QuestõesdanielfortalAinda não há avaliações

- Circuitos-Logicos Aula 13-1Documento22 páginasCircuitos-Logicos Aula 13-1Maluuh MarquesAinda não há avaliações

- Relatório 03Documento13 páginasRelatório 03JVPRAinda não há avaliações

- Experiências Com O Módulo Pwm Programado No ArduinoNo EverandExperiências Com O Módulo Pwm Programado No ArduinoAinda não há avaliações

- ELETRONICA - Experimento - Guia 2 - 2010 - 1Documento8 páginasELETRONICA - Experimento - Guia 2 - 2010 - 1Filipe Rodrigues ViannaAinda não há avaliações

- Relatório Final TelecomunicaçõesDocumento20 páginasRelatório Final TelecomunicaçõesJonathan BehrensAinda não há avaliações

- CL Cap 7 2019 2Documento132 páginasCL Cap 7 2019 2Carllos LimmaAinda não há avaliações

- Atividade de Avaliação - STM32F4Documento2 páginasAtividade de Avaliação - STM32F4FlávioAinda não há avaliações

- Omeprazol2 222Documento6 páginasOmeprazol2 222Felipe VieiraAinda não há avaliações

- Recurso e DocumentosDocumento15 páginasRecurso e DocumentosFelipe VieiraAinda não há avaliações

- Apostila Delphi 7 em Formato Livreto para ImprimirDocumento38 páginasApostila Delphi 7 em Formato Livreto para ImprimirFelipe VieiraAinda não há avaliações

- Edital 40 2019 Transporte Escolar RetificadoDocumento47 páginasEdital 40 2019 Transporte Escolar RetificadoFelipe VieiraAinda não há avaliações

- Correpondências Comerciais - Português InstrumentalDocumento23 páginasCorrepondências Comerciais - Português InstrumentalFelipe VieiraAinda não há avaliações

- Correpondências Comerciais - Português Instrumental BookletDocumento12 páginasCorrepondências Comerciais - Português Instrumental BookletFelipe VieiraAinda não há avaliações

- Caderno Receitas 20190115Documento1 páginaCaderno Receitas 20190115Felipe VieiraAinda não há avaliações

- El65a - Circuitos DigitaisDocumento2 páginasEl65a - Circuitos DigitaisGabriel SchultzAinda não há avaliações

- Chip 8255 - PPIDocumento11 páginasChip 8255 - PPIPedro Henrique Rocha SousaAinda não há avaliações

- Aula 12 - RegistradoresDocumento19 páginasAula 12 - RegistradoresAndre SouzaAinda não há avaliações

- Atividade de Pesquisa 02 - Eletrônica DigitalDocumento9 páginasAtividade de Pesquisa 02 - Eletrônica DigitalJuliano Martins100% (5)

- Arquitetura de ComputadoresDocumento179 páginasArquitetura de Computadorestsf2012Ainda não há avaliações

- pcs3115 07 Sintese - MapaKarnaugh Vmarcos PDFDocumento32 páginaspcs3115 07 Sintese - MapaKarnaugh Vmarcos PDFJoão MiguelAinda não há avaliações

- Manual PC Analyzer 4 DigitosDocumento34 páginasManual PC Analyzer 4 Digitosvitorbxr100% (2)

- Relatório - Exp3 - Codificador Decodicador e Mux Demux - Eletrônica Digital - Quad4.2Documento6 páginasRelatório - Exp3 - Codificador Decodicador e Mux Demux - Eletrônica Digital - Quad4.2Fernando Henrique G. ZucatelliAinda não há avaliações

- Engenharia Eletrica Eletronica Perfil 4505Documento12 páginasEngenharia Eletrica Eletronica Perfil 4505Ramilton VasconcelosAinda não há avaliações

- Livro Digital 251 Sistemas Digitais Microprocessados Tema 3Documento11 páginasLivro Digital 251 Sistemas Digitais Microprocessados Tema 3Luiz HenriqueAinda não há avaliações

- Micro-Clp Clic WegDocumento53 páginasMicro-Clp Clic WegWillians Ribeiro MendesAinda não há avaliações

- Aula 3 - Placa Mãe e ProcessadoresDocumento18 páginasAula 3 - Placa Mãe e ProcessadoresInformaAinda não há avaliações

- Korg EM-1 SM PDFDocumento14 páginasKorg EM-1 SM PDFMarcelo JapaAinda não há avaliações

- Multiplexadores e Demultiplexadores (ART159)Documento9 páginasMultiplexadores e Demultiplexadores (ART159)Pascoal IlidioAinda não há avaliações

- PCS3225 2018S1 Planejamento Eng Eletrica v1Documento4 páginasPCS3225 2018S1 Planejamento Eng Eletrica v1Leonardo VergueiroAinda não há avaliações

- Exercícios - DecodificadoresDocumento1 páginaExercícios - Decodificadoresjhchaves1Ainda não há avaliações

- Mcs 51Documento135 páginasMcs 51Anonymous R0s4q9X8Ainda não há avaliações

- Atividade de Pesquisa 02 Eletrônica DigitalDocumento10 páginasAtividade de Pesquisa 02 Eletrônica DigitalHenrique MarquesAinda não há avaliações

- BookEletronicaDigital 00Documento22 páginasBookEletronicaDigital 00m23tt5Ainda não há avaliações

- Relatorio Eletronica DigitalDocumento11 páginasRelatorio Eletronica DigitalVinicius CostaAinda não há avaliações

- Multivibradores PDFDocumento26 páginasMultivibradores PDFMarco CapozzoliAinda não há avaliações

- Haida Lorencini 346656 0Documento25 páginasHaida Lorencini 346656 0haidaAinda não há avaliações

- Exercicios Portas LogicasDocumento1 páginaExercicios Portas LogicasEzekiel BulverAinda não há avaliações

- Computação Memoria e RegistradoresDocumento10 páginasComputação Memoria e RegistradoresFabrício SoaresAinda não há avaliações

- CRONOMETRODocumento12 páginasCRONOMETROLucas EmanuelAinda não há avaliações

- LCL Exp 8Documento7 páginasLCL Exp 8Lucas BelloAinda não há avaliações

- Evolução Dos ProcessadoresDocumento15 páginasEvolução Dos ProcessadoresEduardo RosalemAinda não há avaliações

- TRABALHO Portas LogicasDocumento7 páginasTRABALHO Portas LogicasAlex CleresAinda não há avaliações