Escolar Documentos

Profissional Documentos

Cultura Documentos

Slebf 20082009 Er

Enviado por

Helder Ramires0 notas0% acharam este documento útil (0 voto)

8 visualizações1 páginaTítulo original

slebf-20082009-er

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

8 visualizações1 páginaSlebf 20082009 Er

Enviado por

Helder RamiresDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 1

Departamento de Engenharia Electrotécnica

Sistemas Lógicos (MiEB+MiEF)

2008/2009

Mestrado integrado em Engenharia Biomédica

Mestrado integrado em Engenharia Física

Disciplina de Sistemas Lógicos - Exame Época Recurso – 21/7/2009 – 13h00mn

Duração: 2h00mn Tolerância: 15mn Sem consulta

Importante: numere as folhas que entregar (ex. 1 de 4) e identifique-se em todas elas

Responda em folhas separadas aos vários grupos de questões

Q1 ( 1 + 1 valores )

a) Prove recorrendo a tabela de verdade se a seguinte igualdade se verifica ou não

a.b + a .c + b.c = ab + a.c .

b) Considere a função f (a, b) = a b + a b . Proponha uma implementação da função utilizando sómente

portas NOR de duas entradas (apresente a expressão e o esquema lógico).

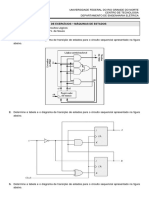

Q2 ( 3 + 1,5 + 1,5 valores )

a) Suponha que pretende fazer um sistema de detecção de erros na transmissão de um código 2-em-5. O

código 2-em-5 possui cinco bits, dois dos quais são ‘1’s e três são ‘0’s. Os bits recebidos são

designados por A, B, C, D e E. Pretende-se implementar a função f(A,B,C,D,E), de modo a determinar

se o código recebido é válido. Apresente a tabela de verdade para a função f(A,B,C,D,E).

b) Considere a função f ( A, B, C , D) = ∑ (0,1,2,3,9,10,11) . Implemente esta função utilizando somente

multiplexers com duas entradas de controlo e a lógica discreta que considere necessária. Utilize o

menor número de multiplexers na solução que apresentar.

c) Considere a função f ( A, B, C , D) = ∑ (0,1,2,3,9,10,11) . Implemente esta função utilizando somente

descodificadores com duas entradas de controlo e a lógica discreta que considere necessária. Utilize o

menor número de descodificadores na solução que apresentar.

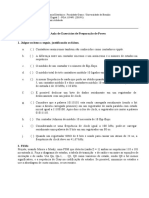

Q3 ( 2 + 3 + 2 valores )

Pretende-se projectar um contador síncrono, com 3 bits, que contará em módulo 5, utilizando os estados

de contagem 0, 1, 2, 3 e 4 (em decimal). As saídas coincidem com as variáveis de estado.

a) Apresente o diagrama de estados associado, a tabela de transição de estados e codificação de estados

proposta.

b) Utilizando um flip-flop tipo D para o bit mais significativo, um flip-flop tipo T para o bit seguinte e

um flip-flop tipo JK para o bit menos significativo, apresente as tabelas das entradas D2, T1, J0 e K0,

mapas de Karnaugh associados e expressões simplificadas (não é necessário apresentar o esquema

lógico).

c) Tendo em conta a resolução da alínea anterior, se o contador começar em 7 qual será a sequência do

contador até atingir um estado especificado (caso seja alcançado)?

Q4 ( 3 + 2 valores )

Pretende-se desenvolver um contador síncrono de 3 bits que permitirá contar o número de impulsos do

sinal de relógio, dispondo de duas entradas (X e Y) de controlo de modo

de funcionamento. Sempre que a entrada X esteja a ‘0’, então o estado de

contagem será congelado; caso contrário e caso a entrada Y esteja a ‘0’, o S0 S1

contador incrementa o seu estado (em módulo 8), caso contrário volta ao

estado inicial. x=1

a) Apresente um diagrama de estados para o contador descrito. S2 x=0

b) Para esta alínea, considere o diagrama de estados apresentado. x=0

Codifique os estados em código binário natural, i.e. S0=000, S1=001, ... e

x=1

apresente a tabela de transição de estados codificada resultante.

S3 S4

Você também pode gostar

- Slebf 20122013 1tDocumento1 páginaSlebf 20122013 1tHelder RamiresAinda não há avaliações

- Slebf 20092010 1tDocumento1 páginaSlebf 20092010 1tHelder RamiresAinda não há avaliações

- Bases de Numeração e AritméticaDocumento17 páginasBases de Numeração e AritméticaJuliano Oliveira DiasAinda não há avaliações

- SL1 Teste 206 RRDDocumento1 páginaSL1 Teste 206 RRDGonçalo GasparAinda não há avaliações

- Slei 20142015 1taDocumento1 páginaSlei 20142015 1taHelder RamiresAinda não há avaliações

- 1 Lista de Exercícios de Sistemas Digitais IDocumento8 páginas1 Lista de Exercícios de Sistemas Digitais IMarco Tulio SoaresAinda não há avaliações

- 01-Exercicios de Revisao Analise de AlgoritmosDocumento3 páginas01-Exercicios de Revisao Analise de AlgoritmosTássio Oliveira100% (1)

- Slebf 20082009 1tDocumento1 páginaSlebf 20082009 1tHelder RamiresAinda não há avaliações

- Serie Problemas 2023Documento12 páginasSerie Problemas 2023Rafael MedeirosAinda não há avaliações

- Sist Dig V21Documento57 páginasSist Dig V21Nuno CarvalhoAinda não há avaliações

- Slebf 20092010 ErDocumento1 páginaSlebf 20092010 ErHelder RamiresAinda não há avaliações

- Sistemas e Sinais - Exame Época EspecialDocumento1 páginaSistemas e Sinais - Exame Época EspecialPolo SemedoAinda não há avaliações

- Lista de Exercícios de Sistemas Digitais I - 1o Semestre de 2012Documento8 páginasLista de Exercícios de Sistemas Digitais I - 1o Semestre de 2012Wellington Júnio100% (1)

- 1 Lista de Exercícios AvaliativaDocumento5 páginas1 Lista de Exercícios AvaliativaWagner Dias CasagrandeAinda não há avaliações

- Sistemas LógicosDocumento2 páginasSistemas LógicosMaster DutyAinda não há avaliações

- Sistemas numéricos, códigos e eletrônica digitalDocumento9 páginasSistemas numéricos, códigos e eletrônica digitalErick Hermann FacundesAinda não há avaliações

- Lista 1Documento9 páginasLista 1Grazielle Tomaz NevesAinda não há avaliações

- Apostila de M01 Parte 1Documento81 páginasApostila de M01 Parte 1Anny GabrieleAinda não há avaliações

- Multiplexer e Circuitos CombinatóriosDocumento2 páginasMultiplexer e Circuitos CombinatóriosnelsonmdvAinda não há avaliações

- Null 4Documento1 páginaNull 4Anivaldo SamboAinda não há avaliações

- Prova - ServomecanismoDocumento7 páginasProva - ServomecanismoCamila Marques CoutoAinda não há avaliações

- Comparação de Magnitude - Algoritmo Lógica - A A A A A B B B B B - A Bsea B, A B, A B Ea B Testar Cada Bit: - Mais Complicado Testar Se A B E A BDocumento4 páginasComparação de Magnitude - Algoritmo Lógica - A A A A A B B B B B - A Bsea B, A B, A B Ea B Testar Cada Bit: - Mais Complicado Testar Se A B E A BInajá FerreiraAinda não há avaliações

- L1 PAC s112Documento18 páginasL1 PAC s112Alexis WalkerAinda não há avaliações

- 078 Engelet - 2002Documento27 páginas078 Engelet - 2002Sergio Henrique PaulaAinda não há avaliações

- Máquinas de Estados - Lista de ExercíciosDocumento4 páginasMáquinas de Estados - Lista de ExercíciosThiago AbrantesAinda não há avaliações

- Lista de Exercícios - Circuitos Digitais - Resolução - Frank VahidDocumento19 páginasLista de Exercícios - Circuitos Digitais - Resolução - Frank VahidElder SantosAinda não há avaliações

- 1 Lista de ExercíciosDocumento8 páginas1 Lista de ExercíciosThiago Abrantes0% (1)

- Prova I - Circuitos Digitais - 2022.1Documento4 páginasProva I - Circuitos Digitais - 2022.1Emmanuel --Ainda não há avaliações

- Sistemas numéricos e conversões em Eletrônica DigitalDocumento9 páginasSistemas numéricos e conversões em Eletrônica DigitaljamarosAinda não há avaliações

- Lista Exe Parte1 Digital EL52M PDFDocumento9 páginasLista Exe Parte1 Digital EL52M PDFRafaelVisettiSoaresAinda não há avaliações

- Lista de exercícios avaliativa de circuitos digitaisDocumento4 páginasLista de exercícios avaliativa de circuitos digitaisElder SantosAinda não há avaliações

- Lista 4 AslDocumento3 páginasLista 4 AslRobevaldo SantosAinda não há avaliações

- Guia Do Experimento 3 Módulo 2018.1Documento4 páginasGuia Do Experimento 3 Módulo 2018.1Felipe de SouzaAinda não há avaliações

- Processamento de Sinais IDocumento3 páginasProcessamento de Sinais Iamerico079Ainda não há avaliações

- Modelagem matemática de sistemas de controleDocumento28 páginasModelagem matemática de sistemas de controleHenrique LimaAinda não há avaliações

- Sistemas Digitais II Slides 1Documento52 páginasSistemas Digitais II Slides 1Benvindo XavierAinda não há avaliações

- Ajuste de curva e regressão numéricaDocumento18 páginasAjuste de curva e regressão numéricaIsabel JohannAinda não há avaliações

- Circuitos Digitais - ListaDocumento4 páginasCircuitos Digitais - ListaAndré Araújo de Souza SilvaAinda não há avaliações

- Circuito lógico para controle de silo de grãosDocumento3 páginasCircuito lógico para controle de silo de grãosadriano santos50% (2)

- Lista Exerc 02Documento3 páginasLista Exerc 02Philip ApsAinda não há avaliações

- Laboratório 1 - Análise e Controle de Sistemas MecânicosDocumento18 páginasLaboratório 1 - Análise e Controle de Sistemas Mecânicosjmaj jmajAinda não há avaliações

- Lista de Exercicios IDocumento5 páginasLista de Exercicios IWermersonAinda não há avaliações

- Lista de Exercícios Sobre Lógica CombinacionalDocumento7 páginasLista de Exercícios Sobre Lógica CombinacionalLorde-SanAinda não há avaliações

- Arquitetura de Computadores – Questionário 9Documento10 páginasArquitetura de Computadores – Questionário 9Marcus RamosAinda não há avaliações

- Lista 2023Documento3 páginasLista 2023Tárcio André dos Santos BarrosAinda não há avaliações

- Prova PhythonDocumento4 páginasProva PhythonAlexander CastroAinda não há avaliações

- Sistemas NumeraçãoDocumento17 páginasSistemas NumeraçãoNathaly LeiteAinda não há avaliações

- Lista de Sistemas de Controle IIDocumento9 páginasLista de Sistemas de Controle IIfelipesineiderAinda não há avaliações

- Exercicios Prova1 PDFDocumento3 páginasExercicios Prova1 PDFAline DiasAinda não há avaliações

- Simulado p2 - Sistemas DigitaisDocumento2 páginasSimulado p2 - Sistemas DigitaisBrendow AlmeidaAinda não há avaliações

- Provas Mestrado UFRNDocumento9 páginasProvas Mestrado UFRNDiego SouzaAinda não há avaliações

- Sistemas Digitais: Lista de Exercícios 1Documento4 páginasSistemas Digitais: Lista de Exercícios 1w ifAinda não há avaliações

- Tarefa 5 - Respostas de SistemasDocumento2 páginasTarefa 5 - Respostas de SistemasmariaeduardabatudAinda não há avaliações

- CNC CadernodeExercícioseRespostasDocumento107 páginasCNC CadernodeExercícioseRespostasdalibolzanAinda não há avaliações

- Exp 9 LGR 1Documento4 páginasExp 9 LGR 1Mk DuarteAinda não há avaliações

- Controle Vetorial, Máquina De Indução E Métodos NuméricosNo EverandControle Vetorial, Máquina De Indução E Métodos NuméricosAinda não há avaliações

- Projetos Com Esp8266 Programado Em Lua - Parte XxvNo EverandProjetos Com Esp8266 Programado Em Lua - Parte XxvAinda não há avaliações

- Catálogo de Treinamentos - V6 FLUIG PDFDocumento17 páginasCatálogo de Treinamentos - V6 FLUIG PDFErick LandaverdeAinda não há avaliações

- Manual Do Operador SS HY-TECH 11000 - 12000 - 13000 - 2005 - Rev 04Documento45 páginasManual Do Operador SS HY-TECH 11000 - 12000 - 13000 - 2005 - Rev 04Renan Carlos KraemerAinda não há avaliações

- PSI - Aula 06Documento47 páginasPSI - Aula 06alice ramalhoAinda não há avaliações

- Certificado Digital A1 Gerado no PCDocumento3 páginasCertificado Digital A1 Gerado no PCLais souzaAinda não há avaliações

- TED realizada com sucessoDocumento1 páginaTED realizada com sucessoVanderlei Gomes JuniorAinda não há avaliações

- Manual Marcação Exame Exin AnywhereDocumento16 páginasManual Marcação Exame Exin AnywhereThalita NayeliAinda não há avaliações

- Dse-7320 Po PDFDocumento3 páginasDse-7320 Po PDFUenis TavaresAinda não há avaliações

- Arquitetura ARMDocumento75 páginasArquitetura ARMFernando 44Ainda não há avaliações

- Tecnico de LaboratorioeletronicaDocumento9 páginasTecnico de LaboratorioeletronicaVanessa LopesAinda não há avaliações

- Comunicação institucional UFCDDocumento2 páginasComunicação institucional UFCDjoanapereirax100% (1)

- Manual de Utilização - SascarDocumento9 páginasManual de Utilização - SascarSalvatore DuarteAinda não há avaliações

- Controle AmbientalDocumento144 páginasControle AmbientalMarcelo PalharesAinda não há avaliações

- Vivo - Box ZTE MF253L Manual Do Usuário PDFDocumento13 páginasVivo - Box ZTE MF253L Manual Do Usuário PDFOlivan B. RibeiroAinda não há avaliações

- Encoder Incremental e Contagem RápidaDocumento19 páginasEncoder Incremental e Contagem RápidaRgerFbianAinda não há avaliações

- Pisos de aço em estruturas LSFDocumento29 páginasPisos de aço em estruturas LSFRafael ScalabrinAinda não há avaliações

- Cha Tecnica Messer Terrablade 4.0: Sobre 260.000.000 Resultados DataDocumento3 páginasCha Tecnica Messer Terrablade 4.0: Sobre 260.000.000 Resultados DataDiomar GonçalvesAinda não há avaliações

- Esquema Eletrico Gol Geração 4Documento7 páginasEsquema Eletrico Gol Geração 4LUCAS ALVESAinda não há avaliações

- Erros e soluções para máquinas de bordado TajimaDocumento1 páginaErros e soluções para máquinas de bordado Tajimamari dalmazAinda não há avaliações

- Questões de Internet (CESPE)Documento23 páginasQuestões de Internet (CESPE)jsd200100% (1)

- Teorias de Localização Alojamentos Geográfica.Documento141 páginasTeorias de Localização Alojamentos Geográfica.Naiss Almeida SantosAinda não há avaliações

- Caderno Pedagógico - Linguagens e Suas TecnologiasDocumento21 páginasCaderno Pedagógico - Linguagens e Suas TecnologiasJoão PaivaAinda não há avaliações

- Portfólio Individual Projeto de Extensão I - Engenharia Civil 2024 - Programa de Contexto À ComunidadeDocumento1 páginaPortfólio Individual Projeto de Extensão I - Engenharia Civil 2024 - Programa de Contexto À ComunidadeAlex NascimentoAinda não há avaliações

- Manual Datacom dm2500Documento81 páginasManual Datacom dm2500Rodrigo De Mattos60% (5)

- Trabalho IHMDocumento3 páginasTrabalho IHMElton FabrícioAinda não há avaliações

- Registro de não conformidadeDocumento2 páginasRegistro de não conformidadeVila Feliz100% (3)

- Propulsã - o Azipodâ® - Aversa - HermannDocumento62 páginasPropulsã - o Azipodâ® - Aversa - HermannGabriel100% (1)

- GULF FORMULA GVX 5W30 SNDocumento1 páginaGULF FORMULA GVX 5W30 SNMedero MederoAinda não há avaliações

- Guia de Implantação ARCServe UDPDocumento756 páginasGuia de Implantação ARCServe UDPchakal_brAinda não há avaliações

- Componentes Curriculares - ArtesDocumento20 páginasComponentes Curriculares - ArtesAndré Santos100% (1)

- IT-SMSQ-140 Formação de CIPA FaltaDocumento7 páginasIT-SMSQ-140 Formação de CIPA FaltaRômulloAinda não há avaliações