Escolar Documentos

Profissional Documentos

Cultura Documentos

Amplificador Operacional IFpe Ampl Oper

Enviado por

Dizu ZuleneDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Amplificador Operacional IFpe Ampl Oper

Enviado por

Dizu ZuleneDireitos autorais:

Formatos disponíveis

16/05/2011

AMPLIFICADOR OPERACIONAL

CAPITULO 2 AMPLIFICADOR OPERACIONAL

2.1.Introduo

O amplificador operacional (AO) um dispositivo em CI que tem grandes aplicaes em todas as

reas da eletrnica. Como o circuito interno muito complexo toda a analise a ser feita considerando o

modelo a ser visto a seguir na Fig 2.1, o qual adequado para a maioria das aplicaes. A Fig2.1a mostra o

smbolo do AO e a Fig2.1b o circuito equivalente simplificado.

(a)

(b)

Fig2.1: Amplificador operacional Smbolo e circuito equivalente

Na Fig2.1 v1 a tenso aplicada na entrada no inversora e v2 a tenso aplicada

na entrada inversora.

Vi = v1 v2 o sinal erro ou sinal diferena

Ri a resistncia de entrada

RO a resistncia de sada

Av o ganho de tenso em malha aberta (ganho sem realimentao)

Sem nenhuma carga ligada na sada, VS = AvVi = Av .(v1 v2 ), isto , o AO pode ser considerado basicamente

como um amplificador diferencial , pois a sada responde somente diferena entre as duas tenses de

entrada, se v1 = v2 VS =0.

Um AO idealmente deveria ter as seguintes caractersticas:

a) Resistncia de entrada infinita

b) Resistncia de sada nula

c) Ganho de tenso em malha aberta infinito

d) Largura de faixa infinito

e) Ausncia de offset na sada( Vs = 0 se v1 = v2 )

f) Slew rate infinito

2.2 Circuitos Bsicos

Os circuitos que sero vistos a seguir so considerados bsicos pois derivam a maioria dos circuitos que sero

vistos em seguida.

2.2.1. Amplificador Inversor

um circuito com realimentao negativa, obtida atravs da rede de resistores R2 e R1.

ifpe.edu.br/cefet/anterior//AOP.htm

1/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.2.: Amplificador inversor

Consideraes:

1. Vamos admitir que o ganho de malha aberta infinito, isto , AV = VS/Vi = infinito, logo Vi = Vs/AV = 0

isto , o ponto A tem o mesmo potencial do terra (dizemos que o ponto A um terra virtual).

2. Tambm consideraremos que Ri infinito e em conseqncia I1 = I2 (a corrente nas entradas do AO so

nulas).

Feitas as consideraes acima da Fig2.2 obtemos:

Ve = R1 .I1 e VS = - R2 .I2 portanto AVf = VS/Ve = - R2 .I2 /R1 .I1

e como I1 = I2 AVf = - R2 /R1

O sinal negativo indica defasagem de 180 entre Ve e VS do circuito A resistncia de entrada do circuito

dada por Rif = R1 ( a resistncia efetivamente vista pela fonte Ve.

A resistncia de sada que a carga RL enxerga quando olha para o AO dada por:

Exerccios Resolvidos

2.1. Calcule VS e a corrente de sada do AO (IAO ) no circuito.

Soluo:

Ve =1V AVf = - 4K7/1K = -4,7 logo Vs = AVf.Ve = -4,7.1V = - 4,7V

IL = -4,7V/10K = - 0,47mA( para cima) e IAO = I1 + I2 = 1mA + 0,47mA = 1,47mA

ifpe.edu.br/cefet/anterior//AOP.htm

2/53

16/05/2011

AMPLIFICADOR OPERACIONAL

( entrando no AO )

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_1.CIR

2.2. Desenhar os grficos de Vsxt e Vext para o circuito.

Ve = 0,2.senwt(V)

Soluo:

AVf = Vs/Ve = -10 logo Vs = -10.0,2.senwt = -2.senwt(V)

Formas de onda

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_2.CIR

2.2.2 Amplificador No Inversor

o circuito da Fig2.3, no qual podemos observar que a realimentao continua ser negativa, mas o sinal a ser

amplificado aplicado na entrada no inversora.

Fig2.3: Amplificador no inversor

As mesmas consideraes feitas para o amplificador inversora tambm sero feitas para a obteno do ganho

ifpe.edu.br/cefet/anterior//AOP.htm

3/53

16/05/2011

AMPLIFICADOR OPERACIONAL

com realimentao ( AVf = Vs/Ve ), logo podemos escrever :

Ve = R1 .I1 e VS = (R1 + R2 ).I1 o ganho com realimentao ser dado por :

AVf = VS/Ve = (R1 + R2).I1 /R1 .I1 = (R1 + R2 )/R1 ou AVf = 1 + R2 /R1

A resistncia de entrada com realimentao do circuito muito alta sendo dada por:

E a resistncia de sada muito baixa sendo dada por:

2.2.2.1 - Buffer

Um circuito derivado do amplificador no inversor o buffer ou seguidor de tenso o qual obtido a

partir da Fig2.3 fazendo-se R1 = infinito (circuito aberto) e R2 = 0 (curto circuito) resultando o circuito da

Fig2.4.

Fig2.4: Seguidor de tenso ( buffer)

Este circuito caracterizado por ter ganho de tenso igual a 1, altssima resistncia de entrada e baixssima

resistncia de sada, sendo calculadas respectivamente por :

Rif = Ri .AV e Rof = RO /AV

A principal aplicao de um circuito buffer isolar um circuito que tem alta resistncia de sada de uma carga

de baixo valor.

Exerccios Resolvidos

2.3. Determinar VS no circuito.

ifpe.edu.br/cefet/anterior//AOP.htm

4/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_3.CIR

Soluo:

A tenso de entrada do circuito

como o ganho igual a 2 (1+R2 /R1 ) a sada ser igual a:

VS = 2.2V = 4V

2.4. - Qual a mxima amplitude que pode ter a tenso de entrada Ve para que a sada

no sature distorcendo a senoide de sada ?

Vsat = 10V

Soluo:

A mxima amplitude de sada 10V, como o ganho AVf = 1 +10K/1K = 11 a mxima amplitude da entrada

ser :

Vemx = Vsmx/11 = 10V/11 = 0,91V

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_4.CIR

2.5. - Qual o valor de Ve que resulta numa sada (Vsaida) igual a 8V no circuito ?

ifpe.edu.br/cefet/anterior//AOP.htm

5/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Soluo:

O ganho do 2 estgio AVf2 = 4

logo a tenso de entrada do 2 estgio ser Vs1=VS/AVf2=8V/4=2V

O ganho do 1 estgio AVf1 = -2

logo a tenso de entrada do 1 estgio, que a tenso de entrada do

circuito ser Ve = VS1 = 2V/-2 = -1V.

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_5.CIR

2.6. - Qual o valor de R para que VS = 6V ?

Soluo:

A tenso no ponto A igual tenso no ponto B (a corrente atravs do 10K nula).

Como o ganho do segundo AO vale 2, com VS =6V a tenso na entrada (ponto B) ser

igual a:

VB = 6V/2 = 3V.

O 1 AO um buffer, a sua tenso de sada (VA ) igual tenso de

entrada (V+), portanto :

V+ =R.10V/(R + 10K) = 3V R = 943 Ohms

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_6.CIR

ifpe.edu.br/cefet/anterior//AOP.htm

6/53

16/05/2011

AMPLIFICADOR OPERACIONAL

2.2.3 Sada de Potncia

A mxima corrente de sada de um AO aproximadamente 20mA. Quando a carga solicitar uma corrente

maior, necessrio colocar entre a carga e o AO um reforador de corrente que em geral um transistor na

configurao coletor comum. A Fig2.5a um circuito no-inversor com sada de potncia, mas a corrente na

carga s circula num sentido. O circuito da Fig2.5b permite que a entrada seja alternada (no semiciclo positivo

conduz TR1 e no semiciclo negativo conduz TR2).

(a)

(b)

Fig2.5: Amplificador no-inversor com sada de potncia

Exerccios Resolvidos

2.7. No circuito pede-se calcular: a) Corrente na carga b) Corrente na sada do AO

c)Potncia dissipada na carga. Dado: =200

Soluo:

I1 = VR1 /R1 =5V/10K =0,5mA = I2 VR2 = 10K.0,5mA = 5V

como VL = VR1 + VR2 = 5 + 5 = 10V IL = 10V/100 = 0,1A = 100mA.

b) IE = I2 + IL = 0,5 + 100 = 100,5mA IC

IAO =IB = IC/ = 100,5mA/200 0,5mA

c) PDRL = VL.IL = 10V.0,1 A = 1W a potncia dissipada transistor calculada por

ifpe.edu.br/cefet/anterior//AOP.htm

7/53

16/05/2011

AMPLIFICADOR OPERACIONAL

PDTR = VCE .IC = 5V.0,1 A=0,5W.

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_7.CIR

2.8. Calcule a potncia dissipada na carga RL .

Ve = 1senwt(V)

Soluo:

No semiciclo positivo conduz TR2 e temos o circuito, e considerando o valor de pico da entrada (1V), a

corrente em 1K e em 10K ser I =1V/1K =1mA resultando uma tenso na carga de

Vs = AVf.Ve = (-10).1V = -10V de forma que a corrente na carga ser igual a IL =-10V/20 = -0,5 A (para

cima). No semiciclo negativo as correntes invertem de sentido e agora quem conduz TR1 , e TR2 corta.

Ve: Semiciclo positivo

Ve: Semiciclo negativo

ifpe.edu.br/cefet/anterior//AOP.htm

8/53

16/05/2011

AMPLIFICADOR OPERACIONAL

tenso de pico na carga VP =10V como uma tenso senoidal o seu valor eficaz

a potncia dissipada na carga ser

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_8.CIR

Exerccios Propostos

2.1. Calcular VS em cada caso.

1a.

1b

ifpe.edu.br/cefet/anterior//AOP.htm

9/53

16/05/2011

AMPLIFICADOR OPERACIONAL

2.2. Calcule a corrente na sada de cada AO no ex1

2. 3. O circuito a seguir funciona como uma fonte de corrente constante (mesmo que a

carga mude de valor , o valor da corrente no muda 0. Pede-se:

a) Valor da corrente na carga (IL )

b) Quais os limites que pode Ter RL , na prtica, para que o circuito possa funcionar

como fonte de corrente?

2.4. O circuito um voltmetro de preciso.Qual o fim de escala para cada posio

da chave?

ifpe.edu.br/cefet/anterior//AOP.htm

10/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Obs: Os resistores so de preciso.

2.5. O circuito um ohmmetro de preciso e linear. Quais os limites de resistncia que

podem ser medidos (fim de escala) em cada posio da chave?

Obs: Os resistores (100 ,1K,10K) so de preciso e o voltmetro na sada tem 10V de

fim de escala.

2.2.4 CARACTERISTICAS DE UM AMPLIFICADOR OPERACIONAL REAL

2.2.4.1 GANHO DE TENSO E LARGURA DE FAIXA

Na prtica o ganho de tenso e a largura de faixa no so infinitos. O ganho de tenso diminui com o aumento

da freqncia. A Fig1.12 mostra a curva de resposta em freqncia em malha aberta de um AO tpico.

ifpe.edu.br/cefet/anterior//AOP.htm

11/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.6: Curva de resposta em freqncia

A escala do ganho na Fig2.6 pode ser especificada em dB ou simplesmente ser igual relao entre a sada e

a entrada (Vs/Ve), sendo que o ganho em dB calculado por :

Ganho(dB) = 20.logVs/V

A escala em dB linear. Do grfico da Fig2.6 podemos ver que o ganho em malha aberta vale 100.000

(100dB), ficando constante at 10Hz. Acima de 10Hz o ganho diminui taxa de 20dB por dcada, isto , o

ganho atenuado de 10 vezes (20dB) cada vez que a freqncia multiplicada por 10.

Um parmetro importante de um AO a frequncia de ganho unitrio (fU ). Nessa frequncia o ganho de malha

aberta torna-se igual a 1. No grfico da Fig2.6 fU =1MHz.

Outro parmetro importante o produto ganhoxlargura de faixa (GxLF). Para qualquer amplificador vlido:

GxLF = constante, isto , em um amplificador se o ganho aumentar a LF (largura de faixa) diminui ou viceversa. A LF de um amplificador definida como sendo:

LF = fCs - fCi

fCS = frequncia de corte superior fCi = frequncia de corte inferior.

A Fig2.7 mostra uma curva de resposta em frequncia de um amplificador genrico.

No caso de um AO como a fCi = 0 (o AO amplifica tenses CC pois no capacitores de acoplamento entre os

estgios.), a LF = fCS- 20 20.

ifpe.edu.br/cefet/anterior//AOP.htm

12/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.7: Curva de resposta em freqncia genrica.

Para o AO da Fig2.6 temos:

Em malha aberta:

LF = 10Hz Ganho = 100.000

Logo GxLF = 100.000.10Hz =106 Hz=1MHz = fu = freqncia de ganho unitario

Vamos supor que esse AO usado em um amplificador de ganho de malha fechada igual a 10.

A largura de faixa ser igual a :

LF = 106 Hz/10 = 100KHz, isto , o ganho diminuiu, mas para manter o produto GxLF

constante a LF aumentou na mesma proporo. A curva de resposta do amplificador

passa a ser como na Fig2.8.

Fig2.8: Curva de resposta em malha fechada

2.2.4.2 Slew Rate (Taxa de Inclinao)

Para compreendermos o significado de Slew Rate (SR), consideremos o buffer da Fig2.9a

alimentado pelos pulsos da Fig2.9b. A tenso de sada terica e a que realmente se obtm

ifpe.edu.br/cefet/anterior//AOP.htm

13/53

16/05/2011

AMPLIFICADOR OPERACIONAL

esto indicadas nas Fig2.9c e Fig2.9d respectivamente.

(a)

(d)

Fig2.9: Buffer Resposta a um pulso de entrada

ifpe.edu.br/cefet/anterior//AOP.htm

14/53

16/05/2011

AMPLIFICADOR OPERACIONAL

O Slew Rate (SL) ou taxa de inclinao a mxima taxa de variao da tenso de sada com o

tempo, isto :

SR =VS/t.

Na Fig2.9 o AO do exemplo tem um SR de SR = 2V/1s = 2v/s ou

SR = 4V/2s = 2V/s

isto significa que a tenso de sada no pode variar mais

rapidamente do que 2V a cada 1s, e, portanto se o sinal de entrada for mais rpido do que

isso, a sada no responder distorcendo o sinal na sada.

No caso de sada senoidal, VS = VM.senwt, a inclinao (derivada) em cada ponto

varivel sendo dada por: dVS/dt = w.VM.coswt e tem valor mximo ( mxima inclinao) na

origem (wt = 0) e valendo:

dVS/dtMx = w.VM

A Fig2.10 mostra o comportamento da derivada, inclinao ou slew rate, de uma senide,

sendo mxima na origem e zero para wt = 90.

Fig2.10: Comportamento da derivada da senide

A concluso: enquanto o SR do AO for maior do que w.VM no haver distoro, caso contrrio

a senoide comea a ficar achatada.

Exerccio Resolvido

2.9. Um AO tem SR = 2V/s, qual a mxima frequncia que pode ter um sinal de 10V de

amplitude na sada do AO para que no haja distoro por slew rate ?

Soluo:

ifpe.edu.br/cefet/anterior//AOP.htm

15/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Para que no haja distoro

SR >w.VM

2.106V/s > 2. .fmx .10V

f <2.106/20. = 31847Hz

2.2.4.3 Tenso de Offset de Sada

a tenso na sada de um AO quando no tem nenhum sinal na entrada. So trs as

causas da sada ser diferente de zero quando a entrada nula.

2.2.4.3.1 - Tenso de Offset de Entrada ( Vio)

A Fig2.11mostra , de uma forma simplificada, o circuito de entrada de um AO. um

amplificador diferencial.

Fig2.11: Amplificador operacional par diferencial de entrada

Com as duas entradas aterradas, em um AO ideal, como os transistores do par diferencial so

iguais (VBE1 = VBE2 e 1 = 2) a sada (Vs) nula. Na prtica como VBE1VBE2 e 1 2

existir uma tenso entre os coletores que ser amplificada aparecendo na sada como um erro

.

Definimos como tenso de offset de entrada (Vio) a tenso CC que deve ser aplicada em uma

das entradas de forma que a sada seja zero Vio = VBE1 - VBE2

Tipicamente: Vio =2mV

Vs0

ifpe.edu.br/cefet/anterior//AOP.htm

Vs=0

16/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.12: Amplificador operacional tenso de offset de entrada

2.2.4.3.2 - Corrente de Polarizao de Entrada (Ip )

Vamos supor que os transistores de entrada so iguais (VBE1 = VBE2 , 1 = , IB1 = IB2 ),

logo Vio=0). Consideremos o amplificador inversor na Fig2.13a com Ve = 0. A sada no

ser nula (no por causa da tenso de offset de entrada), a causa a corrente que

polariza o AO que ao passar pelo resistor (equivalente) colocado entre a entrada inversora

e o terra gera uma tenso a qual amplificada. Colocando entre a entrada no-inversora e

o terra um resistor de igual valor (RP= R1//R2), o mesmo ser percorrido pela mesma

corrente gerando a mesma tenso, anulando o efeito da tenso na outra entrada e

consequentemente anulando a sada.

Fig2.13: Amplificador operacional correntes de polarizao

Na prtica as duas corrente so diferentes e no manual especificado o valor mdio das

duas:

IP = (IB1 + IB2)/2.

Tipicamente IP = 80nA.

2.2.4.3.3 - Corrente de Offset de Entrada (Iio)

definida como sendo a diferena entre as duas correntes de entrada , com a sada nula

Iio = IB1 IB2

Como vimos a tenso de offset de sada causada pelo descasamento dos transistor no

primeiro par diferencial na entrada de um AO. A correo ( ajuste de offset) importante

quando o AO usado para amplificar tenses CC muito pequenas, em instrumentao

principalmente. Em aplicaes onde o AO amplifica tenses alternadas o ajuste de offset no

muito importante (um capacitor de acoplamento retira a componente CC do sinal).

A Fig2.14 mostra trs formas de se fazer o ajuste, sendo que a ltima ( Fig2.14c) s pode

ser usada se o AO dispor de terminais para ajuste de offset.

ifpe.edu.br/cefet/anterior//AOP.htm

17/53

16/05/2011

AMPLIFICADOR OPERACIONAL

(a)

(b)

(c)

Fig2.14: Ajuste de offset - Circuitos

2.2.4.4 - Curva Caracterstica de Transferncia

o grfico que relaciona sada (Vs) e entrada (Ve) em qualquer amplificador. No caso

de um AO em malha aberta (sem realimentao) Ve = Vi .

A Fig2.15 uma caracterstica tpica de um AO com alimentao de VCC = 12V.

ifpe.edu.br/cefet/anterior//AOP.htm

18/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.15: Amplificador operacional Caracterstica de transferncia

Do grfico da Fig2.15 podemos observar que existe uma faixa muito estreita para valores

de Vi para os quais o ganho constante e o AO tem comportamento linear. Para valores de

Vi compreendidos entre 0,1mV e +0,1mV o ganho constante e vale:

AV =VS/Vi =10V/0,1mV = 100.000 para Vi>0,1mV ou Vi< -0,1mV o AO satura com 10V

ou 10V.

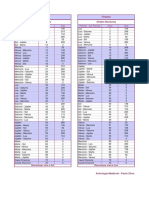

Exemplo de um AO Comercial

Existem vrios tipos de amplificadores operacionais um para cada tipo de aplicao. O

AO mais simples e mais conhecido 741, o qual pode ter dois tipos de encapsulamento,

como indicado na Fig2.16.

Exemplo de um AO Comercial

Fig2.16: Amplificador operacional 741 Encapsulamentos

1 Ajuste de offset

2 Entrada inversora

3 Entrada no-inversora

4 VCC

5 Ajuste de offset

6 Sada

7 +VCC

8 NC(No Conectado)

LIMITES MXIMOS

- 741C

Alimentao

Potncia dissipada

Temperatura de operao

18V

500mW

0C a 70C

OUTROS PARMETROS

Slew rate............................................0,5V/s

Tenso de offset de entrada..............2mV

Corrente de offset de entrada............20nA

Ganho de tenso de malha aberta.....200.000

fu (freqncia de ganho unitario).........1MHz

Resistncia de sada...........................75

ifpe.edu.br/cefet/anterior//AOP.htm

19/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Resistncia de entrada ........................1M

Exerccios Resolvidos

2.10.

Qual a mxima freqncia que pode ter o sinal na entrada do circuito para a sada

no distorcer por slew rate ? Dado: SR = 1V/s

Ve = 0,5.senwt(V)

Soluo:

O ganho do circuito AVf = -10K/1K = -10 de forma que a amplitude da sada ser de

10VP = VM e para no haver distoro deveremos ter:

SL >w.VM , isto ,

1.106Vs > 2. .fMx .10V

da tiramos que

fMx < 106/2. = 159.235Hz.

2.11. Qual a mxima amplitude da senoide de entrada para a sada no distorcer por slew

rate no circuito? A freqncia do sinal de entrada 200KHz. E o slew rate 5V/s

Soluo:

SR > 2. .f.VM

SR = 5.106V/s f = 200.103Hz

VSmx = VM = ?

VM < 5.106/6,28.200.103 4V como o ganho do circuito vale AVf = 1 + 2K2/1K = 3,2 e

como

Ve = VS/AVf ento

VeMx = VSmX/3,2 = 4/3,2 =1,25V

2.12. Esboce a curva de resposta em frequncia em malha aberta de um AO que tem

AV = 105 e fU = =1,5MHz.

Soluo:

Sabemos que GxLF = fU = 1,5MHz

ifpe.edu.br/cefet/anterior//AOP.htm

20/53

16/05/2011

AMPLIFICADOR OPERACIONAL

logo em malha aberta a LF = 1,5.106/105 =15Hz. Resultando o grfico.

2.3 Aplicaes Lineares

Os circuitos a seguir apresentam um comportamento linear entre a entrada e a sada, sendo

que na maioria das vezes esses circuitos so derivados dos circuitos bsicos vistos em 2.2

2.3.1 Amplificador Somador Inversor

O circuito da Fig2.17 derivado do amplificador inversor, tendo mais de uma entrada.

Fig2.17: Amplificador somador inversor

Para obter a expresso de VS = f (v1, v2, V3) faremos as mesmas consideraes j feitas

na analise do amplificador inversor, de forma que :

If= I1 + I2 + I3

onde I1 = v1/R1,

I2 = v2/R2,

I3 = V3/R3

e como VS =-Rf.If

VS = -Rf.(v1/R1 + v2/R2 + V3/R3 )

A tenso de sada uma combinao linear das tenses de entrada.

ifpe.edu.br/cefet/anterior//AOP.htm

21/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Se fizermos R1 = R2 =R3 = R resultar:

VS = -Rf/R.(v1 + v2 + V3 )

E se Rf=R

V S = - ( v1 + v2 + V 3 )

O circuito soma as tenses de entrada e inverte.

Obs: O numero de entradas est limitado capacidade de corrente na sada.

2.3.2 Amplificador Somador No Inversor

um circuito derivado do amplificador no-inversor, Fig2.18.

Fig2.18: Amplificador somador no-inversor

Para obter a expresso da sada em funo das entradas, usamos o teorema da

superposio de efeitos. Com V2 e V3 nulos, obtemos a sada devida s a V1.

Fig2.19: Amplificador somador no-inversor considerando s v1.

Na Fig4.25 V+ = (R/2)/(R + R/2 ).ve1 = ve1/3

VS1 = Ganho.V+ = 3.(ve1/3) = Ve1

Com ve1 e ve3 nulos obtemos a sada (vS2) devida s a Ve2. Resulta um circuito anlogo ao

da Fig2.19 e de maneira semelhante obtemos : vS2= ve2

ifpe.edu.br/cefet/anterior//AOP.htm

22/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Se fizermos Ve1 e Ve2 nulos a sada (VS3) devida s a Ve3 ser: vS3=ve3

Para obter a sada (VS) devido s trs entradas, somamos as trs sadas individuais, isto ,

VS = Vs1 + Vs2 + Vs3 = Ve1 + Ve2 + Ve3

2.3.3 Amplificador Subtrator Amplificador Diferencial

O amplificador subtrator uma combinao do amplificador inversor com o no-inversor,

Fig2.20.

Fig2.20: Amplificador subtrator (Diferencial)

Novamente, usamos o teorema da superposio de efeitos para obter a expresso de VS

=f(ve1,ve2). Primeiramente anulamos ve2 e determinamos VS em funo de ve1 resulta o

circuito da Fig2.21.

Fig2.21: Amplificador subtrator com v2 = 0

Podemos observar que o circuito resultante o amplificador inversor j visto, desta forma

Vs1= - R2/R1.ve1

Agora, anulando ve1 obtemos o circuito da Fig2.22.

ifpe.edu.br/cefet/anterior//AOP.htm

23/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.22: Amplificador subtrator com ve1=0

O circuito resultante o amplificador no-inversor com um divisor de tenso na entrada,desta

forma:

Vs2= Ganho.V+

Ganho = AVf = (R1 + R2)/R1

e V+ = R2/(R1+R2) .ve2

portanto:

Vs2= (R1+R2)/R1.R2/(R1+R2)v2 = R2/R1.ve2

A sada VS no circuito da Fig2.20 obtida somando as sadas parciais Vs1 e Vs2, isto

VS = Vs1+ Vs2 = -R2/R1.ve1 + R2/R1.ve2 = R2/R1.(Ve2 Ve1)

VS= R2/R1.(Ve2 Ve1)

O circuito um amplificador diferencial pois amplifica s a diferena entre duas tenses. Se

v1=v2 a sada ser nula. O ganho diferencial dado por :

Ad = R2/R1.

Se R1=R2

VS = ve2 ve1

Neste caso o circuito realiza a diferena entre duas tenses, da o nome de subtrator

Exerccios Resolvidos

2.13. Calcular VS em cada caso.

ifpe.edu.br/cefet/anterior//AOP.htm

24/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Soluo:

VS = -5K/1K.(2+(-3)) =-5.(-1) = 5V

Simulao: Para ver a soluo com simulao abrir o arquivo

EXRESOLVIDO2_13a.CIR

b.

Soluo:

VS = 5K/1K.(2 3) =5.(-1V) = -5V

Simulao: Para ver a soluo com simulao abrir o arquivo

EXRESOLVIDO2_13b.CIR

2.3.3.1. Amplificador Diferencial de Instrumentao

O amplificador diferencial da Fig2.20 tem como principal desvantagem o a fato da

resistncia de entrada ser dada por R1, o qual por sua vez no pode ser muito alta pois isso

implicaria num valor de R2 muito alto. J que o ganho dado por R2/R1, por exemplo se for

necessrio um ganho de 1000 e R1 da ordem de 1M , o valor de R2 teria de ter um valor

proibitivo da ordem de 1G .Outro problema a dificuldade para se variar o ganho, j que para

isso duas resistncias iguais (R2 ou R1) deveriam ser variadas ao mesmo tempo.

Uma soluo seria o uso de um potencimetro duplo comandado por um nico eixo. Uma

soluo mais simples o circuito da Fig2.23, que alm de ter uma altssima resistncia de

ifpe.edu.br/cefet/anterior//AOP.htm

25/53

16/05/2011

AMPLIFICADOR OPERACIONAL

entrada permite que o ganho seja mudado variando s R1.

Fig2.23: Amplificador diferencial de instrumentao

No circuito da Fig2.23 o ganho calculado por :

Av = VS/Ve = 1 + 2.R2/R1

Onde Ve = Ve2 Ve1

Caso seja necessrio ligar uma carga com um dos terminais aterrados, o circuito da Fig2.24

pode ser usado.

Fig2.24: Amplificador diferencial de instrumentao com carga aterrada.

Com relao ao circuito da Fig2.24 VS = VB VA = V2 V1

Exerccios Resolvidos

ifpe.edu.br/cefet/anterior//AOP.htm

26/53

16/05/2011

AMPLIFICADOR OPERACIONAL

2.14. Calcular VS em cada caso.

Soluo:

No circuito o AO1 e o AO2 so Buffers logo

VA =V2 e VB = V1

E V2 =

= 6V V1 =

= 6,24V

VS = 10.(VB VA) = 10.(6,24 6) =2,4V

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_14.CIR

2.15. No circuito o NTC (Negative Coefficient Temperature) tem uma resistncia de 10K a

250C e 5K a 500C. Quais os valores de tenso indicados pelo voltmetro colocado na

sada que correspondem essas temperaturas ?

ifpe.edu.br/cefet/anterior//AOP.htm

27/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Soluo:

VS = VB - VA Para 250C RNTC =10K

Ve = V2 V1 = 0V

Para 500C

e portanto

RNTC = 5K

logo

Ve = V2 V1 = 8 6 = 2V

Como VS = VS = 10V

ifpe.edu.br/cefet/anterior//AOP.htm

VS = 0V

V2 =

logo

V2 =6V (

) e como V1 = 6V

e tambm VS = 0

= 8V

VS= AV.Ve = ( +2.

).2 = 10V

resulta a escala

28/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_15.CIR

2.16. Dar a expresso da sada VS em funo das entradas V1, V2 e V3.

Soluo:

No ponto

A VA = -2.V1 ( o ganho vale -2)

No ponto

VB = - (V2 + VA) = - ( V2 + (-2.V1)) = 2.V1 V2

NA sada VS = 5.( V3 VB) = 5.(V3 (2.V1 V2)) = 5.V3 - 10.V1 + 5.V2

ou

VS =5.(V3 + V2 ) 10.V1

2.17. Desenhar o grfico de VSxt para o circuito.

Soluo:

ifpe.edu.br/cefet/anterior//AOP.htm

29/53

16/05/2011

AMPLIFICADOR OPERACIONAL

VS = - ( V1 +V2) = - ( 4+ 2.senwt) e o grfico desta funo o seguinte

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_17.CIR

2.18. Desenhar a caracterstica de transferncia (VSxVe)para o circuito.

Dados: VSat = 10V

Ve = V2 - V1

Soluo:

Como

Vs = 10. Ve = 10.(V2 V1) para VS = 10V

ifpe.edu.br/cefet/anterior//AOP.htm

30/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Ve = 1V e para VS = -10V Ve =-1V

resultando o grfico :

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_18.CIR

2.3.4 Operao com Fonte Simples

Quando no for disponvel uma fonte simtrica, atravs de uma polarizao adequada,

podemos usar uma fonte simples. Este tipo de polarizao anloga polarizao classe A

com transistores na qual a tenso de sada quiescente fixada em VCC/2.

2.3.4.1 - Amplificador Inversor

Fig2.25: Amplificador inversor com fonte simples

Em condies quiescente (Ve=0) as tenses no circuito sero:

Tenso na entrada no inversora: VCC/2

ifpe.edu.br/cefet/anterior//AOP.htm

31/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Como no tem corrente em C, R1 e R2, e como as duas entradas tem mesmo potencial, na

sada Vs1 a tenso ser igual a VCC/2 e na sada VS2 a tenso ser igual a zero.

Fig2.26: Amplificador inversor com fonte simples em condies quiescente

As formas de onda do circuito esto representadas na Fig2.27.

Fig2.27: Formas de onda do circuito da Fig2.26

O ganho do circuito calculado por: AVf = R2/R1

Para um bom acoplamento sem perdas ( VSM1= VSM2 ) os capacitores devem ter reatancia

desprezivel em relao resistncia em srie com eles, sendo dimensionados por :

C1 =

C2 =

onde fCi a frequncia de corte inferiort do circuito

Exerccios Resolvido

2.19. Para o circuito da Fig2.25, considerando que a entrada 0,2V de pico/1KHz,

pedem-se: a) Desenhar as formas de onda de entrada e de sada Vs1 e Vs2.

ifpe.edu.br/cefet/anterior//AOP.htm

32/53

16/05/2011

AMPLIFICADOR OPERACIONAL

b) Desenhar a curva de resposta em frequencia do circuito.

c) Desenhar a curva de resposta em freqncia considerando C1=1uF. O que muda?

Soluo:

a) Formas de onda

A tenso de polarizao (tenso na entrada +) vale 6V.

O ganho vale 10 com inverso de fase, desta forma o valor de pico da sada ser 10 vezes

maior que o valor de pico da entrada (0,2V)

b) Curva de resposta em freqncia com C1=10uF

ifpe.edu.br/cefet/anterior//AOP.htm

33/53

16/05/2011

AMPLIFICADOR OPERACIONAL

A freqncia de corte inferior vale aproximadamente 16Hz

c) Curva de resposta em freqncia com C1=1uF

Com C1=1uF a freqncia de corte inferior aumenta para aproximadamente 160Hz

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_19.CIR

2.3.4.2 - Amplificador Inversor

ifpe.edu.br/cefet/anterior//AOP.htm

34/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.28: Amplificador no inversor com fonte simples

Em condies quiescentes (Ve = 0 ) a tenso na entrada no inversora vale VCC/2,

obtida do divisor de tenso. Como as duas entrada ( + e - ) tem mesmo potencial, a tenso na

entrada inversora vale tambm VCC/2, e como no circula corrente por R1 e R2, a tenso na

sada do AO ( VS1) vale VCC/2. Ao aplicar o sinal na entrada (Ve), Fig2.29a, a sada do AO

oscilar em fase em torno de VCC/2 como indicado na Fig2.29b. Depois de C3 a tenso

oscilar em torno de zero, Fig2.29c.

Fig2.29: Formas de onda no amplificador no inversor com fonte simples.

Para um bom acoplamento (VSM1=VSM2) a reatncia dos capacitores deve ser desprezvel em

relao resistncia em serie com cada um deles da resultando que os seus valores devem

ser calculados por :

ifpe.edu.br/cefet/anterior//AOP.htm

35/53

16/05/2011

AMPLIFICADOR OPERACIONAL

C1

C2

C3

fCi = freqncia de corte inferior

Exerccio Resolvido

2.20. No circuito da Fig2.25 dimensionar C 1 e C2 para que o circuito tenha uma frequncia de

corte inferior de 50Hz sabendo-se que R1 = 10K , R2 = 100K, R = 100K e RL = 5K. Se for

usado uma fonte de +12V, calcule qual a mxima amplitude que pode ter a entrada para no

saturar a sada. VSat = 10V.

Soluo:

C1

C2

= 0,318 F

= 0,636 F

Como a sada polarizada em 6V ,e como a saturao ocorre em 10V a mxima sada de

pico ser 4V (10V 6V ) como o ganho vale 10 (100K/10K) a mxima entrada ser

VeM = 4V/10 = 0,4V

Simulao: Para ver a soluo com simulao 0061brir o arquivo EXRESOLVIDO2_20.CIR

2.3.5 Integrador

O integrador e o diferenciador so circuitos que simulam os operadores matemticos integral e

derivada respectivamente. Alm disso, so usados para modificar formas de onda, gerando

pulsos, ondas quadradas, ondas triangulares etc.

A Fig2.30 mostra o circuito bsico de um integrador

Fig2.30: Integrador

ifpe.edu.br/cefet/anterior//AOP.htm

36/53

16/05/2011

AMPLIFICADOR OPERACIONAL

A expresso da tenso de sada em funo da entrada dada por:

Isto , a tenso de sada proporcional integral da tenso de entrada. O sinal de menos se

deve configurao inversora do AO.

Por exemplo, se a entrada for uma tenso constante, a sada ser uma rampa. Se for uma

tenso positiva a rampa ser descendente(inclinao negativa), se for uma tenso negativa a

rampa ser ascendente (inclinao positiva).

(a)

(b)

Fig2.31: Resposta de um integrador a um degrau de tenso ( a ) positiva e ( b )

Negativo.

Na pratica o circuito da Fig2.30 apresenta um problema, como o circuito no tem realimentao

em CC (capacitor circuito aberto em CC) desta forma o ganho muito alto, fazendo o AO

saturar mesmo com tenses da ordem de mV como a tenso de offset de entrada. A soluo

diminuir o ganho em CC colocando em paralelo com o capacitor C um resistor, RP, como na

Fig2.32. O circuito, porm, s se comportar como integrador para freqncias muito acima da

frequncia de corte fC. Abaixo o circuito se comporta como amplificador inversor de ganho igual

a:

Na frequncia de corte a reatncia de C fica igual a RP , isto , XC = RP ou

da obtemos

ifpe.edu.br/cefet/anterior//AOP.htm

37/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Integrador

Amplificador inversor

10.fc

Fig2.31: Integrador com resistor limitar de ganho

Exerccio Resolvido

2.21 Se na Fig2.31 RP = 10K , R = 1K e C = 0,1uF, para que freqncias obteremos na sada

uma onda triangular se a entrada for uma onda quadrada ?

Soluo: A freqncia de corte do circuito :

Portanto, para freqncias muito acima de 160Hz teremos uma boa integrao, isto ,

obteremos na sada uma onda triangular com grande linearidade.

(a)

(b)

Fig2.32: Integrador prtico e curva de resposta em frequncia

Quanto maior for a frequncia do sinal em relao frequncia de corte, melhor ser a

integrao do sinal. A Fig2.33 mostra a sada do integrador quando a entrada quadrada para

dois valores de frequncia do sinal de entrada.

ifpe.edu.br/cefet/anterior//AOP.htm

38/53

16/05/2011

AMPLIFICADOR OPERACIONAL

f=100Hz

(a)

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_21a.CIR

f=2KHz

(b)

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_21b.CIR

Fig2.33: Resposta de um integrador a uma entrada quadrada a diferentes freqncias

Na Fig2.33b a freqncia da onda quadrada de entrada menor do que fC e na Fig2.33c.

A freqncia da onda quadrada muito maior do que fC, resultando uma sada de menor

amplitude mas perfeitamente triangular.

2.3.6 Diferenciador

O diferenciador um circuito que d uma sada proporcional derivada do sinal de entrada . A

derivada um operador dual da integral, e no circuito os componentes trocam de posio,

Fig2.34.

ifpe.edu.br/cefet/anterior//AOP.htm

39/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.34: Diferenciador

A expresso da sada em funo da entrada dada por:

Isto , a tenso de sada proporcional derivada da tenso de entrada. Por exemplo se

a entrada for uma tenso constante a sada ser nula pois a derivada de uma constante

zero, se a entrada for uma rampa, a sada ser constante. O sinal negativo se deve

configurao inversora.

Na prtica o circuito da Fig2.34 sensvel a rudo, tendendo a saturar. A soluo limitar

o ganho em altas freqncias colocando em srie com C uma resistncia RS como na

Fig2.35a. A Fig2.35b a curva de resposta em frequncia do circuito.

(a)

( b)

Fig2.35: ( a ) Diferenciador prtico e ( b ) curva de resposta em freqncia

O circuito da figura 2.35a somente funcionar como diferenciador para freqncias muito abaixo da freqncia

de corte, acima o circuito se comportar como amplificador inversor de ganho igual a R/RS.

O circuito s se comportar como diferenciador se f<< fC, pois nessas condies a reatncia de

C ser muito maior do que RS e na prtica como se no existisse RS e portanto o circuito ter

comportamento semelhante ao da Fig2.34.

Exerccio Resolvido

2.22. Para o circuito da Fig2.35a qual a forma de onda de sada se a entrada quadrada, para as

freqncias de 100Hz e 2KHz.?

ifpe.edu.br/cefet/anterior//AOP.htm

40/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Soluo: A freqncia de corte

Para freqncias muito abaixo de 1600Hz a sada sero pulsos muito estreitos, negativos na borda de subida e

positivos na borda de descida.

(a)

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_22a.CIR

(b)

ifpe.edu.br/cefet/anterior//AOP.htm

41/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_22b.CIR

Fig2.36: Resposta de um diferenciador a uma onda quadrada de ( a ) f<<fc ( b ) f>fc

2.3.7 Conversores Digitais

Sabemos que conforme a informao os circuitos se dividem em digitais e analgicos. Sinais

analgicos podem assumir qualquer valor dentro de uma determinada faixa. Sinais digitais s

podem assumir dois valores de tenses, os quais esto associados a nveis lgicos ( 0 ou 1).

Em sistemas de comunicao a digitalizao de uma informao analgica torna o sinal mais

imune a rudos. Em instrumentos analgicos a leitura feita atravs de um ponteiro em uma

escala. Um voltmetro digital dar uma leitura mais conveniente atravs de um display. O

processo de converso de um sinal analgico em digital envolve de uma forma genrica quatro

etapas: amostragem, reteno, quantificao e codificao. A amostragem e a reteno em

geral so feitas simultaneamente em um circuito chamado amostrador-retentor (sample and

hold). A codificao e a quantizao so feitas num circuito chamado conversor analgico

digital ( A/D). Para obter o sinal original a informao codificada aplicada em um circuito

conversor digital analgico seguido de uma filtragem.

2.3.7.1 Conversor Digital Analgico a Resistor Ponderado

Um conversor D/A d uma sada analgica proporcional entrada digital. Consideremos um

conversor de 4 bits. O circuito da Fig2.37 chamado de conversor ponderado ou resistor de

peso pois cada valor de resistncia est associada posio do bit na palavra binria. Desta

forma o resistor de menor valor estar na posio do MSB (Bit mais significativo ) e o de maior

valor na posio do LSB ( Bit menos significativo ).

Fig2.37: Conversor D/A resistor de peso

Na palavra binria A = A3A2A1A0 os bits podem assumir valor 0 ou 1 os quais

esto associados nveis de tenses V(1) = VR V(0) = 0 V.

A expresso da tenso da sada VS pode ser obtida por superposio sendo dada por :

Genericamente para n bits a expresso acima pode ser generalizada para :

Exerccio Resolvido 2.22

Seja o circuito da Fig2.38 com os seguintes valores R = 8K RL = 1K V(1) =VR=5V V(0) = 0V

com as entradas ligadas a um contador binrio de 0 a 15 ( Por exemplo

7493) a sada ser uma onda em forma de escada tendo 15 degaus cuja amplitude pode

ifpe.edu.br/cefet/anterior//AOP.htm

42/53

16/05/2011

AMPLIFICADOR OPERACIONAL

ser calculada.

A amplitude do degrau vale aproximadamente:

e o valor de pico a pico

VPP = 15.0,217 = 3,26 V

2.4 - Aplicaes No Lineares

Na curva caracterstica do AO em malha aberta pudemos verificar que a sada varia linearmente com

a entrada se esta se mantiver no intervalo entre -0,1mV e 0,1mV. Fora deste intervalo o AO satura. Na

prtica se a tenso de entrada, em mdulo, for muito maior do que o,1mV a curva caracterstica de

transferncia se aproxima da ideal.

2.4.1 Comparador de Zero Inversor

O circuito da Fig2.39a muitas vezes chamado de comparador de zero ou detector de zero no

inversor porque quando a tenso de entrada passar por zero a sada muda de +VSat para -VSat ou vice

versa.

(a)

(b)

Fig2.39: Comparador de zero no inversor e caracterstica de transferncia.

Por exemplo, se Ve = 1.senwt(V) no circuito da Fig2.39a a sada ser uma onda

quadrada de mesma frequncia.

ifpe.edu.br/cefet/anterior//AOP.htm

43/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.40:Formas de onda de entrada e sada do circuito da figura2.39a.

Simulao: Para ver a soluo com simulao abrir o arquivo

2.4.2 Comparador de Zero Inversor

semelhante ao no inversor, porm o sinal aplicado na entrada inversora, Fig2.41a.

(a)

(b)

Fig2.41: Comparador de zero inversor e caracterstica de transferncia

Se for aplicado um sinal senoidal como Ve = 4.senwt(V) na entrada do circuito a sada ser uma onda

quadrada de mesma freqncia, mas defasada de 180 em relao entrada.

ifpe.edu.br/cefet/anterior//AOP.htm

44/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Para ver a soluo com simulao abrir o arquivo

Fig2.42: Comparador de zero inversor e caracterstica de transferncia

2.4.3 Comparador de Zero Inversor com Histerese

Por causa do alto ganho os circuitos comparadores anteriores so sensveis rudos. Quando a

entrada est passando por zero, se aparecer um rudo na entrada a sada oscilar entre +VSat e -VSat

at que o sinal supere o rudo. O circuito ligado na sada entender que o sinal na entrada do

comparador passou varias vezes por zero, quando na realidade foi o rudo que provocou as mudanas

na sada. Para evitar isso deve ser colocada uma imunidade contra ruido chamada de histerese, que

em termos de caracterstica de transferencia resulta no grfico da Fig2.43b.

(a)

(b)

Fig2.43: Circuito comparador de zero com histerese

Observe no circuito da Fig2.43a que a realimentao positiva, (se as entradas fossem invertidas o

circuito seria um amplificador no inversor, ateno portanto !!!). A realimentao positiva faz com

que a mudana de +VSat para -VSat ou vice versa seja mais rpida (s limitada pelo slew rate do AO).

Os valores das tenses que provocam a mudana da sada so calculados por:

ifpe.edu.br/cefet/anterior//AOP.htm

45/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Para mudar de +VSat para -VSat a amplitude do sinal deve ser maior do que V1 e para mudar de - VSat

para + VSat a amplitude do sinal deve ser menor do que - VSat.

Exerccio Resolvido

2.23. Vamos supor o circuito da Fig2.43a. Desenhar a forma de onda de sada se a entrada for

senoidal e de 4VP. e R1=2K e R2=10K

Observe que a forma de onda continua a ser quadrada, porm com uma leve defasagem. Quanto

maior for o valor de pico da senoide em relao V1 e V2 menor ser a defasagem.

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_23.CIR

2.4.4 - Comparador de Nvel Inversor

Num comparador de nvel a tenso de entrada comparada com uma tenso de referencia VR,

Fig2.44, ao invs do terra.

(a)

ifpe.edu.br/cefet/anterior//AOP.htm

46/53

16/05/2011

AMPLIFICADOR OPERACIONAL

(b )

Fig2.44: Comparador de nvel inversor- Circuito ( a ) Curva de transferncia ( b )

Exerccio Resolvido

2.24. Desenhar o grfico de VSxt para o circuito.

VSat =12V

Soluo:

A tenso de referencia a tenso na entrada no inversora e vale :

Enquanto Ve< 2V a sada ser alta ( +12V ) e quando Ve >2V a sada ser baixa ( -12

ifpe.edu.br/cefet/anterior//AOP.htm

47/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Para ver a soluo com simulao abrir o arquivo EXRESOLVIDO2_24.CIR

2.4.5. Monoestvel

Como j visto com transistores , um monoestvel um circuito que tem um estado estvel e um

estado instvel . Na Fig2.45 se a chave estiver aberta a tenso na entrada no inversora ser uma

uma parcela da tenso de sada, que vamos admitir que + VCC, como o capacitor C se carregou

atravs de R o diodo estar conduzindo limitando a tenso em C em aproximadamente 0,7V. Se a

tenso realimentada para a entrada no inversora for maior do que 0,7V esta ser uma condio

estvel, isto , a sada permanece em + VCC indefinidamente.

Fig2.45: monoestvel

Se a chave CH for pressionada momentaneamente, na entrada + aplicada uma tenso negativa

forando a sada para - VCC, o que faz com que seja realimentado agora para a entrada + uma tenso

negativa o que mantm a sada em - VCC. O capacitor C comea a se carregar com polaridade

contrria, o que corta o diodo D. Quando a tenso em C for mais negativa que a tenso na entrada + a

sada voltar para + VCC. O capacitor C voltar a se carregar com valor positivo fazendo o diodo

conduzir grampeando a tenso em C em 0,7V, e o circuito voltar para a condio estvel novamente.

A Fig2.46 mostra graficamente o que j foi explicado.

ifpe.edu.br/cefet/anterior//AOP.htm

48/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Fig2.46: Formas de onda do circuito monoestvel.

A durao da temporizao ( Ti ) dada por :

Aps o circuito ter voltado ao estado estvel ainda demora um tempo para que o circuito possa dar

inicio a um novo ciclo, isto porque apesar da sada ser +VCC o capacitor ainda est se carregando, no

caso atravs de R, o que pode levar a tempos de recuperao da mesma ordem de grandeza de Ti.

Para diminuir o tempo de recuperao do circuito a carga de C deve ser feita atravs de outra

resistncia, no caso da Fig2.47 R6.

Fig2.47: Monoestvel de recuperao rpida

Simulao: Para ver a soluo com simulao abrir o arquivo Monoestavel.CIR

ifpe.edu.br/cefet/anterior//AOP.htm

49/53

16/05/2011

AMPLIFICADOR OPERACIONAL

2.4.6 - Astvel

No circuito da Fig2.48 a sada VS oscilar entre +VCC e - VCC em funo da comparao entre V+ e V- .

Se V+ > V- a sada ser igual a + VCC caso contrario ser - VCC. Se a sada for +VCC, o capacitor se

carregar atravs de R, tendendo para + VCC, quando

nesse instante a sada mudar para - VCC e o capacitor comear a se carregar atravs de R

tendendo a tenso agora para - VCC. Quando a tenso no capacitor for mais negativa que a tenso na

entrada V+ a sada voltar para +VCC e assim sucessivamente.

Fig2.48:Astvel simtrico ( a ) circuito e ( b )formas de onda

ifpe.edu.br/cefet/anterior//AOP.htm

50/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Clique aqui para ver a simulao do circuito da figura48a

O perodo das oscilaes calculado por:

onde

Caso seja necessrio semi perodos diferentes pode ser usado o circuito da Fig2.49.

(a)

(b)

Fig2.49.: Astvel assimtrico ( a ) circuito ( b ) formas de onda

ifpe.edu.br/cefet/anterior//AOP.htm

51/53

16/05/2011

AMPLIFICADOR OPERACIONAL

Simulao: Clique aqui para ver a simulao do circuito da figura49a

TH > TL

4>

R3 e TH < TL

4<

R3

Na Fig2.49 se a sada alta C se carrega atravs de R4 e diodo D2. Quando a sada baixa o

capacitor se carregar atravs de R3 e D1, desta possvel ter o tempo alto ( TH ) diferente do tempo

baixo (TL).

Exerccio Resolvido

2.25. Na Fig2.49 so dados : R1 = 10K = R2 R3 =20K R4 =40K C =0,1F. Desenhar as formas de onda

na sada e no capacitor

Soluo: Primeiramente calculemos os tempos alto e baixo.

2.4.7 Comparador de Janela

Este circuito tambm chamado de detetor de faixa e d uma tenso negativa ou nula na sada

quando a entrada estiver dentro de uma determinada faixa de valores, e d uma sada positiva quando

fora da faixa, Fig2.50.

Fig2.50: Comparador de Janela

Simulao: Clique aqui para ver a simulao do circuito da figura50

No circuito da Fig2.510 temos as seguintes possibilidades considerando VR2 maior

do que VR1 :

a) Ve > VR2 A sada do AO2 +VCC e portanto D2 conduz. A sada do Ao1 -VCC

e portanto D1 estar polarizado reversamente, VS = +VCC.

b) VR1 < Ve < VR2 As sadas dos dois AOs ser - VCC e portanto os dois diodos

estaro cortados a sada VS = 0

ifpe.edu.br/cefet/anterior//AOP.htm

52/53

16/05/2011

AMPLIFICADOR OPERACIONAL

c) Ve < VR1 A sada do AO1 +VCC, logo D1 conduz. A sada do AO2 -VCC e D2

estar aberto, nessas condies a sada VS = + VCC.

O circuito ter a seguinte caracterstica de transferncia:

Fig2.51: Caracterstica de transferncia de um comparador de janela

Na prtica , podemos associar s tenses VR2 e VR1 uma varivel qualquer como temperatura ( T2 e T1

). A tenso Ve por outro lado pode ser obtida num divisor de tenso

que tem um termistor. Enquanto a temperatura estiver dentro de uma determinada faixa

nada acontece (no energiza um rel) . Se a temperatura sair da faixa soa um alarme.

ifpe.edu.br/cefet/anterior//AOP.htm

53/53

Você também pode gostar

- Projetos Em Clp Ladder Baseado No Twidosuite Parte ViiiNo EverandProjetos Em Clp Ladder Baseado No Twidosuite Parte ViiiAinda não há avaliações

- Apostila de Amplificador Operacional - Unifei - ELTA00Documento42 páginasApostila de Amplificador Operacional - Unifei - ELTA00kmi70Ainda não há avaliações

- Conversores AD DADocumento9 páginasConversores AD DAMagno NetoAinda não há avaliações

- Projetos De Instrumentação Eletrônica Usando O ArduinoNo EverandProjetos De Instrumentação Eletrônica Usando O ArduinoAinda não há avaliações

- Aula 02 Equipamentos RevBDocumento111 páginasAula 02 Equipamentos RevBModestoAinda não há avaliações

- Amplificadores Operacionais e Filtros AtivosDocumento18 páginasAmplificadores Operacionais e Filtros AtivosMarcelo OliveiraAinda não há avaliações

- Processamento de Sinais ExerciciosDocumento9 páginasProcessamento de Sinais ExerciciosLiana RitterAinda não há avaliações

- Im Cap04 TransdutoresDocumento58 páginasIm Cap04 TransdutoresAndré ReisAinda não há avaliações

- Transdutores CapacitivosDocumento24 páginasTransdutores CapacitivosaraujoAinda não há avaliações

- LIVRO - Compatibilidade e Interferência Eletromagnética - U4 PDFDocumento45 páginasLIVRO - Compatibilidade e Interferência Eletromagnética - U4 PDFWemerson Rocha Ferreira50% (2)

- An-I - Teoria 1 Características Das Ondas SenoidaisDocumento14 páginasAn-I - Teoria 1 Características Das Ondas SenoidaisZé ZéAinda não há avaliações

- Esquema de TemporizadoresDocumento6 páginasEsquema de TemporizadoresClaudio SerenaAinda não há avaliações

- Manual BJT Regime DinâmicoDocumento35 páginasManual BJT Regime DinâmicoJoão Marques Marques100% (1)

- Aula 2 - Contadores Assíncronos e SíncronosDocumento31 páginasAula 2 - Contadores Assíncronos e SíncronosAnisio André Carlos ManhiçaAinda não há avaliações

- Relatorio Do SemáforoDocumento4 páginasRelatorio Do SemáforoKamila MarinhoAinda não há avaliações

- Captulo 12 - EthernetDocumento7 páginasCaptulo 12 - Ethernetkenshin3000Ainda não há avaliações

- (Apostila) Sensores e TransdutoresDocumento16 páginas(Apostila) Sensores e TransdutoresOscar AvilesAinda não há avaliações

- Iluminação IndustrialDocumento31 páginasIluminação IndustrialShayene KarlaAinda não há avaliações

- Protocolos ModbusDocumento11 páginasProtocolos ModbusredesinformaAinda não há avaliações

- Lista de Exercícios - Trabalho Individual Cap. Ii Vetores No Plano e No EspaçoDocumento4 páginasLista de Exercícios - Trabalho Individual Cap. Ii Vetores No Plano e No EspaçoMisael TeixeiraAinda não há avaliações

- Relatório Técnico Das Aulas Práticas 3Documento5 páginasRelatório Técnico Das Aulas Práticas 3Carol GuimarãesAinda não há avaliações

- Aula 5 Principio Funcionamento Conversor ADDocumento38 páginasAula 5 Principio Funcionamento Conversor ADJonas MolletaAinda não há avaliações

- Ats01 Catalogo 0404 BRDocumento28 páginasAts01 Catalogo 0404 BRJose De NoniAinda não há avaliações

- Dig2Cap4-Conversor DA e ADDocumento38 páginasDig2Cap4-Conversor DA e ADRafael FerreiraAinda não há avaliações

- Relatorio Sensores Indutivos e CapacitivosDocumento8 páginasRelatorio Sensores Indutivos e Capacitivoszinhao2Ainda não há avaliações

- Filtros AtivosDocumento34 páginasFiltros AtivosJulia-e Regina-e AlexandreAinda não há avaliações

- Aula 07 - Multiplexadores e DemultiplexadoresDocumento33 páginasAula 07 - Multiplexadores e DemultiplexadoresXavier Luieno Mualilo0% (1)

- Apostila Ampop PDFDocumento24 páginasApostila Ampop PDFGianny Marcos Fonseca AiresAinda não há avaliações

- Instrumentação e ControleDocumento62 páginasInstrumentação e ControleLuiz Santos ResendeAinda não há avaliações

- Aula LinhasTransmissao Parte2Documento25 páginasAula LinhasTransmissao Parte2Gerson GomesAinda não há avaliações

- Apostila - Fonte de AlimentaçãoDocumento44 páginasApostila - Fonte de AlimentaçãoScriptorAngelAinda não há avaliações

- Conversores DA ADDocumento34 páginasConversores DA ADSilvio Josephik50% (2)

- Ponte-H Com Controle PWM (Mec009)Documento5 páginasPonte-H Com Controle PWM (Mec009)nazuragomesAinda não há avaliações

- Oppenheim - 2010 - 2ed - Cap 02 PDFDocumento57 páginasOppenheim - 2010 - 2ed - Cap 02 PDFDennis De Jesus0% (1)

- Circuito Equivalente Transformadores de PotenciaDocumento17 páginasCircuito Equivalente Transformadores de PotenciaEwerton LiraAinda não há avaliações

- Conceito Básico de EletricidadeDocumento4 páginasConceito Básico de Eletricidadekari1986naAinda não há avaliações

- TransformadoresDocumento16 páginasTransformadoresabraao_george100% (1)

- Relatório de Instrumentação (Finalizado)Documento9 páginasRelatório de Instrumentação (Finalizado)Felippe NarcisoAinda não há avaliações

- Livro Sobre Análise de Circuitos Elétricos - ACEDocumento179 páginasLivro Sobre Análise de Circuitos Elétricos - ACEAlisson Nascimento100% (1)

- Sistemas de ComunicaçãoDocumento49 páginasSistemas de ComunicaçãoDaniel Sá Araújo100% (1)

- Modulacao em Amplitude PDFDocumento14 páginasModulacao em Amplitude PDFIsaac EmmanuelAinda não há avaliações

- Conceitos Básicos de Transmissão de DadosDocumento15 páginasConceitos Básicos de Transmissão de DadosCristianoAinda não há avaliações

- Aula 3 - CONTROLE DIGITAL - Amostragem e Conversores AD-DADocumento34 páginasAula 3 - CONTROLE DIGITAL - Amostragem e Conversores AD-DASilvando MartinsAinda não há avaliações

- Capitulo 07 EDDocumento33 páginasCapitulo 07 EDBrunoPestanaAinda não há avaliações

- TMI - Aulas Teórico-Práticas ResolvidasDocumento142 páginasTMI - Aulas Teórico-Práticas ResolvidasJorge Valente100% (1)

- Todo Tipos de Sensores PDFDocumento35 páginasTodo Tipos de Sensores PDFLindomar Santana Mendonça100% (1)

- Sensores de ProximidadeDocumento20 páginasSensores de ProximidadeHumberto Medeiros CordeiroAinda não há avaliações

- TCC PWMDocumento3 páginasTCC PWMmojuja67% (3)

- Condicionamento de Sinais AnalógicosDocumento23 páginasCondicionamento de Sinais AnalógicosDaniel FonsecaAinda não há avaliações

- Sistores: O Que É Um ResistorDocumento6 páginasSistores: O Que É Um ResistordenistrukAinda não há avaliações

- Os Comparadores de JanelaDocumento12 páginasOs Comparadores de JanelaGaspar ReisAinda não há avaliações

- Processamento Digital de SinaisDocumento17 páginasProcessamento Digital de SinaisLudimilla SabatiniAinda não há avaliações

- Capítulo 1 - Circuitos e Instrumentação-VARIÁVEIS DE CIRCUITO E ELEMENTOS DE CIRCUITOS PDFDocumento106 páginasCapítulo 1 - Circuitos e Instrumentação-VARIÁVEIS DE CIRCUITO E ELEMENTOS DE CIRCUITOS PDFmayaprettiAinda não há avaliações

- EDG3 - Conversores Digital-AnalógicoDocumento72 páginasEDG3 - Conversores Digital-AnalógicoaurivalAinda não há avaliações

- Relatório - TermoparesDocumento5 páginasRelatório - TermoparesJefferson HaagAinda não há avaliações

- Resumo - Amplificadores OperacionaisDocumento4 páginasResumo - Amplificadores OperacionaisNoel_GuaraAinda não há avaliações

- Amplificador de InstrumentaçãoDocumento12 páginasAmplificador de InstrumentaçãoPedroHMoreiraSAinda não há avaliações

- Aplicação Distancia-21-01Documento2 páginasAplicação Distancia-21-01Solange Antonio Carlos100% (1)

- FILMES BonsDocumento1 páginaFILMES BonsDizu ZuleneAinda não há avaliações

- Lenin Charqueiro - Ponte de KelvinDocumento9 páginasLenin Charqueiro - Ponte de KelvinDizu ZuleneAinda não há avaliações

- Dicas para Estudar À DistânciaDocumento1 páginaDicas para Estudar À DistânciaDanyel MoraesAinda não há avaliações

- Partes Físicas - RDocumento33 páginasPartes Físicas - RDizu ZuleneAinda não há avaliações

- Padronizacao Da Comunicacao Atraves Da Tecnologia OPCDocumento10 páginasPadronizacao Da Comunicacao Atraves Da Tecnologia OPCoreiaseccaAinda não há avaliações

- NBR 5410-97Documento128 páginasNBR 5410-97bimbatoluanaAinda não há avaliações

- Search PDF Books - Com Exercicios Resolvidos Do Beer Johnston PDFDocumento3 páginasSearch PDF Books - Com Exercicios Resolvidos Do Beer Johnston PDFDizu Zulene25% (4)

- 03-Preven o ChoqueDocumento25 páginas03-Preven o ChoqueDizu ZuleneAinda não há avaliações

- Cronograma de Atividades Avaliativas - 3º Ano AtualizadoDocumento1 páginaCronograma de Atividades Avaliativas - 3º Ano AtualizadoAdriana SouzaAinda não há avaliações

- A Pronúncia Do Latim A PDFDocumento3 páginasA Pronúncia Do Latim A PDFJoao LucasAinda não há avaliações

- A Diferença (Ontológica) Entre Texto e Norma - Lênio StreckDocumento32 páginasA Diferença (Ontológica) Entre Texto e Norma - Lênio StreckCRISTIANO MAGALHAESAinda não há avaliações

- Machado - Educação Especial Na Escola Inclusiva Políticas, Paradigmas e PráticasDocumento5 páginasMachado - Educação Especial Na Escola Inclusiva Políticas, Paradigmas e PráticasElisangela SilvioAinda não há avaliações

- Português 1S - Unidade 03 - PresencialDocumento17 páginasPortuguês 1S - Unidade 03 - PresencialFórmula On-line 50 ideiasAinda não há avaliações

- APX1 - InformaticaDocumento2 páginasAPX1 - InformaticaVinícius PontesAinda não há avaliações

- Aula 2 - Atividade-Variacao-LinguisticaDocumento12 páginasAula 2 - Atividade-Variacao-LinguisticaPedro Felipe100% (2)

- Ficha Informativa e de Trabalho Dos PronomesDocumento5 páginasFicha Informativa e de Trabalho Dos PronomesSusana Nunes100% (1)

- GramáticaDocumento18 páginasGramáticaAna MonteiroAinda não há avaliações

- Que É Alma - Wikipédia, A Enciclopédia LivreDocumento4 páginasQue É Alma - Wikipédia, A Enciclopédia LivreiasdbrasilAinda não há avaliações

- A Origem Da Língua PortuguesaDocumento7 páginasA Origem Da Língua PortuguesaNoninoNaninoNonino100% (1)

- Línguas Repartidas Como Que de FogoDocumento6 páginasLínguas Repartidas Como Que de FogoRosângela Aparecida Batista100% (1)

- Reforma Protestante e ContrarreformaDocumento16 páginasReforma Protestante e Contrarreformafabio faAinda não há avaliações

- Microsoft Word - Genero Textual AutobiografiaDocumento11 páginasMicrosoft Word - Genero Textual AutobiografiaBarreto RomarizAinda não há avaliações

- PTD Arte Infantil 5 Gasparina.Documento5 páginasPTD Arte Infantil 5 Gasparina.Nilce D de Lima0% (1)

- SERMÃO - No Lugar Certo Na Hora CertaDocumento2 páginasSERMÃO - No Lugar Certo Na Hora CertaIvson NevesAinda não há avaliações

- Habacuque - Wikipédia, A Enciclopédia LivreDocumento4 páginasHabacuque - Wikipédia, A Enciclopédia LivreSaint-Clair LimaAinda não há avaliações

- A Construção Narrativa Da RealidadeDocumento3 páginasA Construção Narrativa Da Realidadejoao coutinhoAinda não há avaliações

- Emoji EmoçõesDocumento9 páginasEmoji EmoçõesSilvia MartinsAinda não há avaliações

- Caderno Palavras Eureka1Documento64 páginasCaderno Palavras Eureka1Olga Sequeira100% (1)

- 6º Ano EF Português Júlia PDFDocumento33 páginas6º Ano EF Português Júlia PDFJéssica OliveiraAinda não há avaliações

- Proprium Cum Ordinario Ad Missam in Vigilia Nativitatis Domini Iesu ChristiDocumento16 páginasProprium Cum Ordinario Ad Missam in Vigilia Nativitatis Domini Iesu ChristiCôro GregorianoAinda não há avaliações

- EXERCICIOS Flip Flops e ContadoresDocumento3 páginasEXERCICIOS Flip Flops e ContadoresmarcosAinda não há avaliações

- Manifestações Artísticas Da Região SudesteDocumento4 páginasManifestações Artísticas Da Região SudesteJulia CarolineAinda não há avaliações

- Artigo 4Documento21 páginasArtigo 4Anderson LeandroAinda não há avaliações

- Modelo de Monografia UFRRJDocumento16 páginasModelo de Monografia UFRRJAlexander Lima BernardoAinda não há avaliações

- A Gramática Das Cores em WittgensteinDocumento438 páginasA Gramática Das Cores em WittgensteinAntonia Mara Neves100% (1)

- Firdaria AbumasharDocumento1 páginaFirdaria AbumasharDiego NovačekAinda não há avaliações

- Primitivo Derivado ColetivoDocumento3 páginasPrimitivo Derivado ColetivoLáizza MartinsAinda não há avaliações

- SEITAS - As Táticas Das Seitas em Torcerem As EscriturasDocumento7 páginasSEITAS - As Táticas Das Seitas em Torcerem As EscriturasPauloAinda não há avaliações