Escolar Documentos

Profissional Documentos

Cultura Documentos

Sistemas Digitais

Enviado por

Rui TavaresTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Sistemas Digitais

Enviado por

Rui TavaresDireitos autorais:

Formatos disponíveis

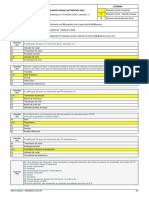

UNIVERSIDADE LUSIADA DE V. N.

DE FAMALICO

FACULDADE DE ENGENHARIA

APONTAMENTOS DA DISCIPLINA DE

SISTEMAS DIGITAIS I

Docente: Prof. Doutor Carlos Alberto Rego de Oliveira

LICENCIATURA EM ENGENHARIA ELECTRONICA E INFORMATICA

1ano

Ano Lectivo de 2005/2006

1

1. INTRODUO

1.1 REPRESENTAES NUMRICAS

Em qualquer area do conhecimento (cincia, tecnologia, economia, ...) trabalha-se

constantemente com valores numericos de determinadas grandezas.

Esses valores numericos podem representar-se de duas Iormas:

- Representao analgica

representam-se por valores de outras grandezas que lhes so proporcionais

variam de Iorma continua

Exemplos.

- tenso de saida de um microIone

(variao entre 0 e 10 V, proporcional a amplitude das ondas sonoras)

- temperatura dada pelo volume do mercurio de um termometro

- horas dadas pelos ponteiros de um relogio

- velocidade de um automovel dada pela posio angular do ponteiro do

velocimetro

- Representao digital

representam-se por simbolos chamados digitos

variam de Iorma discreta (passo a passo)

Exemplos.

- horas dadas por um relogio digital

(hora representada por digitos decimais, varia em passos de um minuto ou um segundo)

- velocidade de um automovel dada por um mostrador digital

Principal diIerena entre as Iormas de representao analogica e digital:

Analogica continua

Digital discreta (passo a passo)

2

1.2 SISTEMAS DIGITAIS E SISTEMAS ANALGICOS

Sistema digital

Combinao de dispositivos projectados para lidar com inIormaes logicas ou com

quantidades Iisicas representadas de Iorma digital, isto e, estas quantidades so podem

assumir valores discretos.

A maior parte dos sistemas digitais processa inIormao representada em binario. O

sistema binario e constituido por dois digitos chamados de digitos binrios ou bits : 0

e 1 (binary digit bit).

Exemplos. - computadores e calculadoras digitais

- equipamento de audio e video digital

- sistema teleIonico

etc.

Sistema analgico

Contem dispositivos que podem manipular quantidades Iisicas que so representadas

de Iorma analogica.

Exemplos. - receptor de radio

- ampliIicador de audio

- equipamento de gravao e reproduo de Iita magnetica

etc.

Vantagens das tecnicas digitais

1 Sistemas digitais so geralmente mais Iaceis de projectar

2 Facil armazenamento de inIormao

3 Maior exactido e preciso

4 A operao do sistema pode ser programada

5 Circuitos digitais so menos aIectados pelo ruido

6 - Um maior numero de circuitos digitais pode ser colocado num

circuito integrado

3

1.3 CONVERSES ANALGICO-DIGITAIS

O mundo real e quase totalmente analogico

A maioria das quantidades Iisicas e originalmente analogica

(por ex. temperatura, presso, posio, velocidade,etc.)

Para tirar proveito das tecnicas digitais, quando estivermos a lidar com entradas e

saidas analogicas, trs passos devem ser seguidos:

1) Converter as entradas analogicas para a Iorma digital

(utilizando conversores A/D)

2) Processar a inIormao digital

3) Converter as saidas digitais de volta a Iorma analogica

(utilizando conversores D/A)

Exemplos.

- sistema de controle de temperatura

- gravao de audio (CDs)

4

2. CIRCUITOS LGICOS BSICOS

2.1 INTRODUO

Os sistemas digitais estabelecem uma relao logica entre os valores binarios

colocados nas suas entradas e os valores binarios que aparecem nas suas saidas.

01001110 01101010

Entradas Saidas

Entradas de um sistema ou circuito digital : variaveis logicas independentes cujos

valores logicos determinam o valor logico da saida. So representadas por letras (A,

B, C, ...) que so tomam dois valores: 0 ou 1.

Sadas de um sistema ou circuito digital: variaveis logicas cujos valores, 0 ou 1,

dependem dos valores logicos das entradas do circuito.

Os sistemas digitais so constituidos por dois tipos de circuitos digitais:

- Circuitos combinatrios: os valores das saidas num dado instante dependem

apenas dos valores das entradas num instante

imediatamente anterior.

- Circuitos sequenciais: os valores das saidas dependem no so dos

valores das entradas mas tambem da sequncia desses

valores (das saidas) ao longo do tempo.

Os circuitos combinatorios so usados para implementar as mais variadas Iunes

logicas e, mais especiIicamente, operaes aritmeticas, codiIicadores e

descodiIicadores, selectores e outros componentes de controlo.

Os circuitos sequenciais so usados para construir outros dispositivos de maior

complexidade, tais como contadores, registadores de deslocamento e memorias.

Os valores binarios das entradas e saidas representam geralmente o nivel de tenso

electrica presente nas ligaes ou nos terminais de entrada e saida do circuito. Por

exemplo, num certo sistema digital, o valor 0 e dado para qualquer tenso situada

entre 0 e 0,8 V, enquanto o valor 1 representa qualquer tenso situada entre 2 e 5 V.

Assim os valores 0 e 1 representam o nivel de tenso de uma variavel, ou, como e

chamado, o seu valor ou nvel lgico.

Outros termos so representados pelos niveis logicos 0 e 1, por exemplo:

Sistema digital

5

Nivel logico 0 Nivel logico 1

Falso Verdadeiro

Desligado Ligado

Baixo Alto

No Sim

Chave aberta Chave Iechada

Qualquer circuito digital pode ser construido utilizando apenas 3 circuitos ou

funes lgicas elementares: OR (OU), AND (E) e NOT (NO).

Outras Iunes basicas podem ser construidas a partir das das trs Iunes

elementares: NAND (NO E), NOR (NO OU), EX OR ou XOR (OU

EXCLUSIVO) e EX NOR ou XNOR ( NO OU EXCLUSIVO).

Portas lgicas (~Gates ou ~logic gates) : designao dos componentes

electronicos que representam as Iunes logicas e dos simbolos que os representam.

Tabela de verdade de um circuito: descreve como o valor logico da saida de um

circuito depende dos valores logicos presentes nas suas entradas.

Para um circuito com N entradas o numero de combinaes possiveis dos seus

valores logicos e 2

N

.

Os circuitos logicos basicos representam-se por simbolos, de acordo com

determinadas normas. As normas existentes so:

- Norma MIL-STD-806 B (Americana) a mais utilizada.

- Norma DIN 40700 (Alem)

- IEC-117-15 (Europeia)

2.2 CIRCUITO LGICO AND (E)

Tabela de verdade:

Entradas Saida

A B S

0 0 0

0 1 0

1 0 0

1 1 1

A operao AND opera da mesma maneira que a multiplicao ordinaria

Expresso para a operao AND: S AB ou S AB

L-se 'S igual a A e B ou 'S igual a A and B

6

Smbolos:

A S A S A & S

B B B

Normas: Americana Alem Europeia

Porta com mais de 2 entradas - Exemplo com trs entradas.

Entradas Saida

A B C S

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 0

1 1 1 1

A saida de uma porta AND tem valor logico 0 quando pelo menos uma da entradas

tem valor 0.

Nota: As combinaes dos bits de entrada, em qualquer tabela de verdade,

escrevem-se por ordem crescente dos numeros decimais que elas representam.

2.3 CIRCUITO LGICO OR (OU)

Tabela de verdade:

Entradas Saida

A B S

0 0 0

0 1 1

1 0 1

1 1 1

Expresso para a operao OR: S A + B

L-se 'S igual a A ou B ou 'S igual a A or B

O sinal ' representa a operao OR e no a adio ordinaria.

7

1

Smbolos:

A S A S A _1 S

B B B

Normas: Americana Alem Europeia

Porta com mais de 2 entradas - Exemplo com trs entradas.

Entradas Saida

A B C S

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 1

A saida de uma porta OR tem valor logico 1 quando pelo menos uma da entradas tem

valor 1.

2.4 CIRCUITO LGICO NOT (NO) ou INVERTER (INVERSOR)

Tabela de verdade:

Entradas Saida

A S

0 1

1 0

Expresso para a operao NOT: S A (1 0 , 0 1)

L-se 'S igual a no A ou 'S igual a not A ou

'S igual ao inverso de A ou 'S igual ao complemento de A.

Smbolos:

A S A S A S

Normas: Americana Alem Europeia

8

A

&

Qualquer circuito logico, independentemente da sua complexidade, pode ser descrito

usando as operaes deIinidas antes. As portas AND, OR e NOT so os blocos

basicos para a construo de sistemas digitais.

Exemplo.

A AB

B

S AB A(BC)

BC

C (BC)A

Existem dois outros tipos de portas logicas, NOR e NAND, que so amplamente

utilizadas em circuitos digitais. Estas combinam operaes AND, OR e NOT de

modo que se torna simples descrever o seu Iuncionamento.

2.5 CIRCUITO LGICO NAND (NO E)

Tabela de verdade :

Entradas Saida

A B S

0 0 1

0 1 1

1 0 1

1 1 0

Expresso para a operao NAND: S A B

Smbolos:

Normas: Americana Alem Europeia

Os mesmos resultados so obtidos se negarmos as entradas de um circuito OR:

9

Tabela de verdade:

Entradas Saida

A B

S

1 1 1

1 0 1

0 1 1

0 0 0

Expresso para a operao NAND: S A + B

Ou seja

Vimos ento que S A B A B

Ou seja, um circuito NAND pode ser implementado com um AND e um NOT ou

com um circuito OR e tantos NOTs quantas Iorem as entradas (isto resulta das leis de

DeMorgan como veremos no capitulo seguinte).

2.6 CIRCUITO LGICO NOR (NO OU)

Tabela de verdade:

Entradas Saida

A B S

0 0 1

0 1 0

1 0 0

1 1 0

Expresso para a operao NOR: S A B

Smbolos:

A S A S A _1 S

B B B

Normas: Americana Alem Europeia

e

10

Os mesmos resultados so obtidos se negarmos as entradas de um circuito AND:

Tabela de verdade:

Entradas Saida

A B

S

1 1 1

1 0 0

0 1 0

0 0 0

Expresso para a operao NOR: S A B

Ou seja

Vimos ento que S B A B A = +

Ou seja, um circuito NOR pode ser implementado com um OR e um NOT ou com

um circuito AND e tantos NOTs quantas Iorem as entradas (isto resulta das leis de

DeMorgan como veremos no capitulo seguinte).

2.7 CIRCUITO LGICO EX OR ou XOR (OU EXCLUSIVO)

Uma das razes para a existncia deste circuito e a sua aplicao nos circuitos de

soma binaria.

Tabela de verdade:

Entradas Saida

A B S

0 0 0

0 1 1

1 0 1

1 1 0

Expresso para a operao XOR: S AB AB A B

Smbolos:

A S A S A 1 S

B B B

Normas: Americana Alem Europeia

11

Portanto

A B

A S

B S

2.8 CIRCUITO LGICO EXNOR ou XNOR (NO OU EXCLUSIVO)

E a negao do XOR.

Tabela de verdade:

Entradas Saida

A B S

0 0 1

0 1 0

1 0 0

1 1 1

Expresso para a operao XNOR: S B A B A B A = +

Smbolos:

A S A S A 1 S

B B B

Normas: Americana Alem Europeia

A S A S

B B

12

2.9 CIRCUITOS INTEGRADOS (CI)

Um circuito integrado e em geral um pequeno cristal de silicio ('chip) composto por

transistores, diodos, resistncias,etc., interligados entre si de Iorma a Iormarem

circuitos de maior ou menor complexidade.

Cada CI pode ter entre algumas a milhes de portas logicas. Por exemplo, os CIs de

portas logicas AND, OR ou NOT, utilizados no laboratorio, tm de 1 a 6 portas, os

CIs contadores tm dezenas de portas e os microprocessadores Pentium ou Power PC

tm milhes de portas.

Existem varias tecnologias de Iabrico de circuitos integrados digitais, sendo as mais

usadas as seguintes:

- TTL : 'Transistor Transistor Logic

Esta usa transistores bipolares.

A sua tenso de alimentao e de 5V.

Um nivel logico 0 e qualquer tenso na Iaixa entre 0 e 0,8 V.

Um nivel logico 1 e qualquer tenso na Iaixa entre 2 e 5 V.

Qualquer tenso que no esteja localizada nestas Iaixas tem um nivel logico

indeterminado e no deve ser usada como entrada em nenhum circuito TTL.

- CMOS : 'Complementary Metal-Oxide Semiconductor

Esta usa MOSFETS canal p e canal n.

A tenso de alimentao varia entre 3 e 18 V, sendo a mais comum 5V.

Neste caso, um nivel logico 0 e qualquer tenso na Iaixa entre 0 e 1,5 V.

Um nivel logico 1 e qualquer tenso na Iaixa entre 3,5 e 5 V.

A Iaixa de indeterminao inclui tenses entre 1,5 e 3,5 V.

13

Exemplos de circuitos integrados das funes logicas basicas.

Cada CI e encapsulado numa embalagem protectora de plastico ou cermica que

Iacilita o seu manuseamento e da qual saem pinos para tornar possivel a ligao do CI

a outros dispositivos.

Um dos tipos de encapsulamento mais comuns e o 'dual-in-line package (DIP) que

tem duas series de terminais, organizados em duas Iilas de lados opostos do

encapsulamento. Os DIPs podem ter 14, 16, 20, 24, 28, 40 ou 64 pinos.

14

Exemplos da estrutura de alguns circuitos integrados TTL das funes logicas

basicas.

15

3. LGEBRA DE BOOLE E SIMPLIFICAO DE CIRCUITOS

lgebra de Boole Tipo de algebra que, baseando-se na teoria de conjuntos, se

aplica a sistemas matematicos que so consideram dois elementos possiveis: 0 e 1.

Quando aplicada aos sistemas digitais permite Iazer a analise e simpliIicao de

expresses e circuitos logicos.

Seja, por exemplo, o seguinte circuito:

So utilizadas 6 portas logicas!

O mesmo circuito simpliIicado, usando a Algebra de Boole :

Agora so so utilizadas 2 portas logicas!

3.1 TEOREMAS FUNDAMENTAIS DA ALGEBRA DE BOOLE

X, Y, Z Variaveis logicas (entradas ou saidas de um circuito logico) que so

podem tomar dois valores: 0 ou 1

16

Teoremas de uma varivel

Relativos a Iuno AND Relativos a Iuno OR

X

0 0 X 0 X

X 1 X X 1 1

X X X X X X

X X 0 X X 1

Relativos a Iuno NOT

X X

Teoremas com mais de uma varivel

Leis da comutatividade

X Y Y X

X Y Y X

Leis da associatividade

(X Y) Z X (Y Z)

(X Y) . Z X (Y Z)

Leis da distributividade

X (Y Z) X Y X Z

X (Y Z) (X Y) (X Z) - esta no se aplica na algebra comum

Leis da absoro

X (X Y) X

X (X Y) X

Dem.: X (X Y) (X 1) X Y) X (1 Y) X 1 X

X ( X Y) (X X) (X Y) X (X Y) X

X ( X Y) X Y

X ( X Y) X Y

Dem.: X ( X Y) (X X) (X Y) 1 (X Y) X Y

X ( X Y) X X X Y 0 X Y X Y

17

(X Y) (X Y) X base dos metodos graIicos de simpliIicao

(X Y) (X Y) X (mapas de Karnaugh)

Dem.: (X Y) (X Y) X (Y Y) X

(X Y) (X Y) X (Y Y) X 0 X

Leis de DeMorgan

Permite transIormar operaes AND em operaes OR e vice-versa.

X Y X Y

X Y + X Y

Exemplos.

1)

( ) ( )

( )

Z A B.C A. B.C A. B C A. B C

2)

( )( )

( ) ( )

( ) ( )

W A B.C D E.F A B.C D E.F

A.B.C D.E.F A. B C D. E F

A.B A.C D.E D.F

Todos os teoremas enunciados se aplicam quando X e Y so expresses que

contm mais do que uma variavel.

3.2 APLICAO DOS TEOREMAS DA LGEBRA DE BOOLE NA

SIMPLIFICAO DE CIRCUITOS LGICOS

3.2.1 Forma de soma de produtos e produto de somas

Soma de produtos expresses que consistem em dois ou mais termos AND

(produtos) conectados as entradas de uma porta OR (somas). Cada termo AND

consiste em uma ou mais variaveis que aparecem individualmente na sua Iorma

complementada ou no.

Exemplos. 1) ABC ABC

2) AB CD ABC D

3) AB CD EF

18

Produto de somas expresses que consistem em dois ou mais termos OR

(somas) conectados as entradas de uma porta AND (produtos). Cada termo OR

consiste em uma ou mais variaveis que aparecem individualmente na sua Iorma

complementada ou no.

Exemplos. 1) (A B C)(A C)

2) (A B)(C D)F

3) (A C)(B D)(B C)

3.2.2 Simplificao algbrica

Na simpliIicao de uma expresso booleana, nem sempre e obvio qual o teorema

a aplicar de modo a obter o resultado mais simples. Alem disso, no existe uma

maneira Iacil de constatar se a expresso obtida esta na sua Iorma mais simples ou

se poderia ser ainda mais simpliIicada. Assim, a simpliIicao algebrica torna-se

Irequentemente um processo de tentativa e erro. No entanto, com a experincia,

obtm-se bons resultados.

Ha dois passos essenciais na simpliIicao algebrica:

1. A expresso original e colocada sob a Iorma de soma de produtos pela

aplicao repetitiva dos teoremas de DeMorgan e pela multiplicao de

termos.

2. Um vez que a expresso original esteja nesta Iorma, os termos AND

(produtos) so veriIicados quanto a Iactores comuns, realizando-se a

Iactorizao sempre que possivel. Com sorte, a Iactorizao resulta na

eliminao de um ou mais termos.

Exemplos.

1)

( ) ( )

( )

( )

( )

Z A.B.C A.B. A.C A.B.C A.B. A C

A.B.C A.B. A C A.B.C A.B.A A.B.C

A.B.C A.B A.B.C A.C. B B A.B

A.C A.B A. C B

2)

( )

( )

( )

( )

Z A.C. A.B.D A.B.C.D A.B.C A.C. A B D A.B.C.D A.B.C

A.A.C A.C.B A.C.D A.B.C.D A.B.C A A .C.B A.C.D A.B.C.D

C.B A.C.D A.B.C.D C.B A.D. C B.C

=

( ) C.B A.D. C B

19

3.3 PRO1ECTO DE UM CIRCUITO LGICO

Procedimento geral:

1 Sintetizar bem o enunciado

2 IdentiIicar as variaveis

3 Fazer a tabela de verdade

4 Deduzir a expresso logica da saida

- Escrever o termo AND para cada caso onde a saida e 1

- Escrever a expresso para a soma de produtos para a saida

5 SimpliIicar a expresso

6 Implementar o circuito

Exemplo prtico:

Pretende-se projectar um circuito para o limpa para-brisas de um automovel.

O motor do limpa para-brisa deve Iuncionar nas seguintes condies:

1- Chave de ignio e comutador do limpa para-brisas ligados

2- Chave de ignio ligada, comutador desligado e escovas do limpa

para-brisas Iora da posio de repouso.

Noutros casos o limpa para-brisas deve estar Iora de Iuncionamento.

1 Sintetizar o enunciado \

2 Identificao das variveis

Variaveis dependentes ou de saida:

Motor do limpa para-brisas (LPB): M

LPB parado: M 0

LPB em movimento: M 1

Variaveis independentes ou de entrada:

Chave na ignio: C

chave OFF: C 0

chave ON: C 1

Comutador do LPB: S Posio das escovas do LPB: P

comutador OFF: S 0 posio normal (repouso): P 0

comutador ON: S 1 outra posio: P 1

20

3 Tabela de verdade

Entradas Saida

C S P M

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

4 Expresso lgica da saida

M 1 para: - C 1 e S 0 e P 1 C.S.P

ou - C 1 e S 1 e P 0 C.S.P

ou - C 1 e S 1 e P 1 C.S.P

A expresso logica e ento: M C.S.P C.S.P C.S.P

A implementao directa do circuito seria

5 Simplificao da expresso

M C.S.P C.S.P C.S.P C.(S.P + S.P + S.P) C.|P.( S + S) S.P|

C.(P S.P) C.(P S)

21

Implementao do circuito

3.4 IMPLEMENTAO DE UM CIRCUITO S COM PORTAS NAND

OU S COM PORTAS NOR

Qualquer circuito pode ser implementado so com portas NAND ou so com portas

NOR.

Processo:

- Aplica-se sucessivamente as leis de DeMorgan a expresso logica do

circuito, de modo que a expresso Iinal contenha so expresses de

NANDs ou NORs.

- Uma variavel e negada se estiver presente em todas as entradas de uma

porta NAND ou NOR (curto-circuito das entradas da porta).

Exemplo: Caso do motor do LPB

M C.(P S) C P S C P.S C.P.S

Implementao so com portas NOR Implementao so com portas NAND

C S

M

P P

S

C M

Exemplo.

Implementar a funo X B.C A.C A.B so com portas NOR de 2 entradas

( ) ( ) ( )

( ) ( ) ( ) ( ) ( ) ( )

X B.C A.C A.B B.C.A.C.A.B B C . A C . A B

B C A C . A B B C A C A B + + +

22

C

B

X

A

3.5 REPRESENTAO DE FUNES

Termos mnimos ou mintermos

- So produtos que envolvem todas as variaveis de uma Iuno F e em que

cada variavel so aparece uma vez (directamente ou pelo seu

complemento).

- Notam-se por m

i

onde i e o inteiro correspondente a representao

binaria, obtida igualando cada variavel a 1 e o seu complemento a 0.

Exemplos.

1) Dada uma Iuno F(A, B, C), por exemplo

2

A.B.C m

0 1 0

2

2

10

2) Dada uma Iuno S(A, B, C, D), por exemplo

9

AB.C.D m

1 0 0 1

2

9

10

Soma cannica de produtos

- E uma soma de mintermos na qual no ha dois mintermos iguais.

- Representa-se por

p

S m =

(lista de mintermos da Iuno).

Exemplo.

1 2 6

S(A, B, C) A.B.C A.B.C A.B.C m m m m(1, 2, 6)

0 0 1 0 1 0 1 1 0

Teorema

Qualquer Iuno F pode ser representada por uma soma canonica de produtos que

incluem todos os mintermos correspondentes aos 1s da Iuno.

Exemplo do motor do limpa para-brisas.

F(C, S, P) M

5 6 7

C.S.P C.S.P C.S.P m m m m(5, 6, 7) =

23

Termos mximos ou maxtermos

- So somas que envolvem todas as variaveis de uma Iuno F e em que

cada variavel so aparece uma vez (directamente ou pelo seu

complemento).

- Notam-se por M

i

onde i e o inteiro correspondente a representao

binaria, obtida igualando cada variavel a 0 e o seu complemento a 1.

(A 0, A 1).

Produto cannico de somas

- E um produto de maxtermos no qual no ha dois maxtermos iguais.

- Representa-se por

s

P M = (lista de maxtermos da Iuno).

Teorema

Qualquer Iuno F pode ser representada por uma produto canonico de somas que

incluem todos os maxtermos correspondentes aos 0s da Iuno.

Exemplo do motor do limpa para-brisas.

F(C, S, P) M ( )

( ) ( ) ( ) ( )

C S P . C S P . C S P . C S P . C S P +

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0

M(0, 1, 2, 3, 4)

Portanto M m(5, 6, 7)

M(0, 1, 2, 3, 4)

Teorema de Shannon

Mintermos e maxtermos permitem uma decomposio das expresses em sub-

-expresses dependentes de subconjuntos de variaveis

Uma Iuno F (X

n-1

, ..., X

0

) pode ser decomposta como

F (X

n-1

, ..., X

0

) X

i

.

F(X

n-1

, ., X

i1

, 1, X

i-1

, ., X

0

)

i

X

.

F(X

n-1

, ., X

i1

, 0, X

i-1

, ., X

0

)

ou da maneira dual

F (X

n-1

, ..., X

0

) |X

i

F(X

n-1

, ., X

i1

, 0, X

i-1

, ., X

0

)| .

. |

i

X

F(X

n-1

, ., X

i1

, 1, X

i-1

, ., X

0

)|

24

Se aplicarmos o teorema duas vezes, primeiro em relao a X

0

e depois em relao a

X

1

obtem-se:

F (X

n-1

, ..., X

0

) X

1

.X

0

.

F(X

n-1

, ., X

2

, 1, 1))

0

1

X X

.

F(X

n-1

, ., X

2

, 1, 0)

1

0

X X .

F(X

n-1

, ., X

2

, 0, 1))

1 0

X X

.

F(X

n-1

, ., X

2

, 0, 0)

Expandindo em relao a (X

k-1

, ..., X

0

) obtem-se:

F(X)

k

2 - 1

i k-1 0 n-1 k

i 0

m (X , ..., X ).F(X , ..., X , i)

i representa a atribuio de valores i (1 ou 0) as variaveis X

k-1

, ..., X

0

ou, por um procedimento dual

F(X)

k

2 - 1

i k-1 0 n-1 k

i 0

M (X , ..., X ) F(X , ..., X , i)

=

(

Exemplo.

Dada uma Iuno F(X

3

, X

2

, X

1

, X

0

), cuja tabela de verdade se apresenta a

seguir, determinar as expresses que decompem as variaveis em dois grupos.

Entradas Saida

X

3

X

2

X

1

X

0

F

0 0 0 0 0

0 0 0 1 0

0 0 1 0 1

0 0 1 1 1

0 1 0 0 1

0 1 0 1 0

0 1 1 0 1

0 1 1 1 0

1 0 0 0 1

1 0 0 1 0

1 0 1 0 1

1 0 1 1 0

1 1 0 0 0

1 1 0 1 1

1 1 1 0 1

1 1 1 1 0

3

3 2 1 0 i 1 0 3 2

i 0

F(X , X , X , X ) m (X , X ).F(X , X , i)

25

X

1

X

0

X

1

3 2 3 2 3 2

3 2 3 2

3 2

3 2 3 2

F(X , X , 0, 0) X .X X .X

F(X , X , 0, 1) X .X

F(X , X , 1, 0) 1

F(X , X , 1, 1) X .X

e

( )

3 2 1 0 1 0 3 2 3 2 1 0 3 2 1 0 1 0 3 2

F(X , X , X , X ) X .X X .X X .X X .X X .X X .X X .X X .X

3.6 MAPAS DE KARNAUGH

- Metodo graIico para representar uma tabela de verdade.

- Destaca as relaes entre as diversas variaveis.

- Permite simultaneamente simpliIicar a expresso logica.

3.6.1 Construo dos mapas de Karnaugh

- Constroi-se uma tabela com 2

n

quadrados ou celulas, correspondendo cada um a

uma combinao dos valores das variaveis (uma linha da tabela de verdade).

- Entre duas celulas adjacentes so pode variar 1 bit no valor das variaveis condio

de adjacncia.

Funo de 2 variveis, X

1

e X

0

O numero de combinaes possiveis das entradas e 2

2

4 4 celulas

Celulas numeradas de 0 a 3:

0 1

0

0

1

1

2

3

0 1

2

3

Exemplo.

X

0

X

1

0

1

0

0

1

1

0

1

2

1

3

0

X

0

linha onde X

1

toma o valor 1

coluna onde X

0

toma o valor 1

ou

1 0 0

0 1 1

0 1 0 2

F(X , X ) X .X X .X

ou F(X , X ) m m m(0, 2)

26

Funo de 3 variveis, X

2

, X

1

e X

0

O numero de combinaes possiveis das entradas e 2

3

8 8 celulas

Variaveis agrupadas 1 2 e celulas numeradas de 0 a 7:

X

1

X

0

X

2

0 0

0 1

1 1

1 0

0

0 1 3 2

1

4 5

7 6

X

0

0 1

3 2

X

2

4 5

7 6

X

1

A ordem em que aparecem os valores das variaveis no e a normal em vez da

sequncia 00 01 10 11 temos 00 01 11 10. Isto deve-se a condio de adjacncia

das celulas. Assim a celula 2 tem a posio trocada com a celula 3 e a 7 com a 6.

Exemplos.

1) F(X

2

, X

1

, X

0

) m(0, 2, 6) M(1, 3, 4, 5, 7)

X

0

0

1

1

0

3

0

2

1

X

2

4

0

5

0

7

0

6

1

X

1

2 1 0 2 0 0

2 1 0 1 2 1

F(X , X , X ) X X X X X X X X X

2) Caso do LPB:

P

0

0

1

0

3

0

2

0

C

4

0

5

1

7

1

6

1

S

ou

F m(5, 6, 7) C.S.P C.S.P C.S.P

27

Funo de 4 variveis, X

3

, X

2

, X

1

e X

0

O numero de combinaes possiveis das entradas e 2

4

16 16 celulas

Variaveis agrupadas duas a duas e celulas numeradas de 0 a 15:

X

1

X

0

X

3

X

2

0 0

0 1

1 1

1 0

0 0

0 1 3 2

0 1

4 5 7 6

1 1

12 13 15 14

1 0

8 9 11 10

X

0

0 1 3 2

4 5 7 6

12 13 15 14

X

2

X

3

8 9 11 10

X

1

Exemplo.

3 2 1 0

F(X , X , X , X ) m(0, 5, 7, 8, 9, 14, 15) M(1, 2, 3, 4, 6, 10, 11, 12, 13)

X

0

0

1

1

0

3

0

2

0

4

0

5

1

7

1

6

0

12

0

13

0

15

1

14

1

X

2

X

3

8

1

9

1

11

0

10

0

X

1

Casos em que a Iuno no esta deIinida para algumas combinaes das entradas - os

valores logicos das celulas correspondentes do mapa de Karnaugh so indeterminados

(celulas 'dc - 'don`t care em ingls).

Ou

3 2 1 0

3 2 1 0

3 1

2 0

3

2 1 0

0

3 2 1

F(X , X , X , X ) X X X X

X X X X

X X X X

X X X X

2 1 0

3

2 1

3 0

3 2 1 0

X X X X

X X X X

X X X X

28

0 0

1

1

2

2

3 3

X 0 ou X 1

X 0

X X

X 1

X 0 ou X 1

Exemplo de representao.

1) F(X

2

, X

1

, X

0

) m(0, 4,5) e d.c.(2,3)

X

0

0

1

1

0

3

X

2

X

X

2

4

1

5

1

7

0

6

0

X

1

X

0

ou

0

1

1

0

3

2

X

2

4

1

5

1

7

0

6

0

X

1

3.6.2 Obteno de expresses simplificadas

- Combinam-se as celulas adjacentes que tm 1`s em grupos.

O n de celulas de cada grupo e sempre igual a 2

k

(1, 2, 4, 8, ...).

- A expresso obtida e uma soma de produtos, correspondentes aos grupos, em

que cada um tem n - k Iactores (n n de variaveis da Iuno).

Exemplos de agrupamentos.

1)

X

0

0

0

1

0

3

0

2

1

4

1

5

1

7

0

6

1

12

1

13

1

15

0

14

0

X

2

X

3

8

0

9

0

11

0

10

1

X

1

(elimina-se X

0

e X

3

: 4 - 2 Iactores)

2 0 3 0 1

3 2 1 0 3 1 1 2

F(X , X , X , X ) X X X X X X X X X

0

1

2

2 2

3

3 0

1

X 0

X 1

(elimina-se X )

X 0 ou X 1

X 0

X .X .X

=

1

2 0

3 1

2

3

0

X 0

X 1

X X X X

X 0

X 1

29

2)

X

0

0

1

1

3

2

1

4

5

7

6

12

13

15

14

X

2

X

3

8

1

9

11

10

1

X

1

3)

X

0

0

1

1

3

1

2

4

1

5

7

6

1

12

1

13

15

14

1

X

2

X

3

8

9

1

11

1

10

X

1

2

0

X X

4)

X

0

0

1

1

3

1

2

4

5

1

7

1

6

12

13

1

15

1

14

X

2

X

3

8

9

1

11

1

10

X

1

Os cantos so adjacentes

neste caso, 1 grupo de 4

produto de 4 2 2 Iactores:

2 0 X X

Lados opostos so adjacentes

neste caso, 2 grupos de 4

0

2

X X

Grupo de 8 eliminam-se 3 variaveis:

X

0

30

5) Utilizao dos 'don`t care:

X

0

0

1

1

0

3

0

2

0

4

1

5

0

7

1

6

X

12

0

13

0

15

1

14

X

X

2

X

3

8

0

9

X

11

0

10

0

X

1

Nota: a adjacncia das celulas situadas nos lados e cantos do mapa de Karnaugh resulta do Iacto de

este provir da planiIicao de uma Iigura geometrica denominada toro, cuja Iorma e semelhante a

uma cmara de ar de um pneu.

Exemplos de aplicao.

1) Caso do motor do LPB

P

0

0

1

0

3

0

2

0

C

4

0

5

1

7

1

6

1

S

2)

2 1 0

F(X , X , X ) m(0, 1, 3, 5, 7)

X

0

0

1

1

1

3

1

2

0

X

2

4

0

5

1

7

1

6

0

X

1

Consideram-se os 'don`t care

(X`s) adjacentes aos 1`s como 1`s

para Iormar grupos maiores

X

2

X

1

F M C.S P.C C.(P S)

2 1

2 1 0 0

F(X , X , X ) X X X

31

3)

3 2 1 0

F(X , X , X , X ) m(0, 2, 5, 6, 7, 8, 10, 15)

X

0

0

1

1

0

3

0

2

1

4

0

5

1

7

1

6

1

12

0

13

0

15

1

14

0

X

2

X

3

8

1

9

0

11

0

10

1

X

1

4)

3 2 1 0

F(X , X , X , X ) m(2, 5, 8, 12, 14) e d.c.(0, 9, 11, 13, 15)

X

0

0

X

1

0

3

0

2

1

4

0

5

1

7

0

6

0

12

1

13

X

15

X

14

1

X

2

X

3

8

1

9

X

11

X

10

0

X

1

1 1 3 2 0

3 2 1 0 3 2 0

F(X , X , X , X ) X X X X X X X X

3.6.3 Funes com mais de 4 variveis

- 5 variaveis X

4

, X

3

, X

2

, X

1

, X

0

: 2

5

32 combinaes possiveis

Constroem-se 2 mapas parciais, cada um com 4 variaveis (X

3

, X

2

, X

1

, X

0

) um

para X

4

e outro para

4 X .

Os grupos nas mesmas posies, num e noutro mapa, consideram-se adjacentes.

- 6 variaveis X

5

, X

4

, X

3

, X

2

, X

1

, X

0

: 2

6

64 combinaes possiveis.

Constroem-se 4 mapas parciais, cada um com 4 variaveis (X

3

, X

2

, X

1

, X

0

)

dois para X

5

e dois para 5 X . Os mapas de X

5

so um para X

4

e outro para 4 X .

O mesmo para os mapas de 5 X

2 0 3

3 2 1 0 2 0

3

2 1 2 1 0

F(X , X , X , X ) X X X X X

X X X X X X

32

4. SISTEMAS DE NUMERAO

4.1 SISTEMAS PRINCIPAIS

Sistemas mais usados na tecnologia digital:

SISTEMA N DE ALGARISMOS

OU DIGITOS BASE

ALGARISMOS OU

DIGITOS

Decimal 10

0, 1, 2, 3, 4, 5, 6, 7, 8, 9

Binario 2 0, 1

Octal 8 0, 1, 2, 3, 4, 5, 6, 7

Hexadecimal 16 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

A, B, C, D, E, F

Sistema de base B n de algarismos e B

Um numero N, numa determinada base r , e constituido por uma parte inteira e uma

parte Iraccionaria:

N

r

d

j

... d

3

d

2

d

1

d

0

, d

-1

d

-2

d

-3

...d

-k

Parte inteira Parte fraccionria

j + 1 dgitos k dgitos

MSD LSD

~Most Significatif Digit ~Less Significatif Digit

Dgito mais significativo Dgito menos significativo

Qualquer numero N de base r pode ser decomposto num polinomio de potncias de

base r:

N

r

d

j

... d

3

d

2

d

1

d

0

, d

-1

d

-2

d

-3

...d

-k

d

j

r

j

... d

3

r

3

d

2

r

2

d

1

r

1

d

0

r

0

d

-1

r

-1

d

-2

r

-2

d

-3

r

-3

...d

-k

r

-k

M

10

converso

para base 10

Cada digito tem um valor numerico (d

j

, ... d

-k

) e

e um valor posicional (r

j

, ..., r

-k

)

33

4.1.1 Sistema decimal

Um numero pode ser decomposto em potncias de 10

Exemplo.

1485,53

10

1 x 10

3

4 x 10

2

8 x 10

1

5 x 10

0

5 x 10

-1

3 x 10

-2

4.1.2 Sistema binrio

E o mais utilizado em sistemas digitais

Base 2 utiliza dois digitos: 0 e 1 (binary digit bit)

Outros exemplos.

11101

2

1 x 2

4

1 x 2

3

1 x 2

2

0 x 2

1

1 x 2

0

29

10

Contagem em binario:

34

11011,101

2

1 x 2

4

1 x 2

3

0 x 2

2

1 x 2

1

1 x 2

0

1 x 2

-1

0 x 2

-2

1 x 2

-3

27,625

10

4.1.3 Sistema Octal

Outro exemplo.

56433,12

8

5 x 8

4

6 x 8

3

4 x 8

2

3 x 8

1

3 x 8

0

1 x 8

-1

2 x 8

-2

23835,15625

10

Contagem em octal:

35

4.1.4 Sistema Hexadecimal

Outro exemplo.

D71A,25

16

13 x 16

3

7 x 16

2

1 x 16

1

10 x 16

0

2 x 16

-1

5 x 16

-2

55066,1445

10

Outros sistemas

Exemplo.

5431

4

5 x 4

3

4 x 4

2

3 x 4

1

1 x 4

0

397

10

4.2 CONVERSES ENTRE SISTEMAS

4.2.1 Converso do sistema decimal para outros sistemas

- Parte inteira e convertida segundo o metodo das divises sucessivas (divide-se

pela base do sistema pretendido)

Contagem em hexadecimal:

36

Exemplo de converso de decimal para binario.

1 4 3 2

0 3 7 1 2

1 1 1 3 5 2

1 1 5 1 7 2

1 1 8 2

LSD 0 4 2

0 2 2

0 1 143

10

10001111

2

MSD

Exemplo de converso de decimal para octal.

1 4 3 5 8

6 3 1 7 9 8

7 5 1 9 2 2 8

3 3 6 2 1435

10

2633

8

Exemplo de converso de decimal para hexadecimal.

6 4 9 0 1 6

0 0 9 0 4 0 5 1 6

1 0 0 8 5 2 5 1 6

0 5 9 1 6490

10

195A

16

A

- Parte Iraccionaria e convertida segundo o metodo das multiplicaes

sucessivas (multiplica-se pela base do sistema pretendido)

Exemplo de converso de decimal para binario.

0,754 x 2 1,508

0,508 x 2 1,016

0,016 x 2 0,032

0,032 x 2 0,064

0,064 x 2 0,128 0,754

10

0,11000...

2

etc.

37

Exemplo de converso de decimal para octal.

0,754 x 8 6,032

0,032 x 8 0,256

0,256 x 8 2,048 0,754

10

0,602...

8

etc.

Exemplo de converso de decimal para hexadecimal.

0,754 x 16 12,064 C 12

0,064 x 16 1,024

0,024 x 16 0,384 0,754

10

0,C10...

16

etc.

O numero de digitos Iinal na parte Iraccionaria depende da preciso

pretendida

Para converter um numero decimal com parte inteira e parte Iraccionaria para

outro sistema utilizam-se os dois metodos reIeridos

Exemplo. como 15

10

1111

2

e 0,341

10

0,0101...

2

ento 15,341

10

1111,0101...

2

4.2.2 Converso entre os sistemas binrio e octal

A relao entre as bases e 8 2

3

Cada digito octal e representado por 3 bits

Exemplos.

7 5 6

- octal

1 1 1 1 0 1 1 1 0 - binario 756

8

111101110

2

76,16

8

111110,001110

2

10110

2

010110

2

26

8

4.2.3 Converso entre os sistemas binrio e hexadecimal

A relao entre as bases e 16 2

4

Cada digito hexadecimal e representado por 4 bits

38

Exemplos.

8 A 4 2

- hexadecimal

1 0 0 0 1 0 1 0 0 1 0 0 0 0 1 0 - binario

8A42

16

1000101001000010

2

2B4

16

001010110100

2

4.2.4 Converso entre os sistemas octal e hexadecimal

Passa-se de um dos sistemas para o sistema binario e deste para o outro.

4.3 OPERAES ARITMTICAS NOS VRIOS SISTEMAS

4.3.1 Sistema Binrio

Adio

Tabuada da adio: 0 0 0

1 0 1

0 1 1

1 1 0 e vai um ('Carry transporte)

Exemplo

13

10

7

10

20

10

1102

2

111

2

10100

2

1 1 0 1

1 1 1

1 0 1 0 0

1 1 1 1 transporte

Um mais um da dois (10

2

) - escreve-se 0 e gera-se o transporte 1 para a soma

seguinte

Subtraco

Tabuada da subtraco: 0 - 0 0

1 - 0 1

0 - 1 1 e vai um ('Borrow pede emprestado)

1 - 1 0

39

Exemplo.

20

10

7

10

13

10

1 pedido emprestado coluna seguinte

10100

2

- 111

2

1101

2

0 1 10 1 10

1 0 1 0 0 ou 1 0 1 0 0

- 1 1 1 - 1 1 1

0 1 1 0 1 0 1 1 0 1

1 1 1 1 e vai um ('Borrow`)

18

10

5

10

13

10

10010

2

101

2

1101

2

1 0 0 1 0

- 1 0 1

0 1 1 0 1

1 1 1 e vai um

Multiplicao

Tabuada da multiplicao: 0 x 0 0

1 x 0 0

0 x 1 0

1 x 1 1

Exemplo.

21

10

x 13

10

273

10

10101

2

x 1101

2

100010001

2

1 0 1 0 1

x 1 1 0 1

1 0 1 0 1

0 0 0 0 0

1 0 1 0 1

1 0 1 0 1 .

1 0 0 0 1 0 0 0 1

1 1 1 1 1 1

Diviso

Tabuada da diviso: 0 : 0 0

0 : 1 0

1 : 1 1

40

Exemplo.

24

10

: 7

10

3

10

resto 3

10

11000

2

: 111

2

11

2

resto 11

2

0 10 1 10

1 1 0 0 0 1 1 1

- 1 1 1 1 1

0 1 10 10

0 1 0 1 0

- 1 1 1

0 0 0 1 1

4.3.2 Sistema Octal

Adio

Soma-se digito a digito como em decimal. Caso o resultado seja maior ou igual a

8 subtrai-se 8, obtendo-se o resultado da adio e vai 1 ('Carry- C)

Exemplo.

7

8

3

8

12

8

passos: 7 3 10 ~ 8

10 8 2 e vai 1(C)

26

8

55

8

102

8

26

8

passos: 6 5 11 ~ 8

55

8

11 8 3 e vai 1(C)

103

8

2 5 1(C) 8 8

8 8 0 e vai 1 (C)

Subtraco

Quando o algarismo de cima (subtraendo ou aditivo) e inIerior ao de baixo

(subtractor ou subtractivo) adiciona-se ao primeiro 8 e subtrai-se como em

decimal, obtendo-se o resultado da subrtraco e vai 1 ('Borrow- B).

Exemplo

325

8

56

8

247

8

325

8

passos: 5 6 5 8 13

- 56

8

13 6 7 e vai 1(B)

247

8

2 5 2 8 10

10 5 1(B) 4 e vai 1(B)

3 1(B) 2

41

Multiplicao

Metodo semelhante

Exemplo. 56

8

x 14

8

1050

8

5 6

8

passos: 4 x 6 24

10

30

8

x 1 4

8

4 x 5 20

10

24

8

3 0 1 x 6 6

10

6

8

2 4 1 x 5 5

10

5

8

6

5 6 4 3 13 ~ 8

1 0 5 0

8

13 8 5 e vai 1(C)

5 2 1(C) 8 8

8 8 0 e vai 1(C)

4.3.3 Sistema Hexadecimal

- Metodos semelhantes aos do sistema octal

Exemplos

Adio: A 3 7

16

7 B 7 11 18 ~ 16

5 9 B

16

18 16 2 e vai 1(C)

F D 2

16

9 3 1(C) 13 D

A 5 10 5 15 F

Subtraco: A A 5

16

5 16 21

- 6 E D

16

21 D 21 13 8 e vai 1(B)

3 B 8

16

A 16 10 16 26

26 E - 1(B) 26 14 1(B)

11 B e vai 1(B)

A 6 1(B) 10 6 1(B) 3

Multiplicao: A B

16

C x B 12 x 11 132

10

84

16

x 4 C

16

C x A 12 x 10 120

10

78

16

8 4 4 x B 4 x 11 44

10

2C

16

7 8 4 x A 4 x 10 40

10

28

16

2 C

2 8 . 8 8 12 28 ~ 16

3 2 C 4

16

28 16 12 C e vai 1(C)

7 2 8 1(C) 18 ~ 16

18 16 2 e vai 1(C)

2 1(C) 3

42

4.4 REPRESENTAO DE NUMEROS BINRIOS COM SINAL

4.4.1 Sistema sinal-grandeza ou sinal-magnitude

Neste sistema, para representar o sinal de um numero, acrescenta-se um bit de sinal

(geralmente o bit mais a esquerda) ao grupo de bits que representa esse numero:

0 (zero) para sinal + (positivo)

1 (um) para sinal - (negativo)

Exemplo

Num sistema que trabalha com 7 bits, incluindo o bit de sinal, temos por exemplo:

0 1 1 0 1 0 0 5 2

10

1 1 1 0 1 0 0 - 5 2

10

grandeza 52

10

grandeza 52

10

bit de sinal () bit de sinal (-)

Nas operaes, neste sistema, sinal e grandeza so tratados separadamente.

Exemplos

1 1 1 0 (-6) 0 1 1 0 (6)

0 1 0 0 (4) - 0 1 0 0 (4)

1 0 1 0 (-2) 0 0 1 0 (2)

A implementao de circuitos para este sistema e complexa. Calculadoras e

computadores normalmente no o usam.

4.4.2 Sistema do complemento para dois

Este e o sistema mais utilizado.

Noo do complemento para um

Exemplo 1 0 1 1 0 1 n binario original

trocam-se os bits

0 1 0 0 1 0 complemento para 1 do binario original

43

Noo do complemento para dois

Exemplo 1 0 1 1 0 1 equivalente binario de 45

0 1 0 0 1 0 complemento para 1

1 adiciona-se 1

0 1 0 0 1 1 complemento para 2

0 1 0 1 1 1 e o complemento para 2 de 1 0 1 1 0 1

Representao de numeros com sinal usando o complemento para dois

n positivo: - grandeza e representada na Iorma directa

- um bit de sinal 0 e colocado a esquerda do MSD

Exemplo. 0 1 0 1 1 0 1 45

10

Binario directo

bit de sinal ()

n negativo: - grandeza e representada na Iorma de complemento para dois

- um bit de sinal 1 e colocado a esquerda do MSD

Exemplo. 1 0 1 0 0 1 1 - 45

10

Complemento para dois de 1 0 1 1 0 1 (45

10

)

bit de sinal (-)

Exemplos.

- Representar o numero 13

10

num sistema que usa o complemento para dois e

um total de 5 digitos binarios

13

10

0 1 1 0 1

2

44

- Representar o simetrico de 9

10

, num sistema binario que usa o complemento

para dois e um total de 5 digitos binarios

9

10

1 0 0 1 ou (melhor) 0 1 0 0 1 9

10

0 1 1 0 1 0 1 1 0

1 1

0 1 1 1 1 0 1 1 1 - 9

10

- 9

10

1 0 1 1 1

- Representar o numero -2

10

, num sistema binario que usa o complemento para

dois e um total de 5 digitos binarios

0 0 0 1 0 2

10

1 1 1 0 1

1

1 1 1 1 0 - 2

10

: representao de 2 em complemento para dois

com 5 bits

- Determinar o valor decimal dos seguintes ns binarios com sinal representados

no sistema complemento para 2.

a) 0 1 1 0 0

1 1 0 0 12

10

0 1 1 0 0 12

10

b) 1 1 0 1 0

1 1 0 1 0 n original

0 0 1 0 1

1

0 0 1 1 0 ( 6) , logo o original e -6

Caso especial na representao de complemento para dois

Se um n com sinal tem 1 como bit de sinal e 0s para todos os bits de grandeza, o seu

equivalente decimal e 2

N

, onde N e o n de bits da grandeza

Exemplos. 1 0 0 0 - 2

3

- 8

1 0 0 0 0 - 2

4

- 16

1 0 0 0 0 0 - 2

5

- 32

etc.

45

A gama de representao de um n com sinal com N bits de grandeza e |- 2

N

, 2

N

1|

Exemplos.

- Determinar o intervalo de ns decimais com sinal representados com um

total de 4 bits usando o sistema de complemento para dois.

Total de 4 bits N 3

O maior n negativo e - 2

3

- 8 (1000)

O maior n positivo e 2

3

- 1 7 (0111) R . |-8, 7|

- Qual o intervalo de valores decimais sem sinal que pode ser representado

com 1 bvte?

1 byte 8 bits 0 0 0 0 0 0 0 0

2

0

10

1 1 1 1 1 1 1 1

2

255

10

R. |0, 255| (256 valores)

- Qual o intervalo de valores decimais com sinal que pode ser representado

com 1 bvte?

1 byte 8 bits N 7

maior valor negativo: 1 0 0 0 0 0 0 0 - 2

7

- 128

10

maior valor positivo: 0 1 1 1 1 1 1 1 2

7

- 1 127

10

R. |-128, 127| (256 valores)

4.4.3 Adio no sistema de complemento para dois

Operao realizada sobre os bits de grandeza tambem e Ieita sobre o bit de sinal

Caso I: dois ns positivos

Exemplo. 0 1 0 0 1 (9)

0 0 1 0 0 (4)

0 1 1 0 1 (13)

bit de sinal

46

Caso II: um n positivo e um outro menor negativo

Exemplo. 0 1 0 0 1 (9)

1 1 1 0 0 (-4)

1 0 0 1 0 1 (5)

bit de sinal

este bit ('Carry) no e considerado

(sistema trabalha com 5 bits)

Caso III: um n positivo e outro maior negativo

Exemplo. 1 0 1 1 1 (-9)

0 0 1 0 0 (4)

1 1 0 1 1 (-5) - rep. em complemento para dois

bit de sinal (-)

Caso IV: dois ns negativos

Exemplo. 1 0 1 1 1 (-9)

1 1 1 0 0 (-4)

1 1 0 0 1 1 (-13) - rep. em complemento para dois

bit de sinal (-)

este bit ('Carry) no e considerado

(sistema trabalha com 5 bits)

o resultado da soma e 1 0 0 1 1 (13)

Caso V: dois numeros iguais em grandeza mas de sinal contrario

Exemplo. 1 0 1 1 1 (- 9)

0 1 0 0 1 (9)

1 0 0 0 0 0 (0) - rep. em complemento para dois

bit de sinal ()

este bit ('Carry) no e considerado

4.4.4 Subtraco no sistema de complemento para dois

Procedimento:

1 - Muda-se o subtractivo para um numero de igual grandeza mas de sinal

contrario.

2 - Adiciona-se o subtraendo ao n obtido no 1 passo

47

A subtraco transIorma-se assim numa adio e portanto, o circuito logico que

Iaz a adio Iaz tambem a subtraco.

Os ns a subtrair tm que estar escritos com o mesmo n de bits.

Exemplos.

1) 0 1 0 0 1 0 0 1 0 0 0 0 1 0 1

(9) (4) 5

1: 0 0 1 0 0 (4) 2: 0 1 0 0 1 (9)

1 1 1 0 0 (- 4)

1 1 0 1 1 1 0 0 1 0 1 (5)

1

1 1 1 0 0 (-4) bit de sinal

bit no considerado

2) 0 1 0 0 1 1 1 0 1 0 0 1 1 0 1

(9) (-4) (13)

1: 1 1 1 0 0 (-4) 2: 0 1 0 0 1 ( 9)

0 0 1 0 0 ( 4)

0 0 0 1 1 0 1 1 0 1 (13)

1

0 0 1 0 0 (4) bit de sinal

4.4.5 Overflow aritmtico

Exemplos.

1) 0 1 0 0 1 (9)

0 1 0 0 0 (8)

1 0 0 0 1

grandeza incorrecta

bit de sinal incorrecto

O resultado seria 17 mas este necessita de mais de 4 bits de grandeza para

ser representado

48

2) 1 0 1 1 1 0 0 1 1 1

(-9) (8) - 17

1: 0 1 0 0 0 (8) 2: 1 0 1 1 1 (- 9)

1 1 0 0 0 (- 8)

1 0 1 1 1 1 0 1 1 1 1

1

1 1 0 0 0 (-8) grandeza incorrecta

bit de sinal incorrecto

bit no considerado

Neste caso o resultado seria 17 mas este necessita de mais de 4 bits para

ser representado.

Num caso e noutro dizemos que houve 'overIlow.

O 'overIlow e detectado examinando o bit de sinal do resultado e

comparando-o com os bits de sinal dos ns que so adicionados.

4.5 CDIGOS

Por vezes no e pratico o processamento de numeros representados no sistema binario

puro, devido a conduzirem a um conjunto de digitos que no tm uma converso directa

para o sistema decimal normalmente utilizado pelo homem.

Por outro lado, a necessidade de armazenar na memoria dos dispositivos digitais outros

caracteres que no sejam numeros, como por exemplo, letras ou simbolos graIicos,

levou a utilizao de codigos que, embora baseados no sistema binario, permitem

representar nuns casos os caracteres ou simbolos que no sejam numericos, e noutros,

os numeros, mas de uma maneira mais Iacil de converter para decimal. Temos assim:

Codigos numericos permitem a representao de numeros

Codigos alfanumericos permitem a representao de caracteres numericos e

outros, tais como letras, simbolos graIicos e caracteres

especiais.

4.5.1 Cdigos BCD (~Binary Coded Decimal) - Decimal Codificado em Binrio

Para converter um n decimal para o codigo BCD, cada digito decimal e convertido no

seu binario equivalente puro. So usados 4 digitos binarios para cada decimal.

49

Cdigo BCD natural, NBCD ou BCD8421

Exemplo.

924

10

escreve-se em binario puro 1 1 1 0 0 1 1 1 0 0

2

Em codigo BCD natural, NBCD ou BCD8421 temos:

Pesos 8 4 2 1 8 4 2 1 8 4 2 1

1 0 0 1 0 0 1 0 0 1 0 0

9 2 4

ou seja 924

10

1 0 0 1 0 0 1 0 0 1 0 0

NBCD

Como e evidente a converso de decimal para NBCD ou vice-versa e muito mais rapida

do que entre decimal e binario puro.

Ha combinas de digitos binarios que no so possiveis em codigo NBCD

Exemplo. 1 1 0 1 no tem correspondncia no codigo NBCD

porque 1 1 0 1 8 4 0 1 13

10

1 1 0 1 e uma combinao ilegitima

se aparecer no codigo NBCD temos um erro

Decimal NBCD

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

1010

1011

1100

1101

1110

1111

Combinaes

legitimas

Combinaes

ilegitimas

50

Outros Cdigos BCD....

2421* 4321 5221 6321 7421 3321* 4421 5311 6221

6421 4311* 5211* 6311 7321

* codigos auto-complementares

Exemplo. BCD4421

Pesos 4 4 2 1 4 4 2 1 4 4 2 1

1 1 0 1 0 0 1 0 0 1 0 0

9 2 4

Assim 924

10

1 1 0 1 0 0 1 0 0 1 0 0

BCD4421

Codigos auto-complementares: permitem determinar o complemento em relao a 9 de

um numero decimal por simples inverso dos seus bits.

( Complemento em relao a 9 de um numero decimal:

Exemplos. 9 99 999

- 4 - 67 - 924

5 32 075

5 e o complemento em relao a 9 de 4

32 e o complemento em relao a 9 de 67

75 e o complemento em relao a 9 de 924 )

Exemplo. BCD2421

Pesos 2 4 2 1 2 4 2 1 2 4 2 1

1 1 1 1 0 0 1 0 0 1 0 0

9 2 4

Assim 924

10

1 1 1 1 0 0 1 0 0 1 0 0

BCD2421

Invertendo os bits: 1 1 1 1 0 0 1 0 0 1 0 0

0 0 0 0 1 1 0 1 1 0 1 1

0 7 5

075

10

e de Iacto o complemento em relao a 9 do numero 924

10

51

Cdigo Excesso 3 ou XS-3

Tambem e um codigo BCD.

Obtem-se do NBCD somando 3 a cada digito:

Decimal NBCD

XS-3

0 0000 0011

1 0001 0100

2 0010 0101

3 0011 0110

4 0100 0111

5 0101 1000

6 0110 1001

7 0111 1010

8 1000 1011

9 1001 1100

XS-3 e auto-complementar.

Cdigo de GRAY e XS-3 GRAY

So codigos BCD.

O codigo de Gray e um codigo ciclico ou progressivo para passar de um digito

decimal para o seguinte basta mudar o valor de um unico bit. No e auto-complementar.

O codigo XS-3 GRAY obtem-se do codigo de Gray como o XS-3 se obtem do NBCD

deslocando 3 posies o codigo de Gray.

Decimal GRAY

XS-3 GRAY

0 0000 0010

1 0001 0110

2 0011 0111

3 0010 0101

4 0110 0100

5 0111 1100

6 0101 1101

7 0100 1111

8 1100 1110

9 1101 1010

52

O XS-3 GRAY e auto-complementar. Para obter o complemento dos digitos decimais

basta inverter o bit mais signiIicativo. Por exemplo:

0 1 1 1 (2

10

) 9

- 2

1 1 1 1 (7

10

) 7

4.5.2 Cdigos Dois em Sete ou ~Two out Seven

Utilizam 7 bits para cada digito decimal.

Desvantagem: - obriga a ter mais elementos para representar um numero neste tipo de

codigos

Vantagens: - detecta erros, visto que, para cada digito decimal, so dois bits e que no

so zero (0).

- apresenta uma carga sempre igual para o circuito uma vez que so dois

bits em cada digito so igual a um (1).

Exemplo.

Decimal Bi-quinario

Qui-binario

Pesos 5 0 4 3 2 1 0 8 6 4 2 0 1 0

0 0 1 0 0 0 0 1 0 0 0 0 1 0 1

1 0 1 0 0 0 1 0 0 0 0 0 1 1 0

2 0 1 0 0 1 0 0 0 0 0 1 0 0 1

3 0 1 0 1 0 0 0 0 0 0 1 0 1 0

4 0 1 1 0 0 0 0 0 0 1 0 0 0 1

5 1 0 0 0 0 0 1 0 0 1 0 0 1 0

6 1 0 0 0 0 1 0 0 1 0 0 0 0 1

7 1 0 0 0 1 0 0 0 1 0 0 0 1 0

8 1 0 0 1 0 0 0 1 0 0 0 0 0 1

9 1 0 1 0 0 0 0 1 0 0 0 0 1 0

4.5.3 Cdigos alfanumricos

Codigos mais utilizados:

53

Codigo ASCII - 'American Standard Code Ior InIormation Interchange

E utilizado em comunicaes telegraIicas e em computadores.

Cada caracter e constituido em geral por 7 bits sendo o LSD o b1

e o MSD o b7

Exemplos: caracter A: 1 0 0 0 0 0 1 4 1

HEX

caracter ?: 0 1 1 1 1 1 1 3 F

HEX

caracter 6: 0 1 1 0 1 1 0 3 6

HEX

No caso do codigo ter 8 bits o b8 pode ser 0 ou 1 de acordo com o pretendido.

A tabela seguinte apresenta o codigo ASCII juntamente com o hexadecimal (HEX)

para caracteres:

54

Codigo BAUDOT ou ITA 2 ou TELEX de 5 BITS

ITA 'International Telegraph Alphabet

E utilizado em comunicaes telegraIicas(telex)

Codigo BCD Extenso , de 8 bits, ou EBCDIC

EBCDIC 'Extended Binary Coded Decimal Interchange Code.

E utilizado em computadores.

4.6 DETECO DE ERROS

Quando uma inIormao e transmitida de um dispositivo para outro existe a

possibilidade da ocorrncia de erros, de modo que o receptor no recebe a inIormao

idntica aquela que Ioi enviada pelo transmissor.

A causa principal de erros de transmisso so ruidos electricos, que consistem em

Ilutuaes aleatorias da tenso ou corrente, e que esto presentes em diIerentes graus em

todos os circuitos electricos.

Exemplo.

1

0

x

O ruido altera o nivel logico de sinal, como acontece no ponto x. Quando ocorre, o

receptor pode interpretar incorrectamente o bit como 1 logico, que no Ioi o que o

transmissor enviou.

A probabilidade de ocorrncia de erros em circuitos digitais e muito baixa. No entanto,

os sistemas transmitem milhares ou mesmo milhes de bits por segundo e, mesmo com

uma taxa de ocorrncia baixa, um erro ocasional pode ocorrer. Por esta razo muitos

sistemas digitais empregam algum metodo de deteco (e as vezes correco) do erro.

Transmissor

Receptor

55

4.6.1 Mtodo da paridade

Um bit extra, o bit de paridade, e anexado ao grupo de bits do codigo que e transmitido.

Paridade par

O bit de paridade e escolhido de modo que o n total de uns (1) no grupo de bits do

codigo seja par

Exemplos. 1 0 0 0 0 1 1 letra C no codigo ASCII

1 1 0 0 0 0 1 1 n par de 1s

bit de paridade adicionado

1 0 0 0 0 0 1 letra A

0 1 0 0 0 0 0 1 n par de 1s

bit de paridade adicionado

0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0

paridade par erro

O receptor veriIica a paridade (conta o numero de 1s), detecta o erro e, de algum

modo, pede para os dados serem novamente enviados.

Paridade impar

O bit de paridade e escolhido de modo que o n total de uns (1) no grupo de bits do

codigo seja impar.

O bit de paridade e usado para detectar qualquer erro de apenas 1 bit que ocorra durante

a transmisso de um codigo de um lugar para outro. O erro e detectado mas no e

corrigido.

Se dois bits estiverem errados no ha mudana na paridade e o metodo no Iunciona.

Portanto, este metodo e usado em situaes em que a probabilidade de erro simples e

muito baixa e a de erro duplo e zero.

Transmissor Receptor

56

Paridade longitudinal e transversal

Exemplo de utili:ao em codigo NBCD

7 9 3 8

10

vai ser transmitido

Digito decimal NBCD NBCD bit de paridade impar

7 0 1 1 1 0 0 1 1 1

9 1 0 0 1 1 1 0 0 1

3 0 0 1 1 1 0 0 1 1

8 1 0 0 0 0 1 0 0 0

bits de paridade adicionados as linhas paridade longitudinal

Digito decimal NBCD NBCD bit de paridade impar

7 0 1 1 1 0 1 1 1

9 1 0 0 1 1 0 0 1

3 0 0 1 1 0 0 1 1

8 1 0 0 0 1 0 0 0

1 0 1 0 bits de paridade adicionados as

colunas paridade transversal

Digito decimal NBCD NBCD bit de paridade impar

7 0 1 1 1 0 0 1 1 1

9 1 0 0 1 1 1 0 0 1

3 0 0 1 1 1 0 0 1 1

8 1 0 0 0 0 1 0 0 0

1 0 1 0

paridade transversal e longitudinal simultaneamente

Neste ultimo caso.

- Um erro simples muda a paridade da linha e coluna correspondentes ao bit errado

e detectado e corrigido.

- Um erro duplo na mesma linha no muda a paridade da linha mas muda de duas

colunas e detectado mas no corrigido.

- Um erro duplo em linhas diIerentes mas na mesma coluna no muda a paridade

da coluna mas muda a paridade das linhas pode ser detectado mas no

corrigido.

- Um erro duplo em linhas e colunas diIerentes muda a paridade de ambas as linhas

e colunas e detectado mas no corrigido.

- Erros triplos podem ser detectados.

57

4.6.2 Cdigos de Hamming

Codigos de Hamming so uma classe de codigos que utilizam combinaes de bits de

veriIicao de paridade para detectar e corrigir erros.

Um grupo de bits de veriIicao de paridade (p

i

) e adicionado ao grupo de bits de dados

(d

i

). As posies (i) dos bits de paridade (p

i

) correspondem as potncias de 2. As

posies dos bits so numeradas de 1 a r, iniciando a 1.

Um determinado bit de paridade e determinado a partir dos bits de dados com 1 na

posio correspondente ao bit de paridade.

Por exemplo p

2

(0 1 0) sera determinado a partir de d

3

(0 1 1) , d

6

(1 1 0) e d

7

(1 1 1)

num codigo de Hamming com 7 bits (4 de dados e 3 de paridade).

O valor de cada bit de paridade sera obtido de modo que cada conjunto, Iormado por

esse bit de paridade e os bits de dados que lhe do origem, tenha uma paridade par ou

impar.

Consideremos por exemplo os numeros decimais de 0 a 9 codiIicados em codigo de

Hamming de 7 bits e paridade par.

Digito

Decimal

Codigo de Hamming

Pesos 0 0 1 0 2 4 8

Posio 1 2 3 4 5 6 7

Bit

p

1

p

2

d

3

p

4

d

5

d

6

d

7

0 0 0 0 0 0 0 0

1 1 1 1 0 0 0 0

2 1 0 0 1 1 0 0

3 0 1 1 1 1 0 0

4 0 1 0 1 0 1 0

5 1 0 1 1 0 1 0

6 1 1 0 0 1 1 0

7 0 0 1 0 1 1 0

8 1 1 0 1 0 0 1

9 0 0 1 1 0 0 1

Os bits de paridade so determinados por

p

1

d

3

d

5

d

7

p

2

d

3

d

6

d

7

- XOR (OU EXCLUSIVO) ' adio sem 'carry

p

4

d

5

d

6

d

7

58

Metodo de deteco e correco de erro simples (admitindo que no ocorre um erro

duplo)

1 - Forma-se o binario (C

2

C

1

C

0

)

2

onde C

2

p

4

d

5

d

6

d

7

C

1

p

2

d

3

d

6

d

7

C

0

p

1

d

3

d

5

d

7

Posio 1 2 3 4 5 6 7

Bit p

1

p

2

d

3

p

4

d

5

d

6

d

7

C

2

C

1

C

0

2 - Converte-se para decimal: (C

2

C

1

C

0

)

2

X

10

X posio de erro

3 - Troca-se o bit na posio em que ha erro

Exemplo. 742

10

vai ser transmitido

Decimal: 7 4 2

Codigo de Hamming: 0 1 1 0 1 0 0 0 1 0 1 0 1 0 0 0 1 1 0 0 1

Suponhamos que o sinal recebido e:

0 1 1 0 1 0 0 0 1 1 1 0 1 0 0 0 1 1 0 0 1

Analisando o 2 grupo de bits, correspondentes ao 4, temos:

C

2

1 0 1 0 0

C

1

1 1 1 0 1

C

0

0 1 0 0 1

(C

2

C

1

C

0

)

2

0 1 1

2

3

10

Erro detectado na posio 3 ! Troca-se o bit.

Se admitirmos que podem ocorrer erros duplos (mas que a probabilidade de ocorrerem

erros triplos e desprezavel), para os detectar, adiciona-se mais um bit de paridade extra,

na posio 0, que e calculado de modo a manter a paridade de todos os bits (de paridade

e dados) par ou impar. Assim, na deteco de erros, temos que:

59

Se um bit esta errado pelo menos uma das veriIicaes dos bits de paridade (C

2

, C

1

ou C

0

) Ialha ( 0) e a paridade global Ialha. O erro pode ser corrigido do modo

indicado antes.

Se dois bits esto errados, uma ou mais das veriIicaes dos bits de paridade Ialha

mas a paridade global estara correcta. O erro e detectado mas no pode ser

corrigido.

Exemplos

60

5. CIRCUITOS COMBINATRIOS

INTRODUO

ConIorme ja Ioi dito antes, designam-se por circuitos digitais combinatorios os

circuitos cujas saidas so exclusivamente Iuno das suas entradas, sem

interveno do ultimo valor em que se encontravam essas saidas.

Os circuitos combinatorios so criados implementando a respectiva equao

booleana de Iuncionamento com portas logicas e cumprem multiplas Iunes

dentro dos circuitos digitais.

O nivel de complexidade dos circuitos combinatorios pode chegar ao caso de haver

milhes de entradas, portas logicas, interconexes e saidas. A compreenso destes

circuitos Iaz-se por meio da sua decomposio em circuitos basicos mais simples.

Neste capitulo vamos descrever alguns dos principais circuitos combinatorios

basicos, tais como gerador de bit de paridade, gerador do complemento para dois,

conversores, codiIicadores, descodiIicadores, comparadores, somadores,

subtractores, multiplexers e desmultiplexes.

5.1 GERADOR DO BIT DE PARIDADE

O XOR permite acrescentar directamente um bit de paridade par a um grupo de

dois bits.

Tabela de verdade de um XOR:

Entradas Sada

A

o

B

o

X

0 0 0

0 1 1

1 0 1

1 1 0

Para n bits utilizam-se n-1 XORs de duas entradas ou um XOR com um numero

de entradas igual ao numero de variaveis ou varios XORs com um numero de

entradas superior a dois.

Para obter uma paridade impar inverte-se a saida do ultimo XOR do circuito, ou

seja, utiliza-se uma porta XNOR .

61

Exemplo : Acrescentar um bit de paridade par a um nmero binrio de 4 bits

Tabela de verdade:

ENTRADAS

SADA

NMERO BINRIO

DECIMAL

A

3

A

2

A

1

A

0

BIT DE

PARIDADE

P

0 0 0 0 0 0

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 1

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 0

11 1 0 1 1 1

12 1 1 0 0 0

13 1 1 0 1 1

14 1 1 1 0 1

15 1 1 1 1 0

O gerador do bit de paridade para 4 bits e (veriIicar):

ou, utilizando uma porta XOR de 4 entradas,

62

De notar que a porta XOR e, ao mesmo tempo, um gerador e um detector da paridade.

Exemplo prtico: Gerao/Deteco do bit de paridade numa transmisso

Tabela dos XORs

Se X Y e S 0

Se X = Y e S 1 Existe deturpao do sinal na linha entre o

gerador e o detector

63

5.2 GERADOR DO COMPLEMETO PARA DOIS DE UM NUMERO

BINRIO

Exemplo : gerar o complemento para dois de um nmero binrio de 4 bits

Tabela de verdade:

Mapas de Karnaugh correspondentes

O mapa relativo a B

1

dispensa-se pois B

1

A

1

A

8

A

4

A

2

A

1

B

8

B

4

B

2

B

1

64

Destes obtem-se:

( )

( )

( )

( )

( )

2 1 2 1 2 1 2

4 4 2 4 1 4 2 1 4 2 1 4 2 1

4 2 1 4 2 1 4 2 1

8 8 4 8 2 8 1 8 4 2 1

8 4 2 1 8 4

B A .A A .A A A

B A .A A .A A .A .A A . A A A .A .A

A . A A A . A A A A A

B A .A A .A A .A A .A .A .A

A . A A A A . A A

+ +

+

( )

( )

2 1 8 4 2 1

A A A A A

Implementao do circuito:

65

5.3 CONVERSORES

Circuitos que convertem codigos

Exemplo: ABCD XS-3 (Excesso 3)

Tabela de verdade

Mapas de Karnaugh correspondentes

E

0

E

1

E

2

E

3

66

Destes mapas resulta

0

1

2

3

E A

E A.B A.B A B

E A.C B.C A.B.C

E A.C B.C D

Aplicando as leis de DeMorgan a E

2

e E

3

obtem-se

( ) ( )

( ) 2

E C A B . A B .C

E3 A.C.B.C.D

| |

|

\ .

Implementao do circuito

67

5.4 CODIFICADORES E DESCODIFICADORES

5.4.1 Codificadores

So circuitos que convertem um numero representado no sistema decimal para a

sua representao num codigo BCD ou binario natural. Tambem se utilizam para

codiIicar simbolos e caracteres alIabeticos. Possuem n saidas e ate 2

n

1 entradas.

CodiIicadores sem prioridade

So circuitos que no admitem a activao simultnea de mais de uma entrada,

porque, se isso acontecer, aparece o codigo errado nas suas saidas. O meio de

ultrapassar isto e utilizar codigos com prioridade.

CodiIicadores com prioridade

So codiIicadores em que, no caso de ocorrer a activao simultnea de varias das

suas entradas, aparecera nas suas saida o codigo da entrada de maior prioridade

(normalmente a entrada de maior valor).

Exemplo: Codificador Decimal - Binrio

E Iacil veriIicar que o circuito que realiza esta codiIicao e o seguinte:

Na pratica utiliza-se o CI 74147 para eIectuar esta codiIicao. Este CI e um

codiIicador com prioridade cujo Iuncionamento e descrito pela tabela seguinte. De

notar que as entradas e saidas apresentam-se de modo complementar.

68

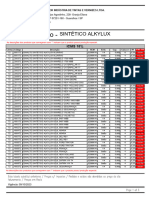

Entradas Saidas

1 2 3 4 5 6 7 8 9 S3 S2 S1 S0

1 1 1 1 1 1 1 1 1 1 1 1 1

x x x x x x x x 0 0 1 1 0

x x x x x x x 0 1 0 1 1 1

x x x x x x 0 1 1 1 0 0 0

x x x x x 0 1 1 1 1 0 0 1

x x x x 0 1 1 1 1 1 0 1 0

x x x 0 1 1 1 1 1 1 0 1 1

x x 0 1 1 1 1 1 1 1 1 0 0

x 0 1 1 1 1 1 1 1 1 1 0 1

0 1 1 1 1 1 1 1 1 1 1 1 0

A Iigura seguinte apresenta a implementao pratica do codiIicador. Neste circuito

as entradas e saidas so activadas a um nivel logico baixo (L ou 0).

5.4.2 Descodificadores

So circuitos que realizam a operao inversa dos codiIicadores. Dispem de n

entradas e dum numero de saidas menor ou igual a 2

n

. Nestes circuitos so uma

saida estara activa para cada combinao das entradas.

69

Exemplo 1: DESCODIFICADOR BINRIO PURO DECIMAL

Tabela de verdade

Mapas de Karnaugh - 10 mapas podem reduzir-se a um so:

Deste mapa tiramos, para cada uma das saidas:

0 A.B.C.D 5 A.B.C

1 A.B.C.D 6 A.B.C

2 A.B.C 7 A.B.C

3 A.B.C 8 A.D

4 A.B.C 9 A.D

D C B A

70

Implementao do circuito:

Os CIs 7442 e 7445 so descodiIicadores BCD para decimal. Nestes circuitos a

saida e activada a um nivel logico baixo (L ou 0), enquanto as restantes

permanecem a um nivel alto (H ou 1).

A Iigura seguinte mostra a implementao pratica de um descodiIicador utilizando

um CI 7445, com accionamento de LEDs nas suas saidas.

BCD/DEC

A

B

C

D

0

1

2

3

4

5

6

7

8

9

Representao esquematica de um

descodiIicador BCD-Decimal:

71

Exemplo 2 : DESCODIFICADOR BCD 7 SEGMENTOS

Circuito que alimenta um displav (mostrador) de sete segmentos construidos com

sete LEDs , os quais podem ser acesos para escrever os digitos de 0 a 9, alem de

algumas letras ou outros caracteres.

Tabela de verdade (LEDs acesos com nivel logico 1 modo catodo comum)

72

Deste mapa resulta a expresso

d B.D B.C A.D C.D B.C.D

Apos a obteno de todas as expresses implementa-se o circuito.

O displav de sete segmentos pode ser construido no modo de nodo comum ou de

catodo comum.

nodo comum Catodo comum

Os CIs 7446 e 7447 so descodiIicadores de 7 segmentos cujas saidas so

activadas a um nivel baixo (L), utilizando-se, por isso, para nodo comum.

O CI 7448 e um descodiIicador de 7 segmentos cujas saidas so activadas a um

nivel alto (H), utilizando-se, por isso, para catodo comum.

Mapa de Karnaugh para o d:

73

5.5 COMPARADORES

Os circuitos comparadores so circuitos que comparam a grandeza de dois

numeros binarios de n bits e indicam qual deles e maior, menor ou se so iguais.

5.5.1 Comparador de dois bits

Tabela de verdade

Entradas Sadas

A

o

B

o

A

o

B

0

A

o

> B

0

A

o

< B

0

0 0 1 0 0

0 1 0 0 1

1 0 0 1 0

1 1 1 0 0

Funes para as sadas

( )

0 0 0 0 0 0 0 0

B A B A B A B A = + = =

( ) B A B A

0 0 0 0

= >

( )

0 0 0 0

B A B A = <

Implementao do circuito

74

5.5.2 Comparador de dois nmero binrios de dois bits

A A

1

A

0

B B

1

B

0

Tabela de verdade simplificada tendo em conta a comparao de dois bits

Entradas Sadas

A

1

, B

1

A

o

, B

o

A B A > B A < B

A

1

~ B

1

X 0 1 0

A

1

B

1

X 0 0 1

A

1

B

1

A

o

~ B

0

0 1 0

A

1

B

1

A

o

B

0

0 0 1

A

1

B

1

A

o

B

0

1 0 0

Funes para as sadas

( ) ( ) ( )

0 0 0 0

B A B A B A = =

( ) ( ) B A B A B A B A

1 1 0 0 1 1

+ = >

( ) ( )

1 1 0 0 1 1

B A .B A B A B A + = <

Implementao do circuito

75

5.5.3 Caso geral : Comparador de dois nmero binrios de n+1 bits

A A

n

A

n-1

.A

2

A

1

A

0

B B

n

B

n-1

. B

2

B

1

B

0

Determinao da sada (A B)

Dois numeros so iguais se os digitos do mesmo peso so iguais, isto e

A

n

B

n

, A

n-1

B

n-1

, . , A

1

B

1

, A

0

B

0

Ento, pelo que vimos, a expresso de (A B) e:

( ) ( ) ( ) ( ) ( )

0 0 1 1 1 - n 1 - n n n

B A B A ... B A B A B A = =

Utilizando a notao