Escolar Documentos

Profissional Documentos

Cultura Documentos

Prova Circuitos Digitais Solucao

Enviado por

Philipp HassDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Prova Circuitos Digitais Solucao

Enviado por

Philipp HassDireitos autorais:

Formatos disponíveis

lOMoARcPSD|34579991

Prova - Circuitos Digitais - Solução

Circuítos Digitais (Universidade Federal de Santa Maria)

A Studocu não é patrocinada ou endossada por nenhuma faculdade ou universidade

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

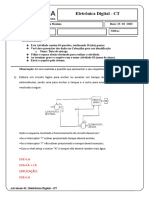

Ministério da Educação

Universidade Federal de Santa Maria

Departamento de Eletrônica e Computação

Acadêmico(a): RA:

Curso Engenharia Elétrica Período: 16 de outubro de 2017

Disciplina ELC 1112 – Circuitos Digitais II Valor da Avaliação

Professor Marcos H. Maruo

Avaliação escrita 35% da nota final

1) Considere que um projeto digital requer um circuito contador em código Gray de mó-

dulo 8 para funcionar corretamente. A sequência (periódica) em código Gray com módulo 8

é 0, 1, 3, 2, 6, 7, 5, 4 devendo reciclar novamente para zero após o dígito 4. Projete um circuito

digital, utilizando flip-flops tipo JK, que reproduza a sequência em código Gray com módulo 8.

i) (0,5) Determine o diagrama de transição de estados;

A sequência indicada tem módulo-8 portanto o número mínimo de Flip-flops no projeto é

⌈log2 8⌉ = 3. A contagem envolve algarismos entre 0 e 7 portanto a contagem pode ser co-

dificada diretamente nos estados do contador com o diagrama de transição de estados abaixo

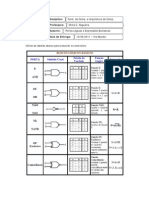

ii) (1,0) Determine a tabela de ativação;

Baseado no diagrama de transição de estados determinado anteriormente

e na tabela de ativação do flip-flop tipo JK, a tabela de ativação é

Estado Atual Estado Futuro Ativação

E2 [n] E1 [n] E0 [n] E2 [n + 1] E1 [n + 1] E0 [n + 1] J2 K2 J1 K1 J0 K0

0 0 0 0 0 1 0 X 0 X 1 X

0 0 1 0 1 1 0 X 1 X X 0

0 1 0 1 1 0 1 X X 0 0 X

0 1 1 0 1 0 0 X X 0 X 1

1 0 0 0 0 0 X 1 0 X 0 X

1 0 1 1 0 0 X 0 0 X X 1

1 1 0 1 1 1 X 0 X 0 1 X

1 1 1 1 0 1 X 0 X 1 X 0

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

iii) (0,5) Simplifique a lógica combinacional das funções de ativação.

A simplificação da lógica combinacional exige a determinação das funções lógicas referentes aos

sinais J2 , K2 , J1 , K1 , J0 e K0 . Utilizando mapas de Karnaugh-Vuit, as funções resultantes são

E1 [n] E0 [n] E1 [n] E0 [n]

00 01 11 10 00 01 11 10

E2 [n] E2 [n]

0 0 0 0 1 0 X X 0 0

1 X X X X 1 X X 1 0

J2 = E1 [n] · E0 [n] K1 = E0 [n] · E2 [n]

E1 [n] E0 [n] E1 [n] E0 [n]

00 01 11 10 00 01 11 10

E2 [n] E2 [n]

0 X X X X 0 1 X X 0

1 1 0 0 0 1 0 X X 1

K2 = E1 [n] · E0 [n] J0 = E1 [n] · E2 [n] + E1 [n] · E2 [n]

= E1 [n] ⊕ E2 [n]

E1 [n] E0 [n] = E1 [n] ⊕ E2 [n]

00 01 11 10

E2 [n]

0 0 1 X X

E1 [n] E0 [n]

00 01 11 10

1 0 0 X X E2 [n]

0 X 0 1 X

1 X 1 0 X

J1 = E0 [n] · E2 [n]

K0 = E1 [n] · E2 [n] + E1 [n] · E2 [n]

= E1 [n] ⊕ E2 [n]

O circuito requer 3 flip-flops tipo JK, 4 portas AND de duas entradas e 2 portas XOR de duas

entradas. O funcionamento do circuito pode ser verificado no arquivo prova201702q1.hds em

anexo.

2) Considere a sequência de números inteiros 7, 5, 5, 3, 0, 4, 4, 0, 6, 2, 1. Projete um circuito

digital utilizando flip-flops tipo JK que reproduza essa sequência periodicamente. A tabela de

ativação do flip-flop JK está indicada na Tabela 3.

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

i) (0,5) Defina e codifique os estados do circuito. Desenhe o diagrama de transição de estados;

O gerador de sequência tem módulo 11 portanto são necessários ⌈log2 11⌉ = 4 flip-flops. Os

algarismos da contagem variam entre 0 e 7. Observando que as repetições de algarismos da

sequência ocorrem no máximo uma vez, não é necessário um transcodificador. Utilizando um bit

adicional na posição mais significativa, uma das possíveis codificações de estado possíveis é

em que a saída do contador é produzida utilizando os 3 bits menos significativos.

ii) (1,0) Construa a tabela de ativação do circuito;

Baseado no diagrama de transição de estados determinado anteriormente e na tabela de ativação

do flip-flop tipo JK, a tabela de ativação resultante é

Estado Atual Estado Futuro Ativação

E3 [n] E2 [n] E1 [n] E0 [n] E3 [n + 1] E2 [n + 1] E1 [n + 1] E0 [n + 1] J3 K3 J2 K2 J1 K1 J0 K0

0 0 0 0 0 1 0 0 0 X 1 X 0 X 0 X

0 0 0 1 0 1 1 1 0 X 1 X 1 X 1 X

0 0 1 0 0 0 0 1 0 X 0 X X 1 X 0

0 0 1 1 0 0 0 0 0 X 0 X X 1 X 1

0 1 0 0 1 1 0 0 1 X X 0 0 X 0 X

0 1 0 1 1 1 0 1 1 X X 0 0 X X 0

0 1 1 0 0 0 1 0 0 X X 1 X 0 0 X

0 1 1 1 0 1 0 1 0 X X 0 X 1 X 0

1 0 0 0 0 1 1 0 X 1 1 X 1 X 0 X

1 0 0 1 X X X X X X X X X X X X

1 0 1 0 X X X X X X X X X X X X

1 0 1 1 X X X X X X X X X X X X

1 1 0 0 1 0 0 0 X 0 X 1 0 X 0 X

1 1 0 1 0 0 1 1 X 1 X 1 1 X X 0

1 1 1 0 X X X X X X X X X X X X

1 1 1 1 X X X X X X X X X X X X

iii) (0,5) Determine a lógica combinacional das entradas de controle dos flip-flops.

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

A simplificação da lógica combinacional exige a determinação das funções lógicas referentes aos

sinais J3 , K3 , J2 , K2 , J1 , K1 , J0 e K0 . Utilizando mapas de Karnaugh-Vuit, as funções resultantes

são

E1 [n] E0 [n] E1 [n] E0 [n]

00 01 11 10 00 01 11 10

E3 [n] E2 [n] E3 [n] E2 [n]

00 0 0 0 0 00 X X X X

01 1 1 0 0 01 0 0 0 1

11 X X X X 11 1 1 X X

10 X X X X 10 X X X X

J3 = ·E2 [n] · E1 [n] K2 = E1 [n] · E0 [n] + E3 [n]

E1 [n] E0 [n] E1 [n] E0 [n]

00 01 11 10 00 01 11 10

E3 [n] E2 [n] E3 [n] E2 [n]

00 X X X X 00 0 1 X X

01 X X X X 01 0 0 X X

11 0 1 X X 11 0 1 X X

10 1 X X X 10 1 X X X

K3 = E0 [n] + E2 [n] J1 = E3 [n] · E2 [n] + E2 [n] · E0 [n]

+ E3 [n] · E0 [n]

E1 [n] E0 [n]

00 01 11 10

E3 [n] E2 [n] E1 [n] E0 [n]

00 1 1 0 0 00 01 11 10

E3 [n] E2 [n]

01 X X X X 00 X X 1 1

11 X X X X 01 X X 1 0

10 1 X X X 11 X X X X

10 X X X X

J2 = E1 [n]

K1 = E0 [n] + E2 [n]

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

E1 [n] E0 [n] E1 [n] E0 [n]

00 01 11 10 00 01 11 10

E3 [n] E2 [n] E3 [n] E2 [n]

00 0 X X 1 00 X 0 1 X

01 0 X X 0 01 X 0 0 X

11 0 X X X 11 X 0 X X

10 0 X X X 10 X X X X

J0 = E2 [n] · E1 [n] K0 = E2 [n] · E1 [n]

O circuito requer 4 flip-flops tipo JK, 7 portas AND de duas entradas, 3 portas OR de duas

entradas e 1 porta OR de três entradas. O funcionamento do circuito pode ser verificado no

arquivo prova201702q3.hds em anexo.

Epílogo: Verificação do comportamento nos estados não utilizados

Verificando a Tabela de Transição de estados após a determinação da lógica combinacional, a

tabela resultante (omitindo os estados com estado futuro determinados) é

Estado Atual Estado Futuro Ativação

E3 [n] E2 [n] E1 [n] E0 [n] E3 [n + 1] E2 [n + 1] E1 [n + 1] E0 [n + 1] J3 K3 J2 K2 J1 K1 J0 K0

1 0 0 1 0 1 1 1 0 1 1 1 1 1 0 0

1 0 1 0 0 0 0 1 0 1 0 1 1 1 1 1

1 0 1 1 0 0 0 0 0 1 0 1 1 1 1 1

1 1 1 0 1 0 1 0 0 0 0 1 0 0 0 0

1 1 1 1 0 0 0 1 0 1 0 1 1 1 0 0

Os estados futuros de 1001, 1010, 1011 e 1111 são estados válidos utilizados pelo gerador de

sequência. O estado futuro do estado 1110 é o estado 1010 cujo estado futuro é um estado

válido. Portanto, o circuito é capaz de retornar a um estado válido mesmo que ele tenha sido

inicializado em um estado inválido.

3) Considere a tabela de estados descrita na Tabela 1.

Estado atual Estado Futuro (i = 0) Estado Futuro (i = 1) Saída (o)

a e d 0

b c g 1

c d e 1

d a c 0

e c a 1

f h g 1

g f d 0

dh h b 1

Tabela 1: Tabela de estados da Questão 3

i) (1,0) Utilize uma tabela de implicação ou o método das partições para identificar estados

equivalentes;

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

Iniciando a tabela de implicação a partir da tabela de estados

b X

c X c=d; g=c

d a=e; c=d X X

e X a=g c=d; a=e X

f X c=h d=h; d=e X c=h; a=g

g e=f; d=g X X a=f; c=d X X

h X c=h; b=g d=h; e=b X c=h; a=b b=h; b=g X

a b c d e f g

Após a primeira iteração (9 eliminações)

b X

c X X

d X X X

e X a=g X X

f X c=h X X c=h; a=g

g e=f; d=g X X X X X

h X X X X X X X

a b c d e f g

Após a segunda iteração (3 eliminações)

b X

c X X

d X X X

e X a=g X X

f X X X X X

g X X X X X X

h X X X X X X X

a b c d e f g

Após a terceira iteração (1 eliminação)

b X

c X X

d X X X

e X X X X

f X X X X X

g X X X X X X

h X X X X X X X

a b c d e f g

O processo é interrompido por não haver mais possibilidade de encontrar estados iguais ou

equivalentes.

ii) (0,5) Construa a tabela de estados;

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

Como não foram encontrados estados iguais ou equivalentes, a tabela de estados do circuito é

Estado atual Estado Futuro (i = 0) Estado Futuro (i = 1) Saída (o)

a e d 0

b c g 1

c d e 1

d a c 0

e c a 1

f h g 1

g f d 0

h h b 1

iii) (1,0) Construa a tabela de ativação do circuito. Considere que o circuito utiliza flip-flops

tipo D;

Escolhendo (arbitrariamente) a seguinte codificação de estados

Codificação

Estado

E2 [n] E1 [n] E0 [n]

a 0 0 0

b 0 0 1

c 0 1 0

d 0 1 1

e 1 0 0

f 1 0 1

g 1 1 0

h 1 1 1

a tabela de ativação é

Estado Atual Entrada Estado Futuro Ativação Saída

E2 [n] E1 [n] E0 [n] i E2 [n + 1] E1 [n + 1] E0 [n + 1] D2 D1 D0 o

0 0 0 0 1 0 0 1 0 0 0

0 0 0 1 0 1 1 0 1 1 0

0 0 1 0 0 1 0 0 1 0 1

0 0 1 1 1 1 0 1 1 0 1

0 1 0 0 0 1 1 0 1 1 1

0 1 0 1 1 0 0 1 0 0 1

0 1 1 0 0 0 0 0 0 0 0

0 1 1 1 0 1 0 0 1 0 0

1 0 0 0 0 1 0 0 1 0 1

1 0 0 1 0 0 0 0 0 0 1

1 0 1 0 1 1 1 1 1 1 1

1 0 1 1 1 1 0 1 1 0 1

1 1 0 0 1 0 1 1 0 1 0

1 1 0 1 0 1 1 0 1 1 0

1 1 1 0 1 1 1 1 1 1 1

1 1 1 1 0 0 1 0 0 1 1

iv) (0,5) Determine a lógica combinacional das entradas de controle dos flip-flops.

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

E0 [n] i E0 [n] i

00 01 11 10 00 01 11 10

E2 [n] E1 [n] E2 [n] E1 [n]

00 1 0 1 0 00 0 1 0 0

01 0 1 0 0 01 1 0 0 0

11 1 0 0 1 11 1 1 1 1

10 0 0 1 1 10 0 0 0 1

D2 = E2 [n] · E1 [n] · E0 [n] · i D0 = E1 [n] · E0 [n] · i

+ E2 [n] · E1 [n] · E0 [n] · i + E2 [n] · E1 [n]

+ E1 [n] · E0 · i + E2 [n] · E1 [n] · E0 [n] · i

+ E2 [n] · E1 [n] · i + E2 [n] · E1 [n] · E0 [n] · i

E0 [n] i E0 [n] i

00 01 11 10 00 01 11 10

E2 [n] E1 [n] E2 [n] E1 [n]

00 0 1 1 1 00 0 0 1 1

01 1 0 1 0 01 1 1 0 0

11 0 1 0 1 11 0 0 1 1

10 1 0 1 1 10 1 1 1 1

D1 = E2 [n] · E1 [n] K0 = E2 [n] · E1 [n]

+ E2 [n] · E1 [n] · i + E2 [n] · E1 [n]

+ E2 [n] · E0 [n] · i + E2 [n] · E0 [n]

+ E2 [n] · E1 [n] · E0 [n] · i + E2 [n] · E1 [n] · E0 [n]

+ E2 [n] · E1 [n] · E0 [n] · i

+ E2 [n] · E0 [n] · i

+ E2 [n] · E1 [n] · i

4) Projete uma máquina de estados finita de Mealy que detecte a sequência binária “1110”

utilizando flip-flops tipo D na memória de estado. Quando a sequência correta é detectada a

máquina de estados deve produzir um nível lógico baixo em sua saída. Do contrário, a máquina

deve produzir um nível alto em sua saída. Devido a restrições orçamentárias, você pode utilizar

no máximo dois flip-flops no projeto.

i) (1,0) Desenhe o diagrama de transição de estados;

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

ii) (0,5) Utilize uma tabela de implicação ou o método das partições para identificar estados

equivalentes;

Gerando a tabela de estados a partir do diagrama de transição de estados

Estado atual Estado Futuro (i = 0) Estado Futuro (i = 1) Saída (i = 0) Saída (i = 1)

0 acertos 0 acertos 1 acerto 1 1

1 acertos 0 acertos 2 acertos 1 1

2 acertos 0 acertos 3 acertos 1 1

3 acertos 4 acertos 3 acertos 0 1

4 acertos 0 acertos 1 acerto 1 1

De onde conclui-se que os estados “0 acertos” e “4 acertos” são iguais. Eliminando o estado “4

acertos”, a tabela resultante é

Estado atual Estado Futuro (i = 0) Estado Futuro (i = 1) Saída (i = 0) Saída (i = 1)

0 acertos 0 acertos 1 acerto 1 1

1 acertos 0 acertos 2 acertos 1 1

2 acertos 0 acertos 3 acertos 1 1

3 acertos 0 acertos 3 acertos 0 1

Iniciando a tabela de implicação

1 acerto 1 acerto = 2 acertos

2 acertos 1 acerto = 3 acertos 2 acertos = 3 acertos

3 acertos X X X

0 acertos 1 acerto 2 acertos

Após a primeira iteração (2 eliminações)

1 acerto 1 acerto = 2 acertos

2 acertos X X

3 acertos X X X

0 acertos 1 acerto 2 acertos

Após a segunda iteração (1 eliminação)

1 acerto X

2 acertos X X

3 acertos X X X

0 acertos 1 acerto 2 acertos

O processo é interrompido pois não é possível realizar mais eliminações.

iii) (1,0) Construa a tabela de ativação do circuito;

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

Utilizando a codificação

Codificação

Estado

E1 [n] E0 [n]

0 Acertos 0 0

1 Acerto 0 1

2 Acertos 1 0

3 Acertos 1 1

a tabela de ativação resultante é

Estado Atual Entrada Estado Futuro Ativação Saída

E1 [n] E0 [n] i E1 [n + 1] E0 [n + 1] D1 D0 o

0 0 0 0 0 0 0 1

0 0 1 0 1 0 1 1

0 1 0 0 0 0 0 1

0 1 1 1 0 1 0 1

1 0 0 0 0 0 0 1

1 0 1 1 1 1 1 1

1 1 0 0 0 0 0 0

1 1 1 1 1 1 1 1

iv) (0,5) Determine os circuitos combinacionais que geram os sinais de controle dos flip flops e

o sinal de saída.

E0 [n] i E0 [n] i

00 01 11 10 00 01 11 10

E1 [n] E1 [n]

0 0 0 1 0 0 0 1 0 0

1 0 1 1 0 1 0 1 1 0

D1 = E0 [n] · i + E1 [n] · i D0 = E0 [n] · i + E1 [n] · i

E0 [n] i

00 01 11 10

E1 [n]

0 1 1 1 1

1 1 1 1 0

o = E1 [n] + i + E0 [n]

Baixado por Philipp Hass (philipphass2014@gmail.com)

lOMoARcPSD|34579991

Tabela 2: Tabela de ativação do flip-flop tipo JK

Qk Qk+1 J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Tabela 3: Tabela de ativação do flip-flop tipo D

Qk Qk+1 D

0 0 0

0 1 1

1 0 0

1 1 1

Baixado por Philipp Hass (philipphass2014@gmail.com)

Você também pode gostar

- Sistemas Digitais - Trabalho I (Resolução)Documento3 páginasSistemas Digitais - Trabalho I (Resolução)lazaro MouraAinda não há avaliações

- LCL Codificador, DecodificadorDocumento7 páginasLCL Codificador, DecodificadoriorrannaAinda não há avaliações

- Examen 28 11 2011 SOLUCIONDocumento9 páginasExamen 28 11 2011 SOLUCIONAdri SsAinda não há avaliações

- Relatorio 2Documento9 páginasRelatorio 2Miguel RebochoAinda não há avaliações

- Circuitos CombinatóriosDocumento30 páginasCircuitos CombinatóriosAdilson NevesAinda não há avaliações

- Actividade 11Documento5 páginasActividade 11Klöry BrásAinda não há avaliações

- Atividade 02 - Digital (2) - CopiarDocumento5 páginasAtividade 02 - Digital (2) - CopiarleandrodasilveiraoliveiraAinda não há avaliações

- uDX210 ManualreléDocumento3 páginasuDX210 Manualreléroth_scribAinda não há avaliações

- uDX210 manualSSRDocumento3 páginasuDX210 manualSSRroth_scribAinda não há avaliações

- PROVA Sistemas DigitaisDocumento12 páginasPROVA Sistemas DigitaisJulia FlorencioAinda não há avaliações

- EELi03 - Experimento 03 - Júlio César Ribeiro SilvaDocumento3 páginasEELi03 - Experimento 03 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- Circuitos CombinatóriosDocumento16 páginasCircuitos CombinatóriosPaulo RodriguesAinda não há avaliações

- Lista de Exercícios (1) (2) - Respostas-2022Documento8 páginasLista de Exercícios (1) (2) - Respostas-2022Diego Felipe Moreno MoreiraAinda não há avaliações

- G Atividade 02 - DigitalDocumento6 páginasG Atividade 02 - DigitalrgomesgianiniAinda não há avaliações

- Avaliação Final DigitalDocumento5 páginasAvaliação Final DigitalGeorge MaxwellAinda não há avaliações

- Atividade 08.1 Obrigatória 02Documento3 páginasAtividade 08.1 Obrigatória 02felipe.matAinda não há avaliações

- Atividade de Pesquisa 02 - Eletrônica DigitalDocumento12 páginasAtividade de Pesquisa 02 - Eletrônica Digitalmauro floresAinda não há avaliações

- ANOVA Caso No BalanceadoDocumento9 páginasANOVA Caso No Balanceadocamilo pardoAinda não há avaliações

- LCL Relatorio 1Documento6 páginasLCL Relatorio 1luca50% (2)

- Aula 05042010 1oa Cco IocDocumento37 páginasAula 05042010 1oa Cco IocProf. Rubens EvangelistaAinda não há avaliações

- Exerc1 PDFDocumento3 páginasExerc1 PDFAlisson OliveiraAinda não há avaliações

- Atividade de Pesquisa 01Documento6 páginasAtividade de Pesquisa 01Juliano MartinsAinda não há avaliações

- LedDocumento3 páginasLedThiago HenriqueAinda não há avaliações

- Atividade4 EXC LABDocumento4 páginasAtividade4 EXC LABGuilherme Ramos da SilvaAinda não há avaliações

- Aula IIDocumento11 páginasAula IIAntonio LinsAinda não há avaliações

- EELi03 - Experimento 02 - Júlio César Ribeiro SilvaDocumento10 páginasEELi03 - Experimento 02 - Júlio César Ribeiro SilvaJúlioAinda não há avaliações

- Relatorio Trab1Documento6 páginasRelatorio Trab1lucas de macedoAinda não há avaliações

- Cópia de LISTA 2Documento12 páginasCópia de LISTA 2wagnermafraAinda não há avaliações

- Atividade Prática - Eletrônica Digital RU1567558Documento10 páginasAtividade Prática - Eletrônica Digital RU1567558Heuler LageAinda não há avaliações

- Exercicios de Circuitos Digitais - Lista 3Documento7 páginasExercicios de Circuitos Digitais - Lista 3Elisama Rebello VianaAinda não há avaliações

- PráticaCircuito IsabellaDocumento5 páginasPráticaCircuito IsabellaIsabella Correa De SouzaAinda não há avaliações

- Exp 2 - VerilogDocumento5 páginasExp 2 - VerilogGabriel NazarioAinda não há avaliações

- Álgebra Linear - Exercícios ResolvidosDocumento17 páginasÁlgebra Linear - Exercícios ResolvidosFelipe André100% (2)

- Ed Lab-2 2022-Grupo5 LDocumento8 páginasEd Lab-2 2022-Grupo5 Lrute maungueAinda não há avaliações

- LSD 2122i LAB1 RelatórioDocumento6 páginasLSD 2122i LAB1 RelatórioJEREMIAS BORGESAinda não há avaliações

- Solução Avaliação III - 2021-1Documento6 páginasSolução Avaliação III - 2021-1Mikael CassaoAinda não há avaliações

- Atividade de Pesquisa 01Documento7 páginasAtividade de Pesquisa 01celsotkAinda não há avaliações

- Lista de Exercícios 02 - Simplificação de Circuitos LógicosDocumento1 páginaLista de Exercícios 02 - Simplificação de Circuitos Lógicosvieira.george8082100% (1)

- Lista de Exercicios Sistemas DigitaisDocumento2 páginasLista de Exercicios Sistemas DigitaisAlexandre QuintasAinda não há avaliações

- Exercicio 06 - GabaritoDocumento6 páginasExercicio 06 - GabaritoquimiwataAinda não há avaliações

- AT02 Zedekias NobregaDocumento2 páginasAT02 Zedekias NobregaZedekias NobregaAinda não há avaliações

- Atividade 3Documento3 páginasAtividade 3Guilherme Ramos da SilvaAinda não há avaliações

- EL66J Exercicios Lista2Documento7 páginasEL66J Exercicios Lista2VINICIUS HIDEKI INOUEAinda não há avaliações

- Simulado p2 - Sistemas Digitais - GabDocumento7 páginasSimulado p2 - Sistemas Digitais - GabBrendow AlmeidaAinda não há avaliações

- Exercicio 20200610 GabDocumento6 páginasExercicio 20200610 Gabdont4getAinda não há avaliações

- Eletronica DigitalDocumento5 páginasEletronica DigitalJonas Paixão marques de sousaAinda não há avaliações

- Atividade Portas LogicasDocumento5 páginasAtividade Portas LogicasNeto Pops100% (1)

- Contadores Descedente Mod10Documento19 páginasContadores Descedente Mod10Hilton CalderonAinda não há avaliações

- Exp3 LCLDocumento6 páginasExp3 LCLAna Luiza CamposAinda não há avaliações

- Atividade 02 Eletrônica DigitalDocumento6 páginasAtividade 02 Eletrônica DigitalDaniel Canaã93% (14)

- Lista 2 de SIST DIG (2s2022)Documento3 páginasLista 2 de SIST DIG (2s2022)iron hAinda não há avaliações

- Lista 1aDocumento7 páginasLista 1awagnermafraAinda não há avaliações

- Avaliação Final Digital (1) - CopiarDocumento5 páginasAvaliação Final Digital (1) - CopiarleandrodasilveiraoliveiraAinda não há avaliações

- Experimento 01Documento8 páginasExperimento 01Pedro HAinda não há avaliações

- Aula Prática 3Documento14 páginasAula Prática 3Morgana Correa De OliveiraAinda não há avaliações

- Conversões e Operações Matemáticas Com BináriosDocumento45 páginasConversões e Operações Matemáticas Com BináriosPEDRO HENRIQUEAinda não há avaliações

- Atividade 02 - DigitalDocumento4 páginasAtividade 02 - Digitalvictorhsmaximo10Ainda não há avaliações

- Lab 2 # 1 Parte (1) Eletrônica DigitalDocumento8 páginasLab 2 # 1 Parte (1) Eletrônica DigitalgabrielgomesgblAinda não há avaliações

- Prova 11 ED 1 Prova 2 EtapaDocumento3 páginasProva 11 ED 1 Prova 2 Etapahenrique silvaAinda não há avaliações

- Hiragana, Katakana, KanjiDocumento3 páginasHiragana, Katakana, KanjiRuan Flaneto CartierAinda não há avaliações

- Plantar EspinafreDocumento3 páginasPlantar EspinafrecarrapichoAinda não há avaliações

- A Estatística Na EconomiaDocumento3 páginasA Estatística Na EconomiaJefferson MartinsAinda não há avaliações

- PNL MetáforasDocumento105 páginasPNL Metáforascor com poesia100% (1)

- PalestraDocumento17 páginasPalestraWilliam AmaralAinda não há avaliações

- Maykon Dos Santos Marinho - Construindo Um Mapa ConceitualDocumento1 páginaMaykon Dos Santos Marinho - Construindo Um Mapa ConceitualMaykon dos Santos MarinhoAinda não há avaliações

- Exercicios U1Documento6 páginasExercicios U1Elone Izata SampaioAinda não há avaliações

- Cgconvocaocadastroreserva 2011aDocumento87 páginasCgconvocaocadastroreserva 2011aPaulo SergioAinda não há avaliações

- Os Problemas Do EtnocentrismoDocumento6 páginasOs Problemas Do EtnocentrismoMarcelo Soares Cotta100% (1)

- Reis Magos e Simbologia Esoterica Nasc - JesusDocumento6 páginasReis Magos e Simbologia Esoterica Nasc - JesusAurivan de CastroAinda não há avaliações

- VLB 1º Vol (A-H)Documento59 páginasVLB 1º Vol (A-H)Emerson José Silveira da Costa100% (1)

- SssDocumento3 páginasSssWallace AguiarAinda não há avaliações

- Treino para A Vida - Treinador CarterDocumento4 páginasTreino para A Vida - Treinador CarterLuizCarlos100% (3)

- Teste 2 Versão IDocumento9 páginasTeste 2 Versão IJose Eira100% (1)

- Atividade 1 UC8Documento2 páginasAtividade 1 UC8Cleber OliveiraAinda não há avaliações

- Sistema de Apoio A Decisão em Escalada AlpinaDocumento11 páginasSistema de Apoio A Decisão em Escalada AlpinaTiago LisboaAinda não há avaliações

- Trilhas de Estudo Ao Cacd CompletoDocumento10 páginasTrilhas de Estudo Ao Cacd CompletoJoão Paulo Arrais100% (2)

- Manual Antron IIDocumento18 páginasManual Antron IIleonardoAinda não há avaliações

- PluviógrafoDocumento12 páginasPluviógrafoWillian HellerAinda não há avaliações

- Derrida e o Pensamento Contemporâneo - Estudos InterdisciplinaresDocumento314 páginasDerrida e o Pensamento Contemporâneo - Estudos Interdisciplinaresandrethiago_geo100% (2)

- Quem É A Mocinha Que Está Com KrishnaDocumento5 páginasQuem É A Mocinha Que Está Com KrishnaGuruprema DasaAinda não há avaliações

- Se Amigo de Ti Mesmo - Capitulo 7Documento15 páginasSe Amigo de Ti Mesmo - Capitulo 7Lília ReisAinda não há avaliações

- PGR - Programa de Gerenciamento de Riscos PDFDocumento6 páginasPGR - Programa de Gerenciamento de Riscos PDFaaspdcaAinda não há avaliações

- Operating Manual (Avh-P5250dvd - Avh-P5250bt) - PorDocumento112 páginasOperating Manual (Avh-P5250dvd - Avh-P5250bt) - PorRobson meloAinda não há avaliações

- FT Climas FriosDocumento7 páginasFT Climas FriosAna GriloAinda não há avaliações

- NBR 15113 - Resíduos Sólidos Da Construção CivilDocumento16 páginasNBR 15113 - Resíduos Sólidos Da Construção CivilRogerio AraujoAinda não há avaliações

- Aves MatrizesDocumento20 páginasAves MatrizesJacyele Bassiga De LimaAinda não há avaliações

- A Família Das Palavras PDFDocumento13 páginasA Família Das Palavras PDFMilena Carvalhais100% (1)

- O Trader Vencedor - OGF - 04.indd 1Documento14 páginasO Trader Vencedor - OGF - 04.indd 1Alexandro KozielAinda não há avaliações

- Avaliação Parcial - Linguagens - 1º Bimestre - 2Documento4 páginasAvaliação Parcial - Linguagens - 1º Bimestre - 2DANIEL JEFFERSONAinda não há avaliações