Escolar Documentos

Profissional Documentos

Cultura Documentos

Flip Flop

Enviado por

Guilherme Barbosa MendesTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Flip Flop

Enviado por

Guilherme Barbosa MendesDireitos autorais:

Formatos disponíveis

Flip- flop RS O flip-flop bsico o modelo RS.

. constitudo por 2 portas NAND com suas sadas sendo usadas como uma das variveis de entradas de modo cruzado.

Tabela verdade do Flip-flop RS bsico: S 0 0 0 0 1 1 1 1 R 0 0 1 1 0 0 1 1 Q ATUAL 0 1 0 1 0 1 0 1 Q FUTURO 0 1 0 0 1 1 1 1 Q BARRADO 1 0 1 1 0 0 1 1

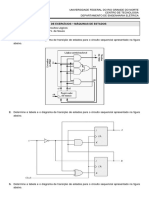

Flip- Flop RS com Clock

Partindo da mesma lgica do tipo de Flip-Flop RS Bsico, a nica alterao em sua composio a entrada de um clock, que a pea fundamental para o circuito, pois quando ativo ele altera a sada de acordo com as variveis de entrada. Porm, aqui temos a entrada do clock, que quando possui nvel lgico 1 permite o funcionamento do RS Bsico em si e quando ele apresenta nvel lgico 0 ele apresenta na sada o ltimo estado das entradas

Tabela Verdade do Flip-flop RS com Clock: S 0 0 1 1 R 0 1 0 1 QF QA 0 1 X

Flip-Flop JK O funcionamento do JK nada mais que um Flip-Flop RS realimentado, conforme ilustrao abaixo:

Tabela verdade do Flip-Flop JK: J 0 0 1 1 K 0 1 0 1 QF QA 0 1 QA

Flip- Flop JK com entradas Preset e Clear Aqui temos a entrada de duas novas variveis, o Preset e Clear, que determinam o funcionamento do Flip-Flop. Onde o Preset seleciona o nvel lgico 1 na sada, independente do que est nas entradas, assim como o Clear seleciona o nvel lgico 0 na sada independente do que est nas entradas. Abaixo segue a tabela de como funciona o esquema Preset e Clear.

Tabela verdade do Flip-Flop JK com Prest e Clear CLR 0 0 1 1 PR 0 1 0 1 QF No Permitido 0 1 Funcionamento normal

Flip-flop JK Mestre Escravo O flip-flop apresenta um comportamento indesejvel, quando o clock for igual a 1. Nesta situao, se houver uma mudana nas entrada J e K, o circuito apresentar uma nova sada. Para corrigir este problema, foi criado o flip-flop JK Mestre-Escravo. Anlise: Clock em 1, entradas J e K afetam a sada Q1; Clock do RS em 0, bloqueando a sada Q; Clock em 0, sada Q1 bloqueada; Entradas RS, desbloqueadas afetando a sada Q; Valores de JK no afetam a sada Q1; Valores em RS no mudam;

Mudanas de clock Clock em 0, mestre bloqueado: Entadas J e K variam mas a sada Q1 permanece a mesma, logo Q tambm mantem seu valor. Intervalo de t0 a t1 e t2 a t3. Clock de 0 para 1, J e K afetam Q1; t1, o valor que estava em Q vai para Q1 invertido; t3, J = 0 e K = 0, Q e Q1 continua no mesmo estado, Qf = Qa; Clock em 1, mestre desbloqueado: Q1 muda o seu estado de acordo com as entradas J, K e Q; t1 a t2, os valores assumidos por J, K e Q mantem o valor de Q1 em 1; t3 e t4, Q1 vai para 0, quando J = 0 e K = 1; Q1 via para 1, quando J = 1 e K = 0; Q1 vai para 0, novamente quando J = 0 e K = 1; Q permanece constante, pois o clock do circuito escravo estar em 0; Clock passa de 1 para 0, Q1 (R e S) afetam Q: O valor de Q1 se altera apenas uma vez exatamente na transio 1 para 0, incio do intervalo onde o valor do clock est em 0; O valor presente na entrada do mestre gera uma entrada para o circuito escravo em (t2 e t4); t2, J = 1 e K = 0, Q vai para 1; t4, J = 1, K = 1 e Qa = 1, Q vai para 0, invertendo seu valor;

Tabela Verdade Flip-flop JK Mestre Escravo J 0 0 1 1 K 0 1 0 1 Qf Qa 0 1 Qa

Flip-Flop Tipo T

Esse um flip-flop JK com a particularidade de possuir as entradas J e K curto circuitadas. quando houver variao do clock, o valor guardado no flip-flop ser alternado ou mantido dependendo se o valor na entrada T (Toggle) for 1 ou 0.

Tabela Verdade do Flip-flop tipo T T 0 1 0 1 Q 0 1 1 0 Q 0 0 1 1

Flip-flop tipo D (DATA) O flip-flop D ("data" ou dado, pois armazena o bit de entrada) possui uma entrada, que ligada diretamente sada quando o clock mudado. Independentemente do valor atual da sada, ele ir assumir o valor 1 se D = 1 quando o clock for mudado ou o valor 0 se D = 0 quando o clock for mudado. Este flip-flop pode ser interpretado como uma linha de atraso primitiva ou um hold de ordem zero, visto que a informao colocada na sada um ciclo depois de ela ter chegado na entrada.

Tabela Verdade do Flip-flop tipo D D 0 0 1 1 Q 0 1 0 1 Q 0 0 1 1

Registrador de deslocamento

registrador de deslocamento um conjunto de registradores configurados em um arranjo linear de tal forma que a informao deslocada pelo circuito conforme o mesmo ativado. Os registradores de deslocamento podem possuir uma combinao de entradas e sadas seriais e paralelas, incluindo as configuraes entrada serial, sada paralela (SIPO) e entrada paralela, sada serial (PISO). Existem outra configuraes possuindo ambas as entradas serial e paralela e outra com sadas serial paralela. Existem tambm registradores de deslocamento bi-direcionais, os quais permitem que se varie a

direo do deslocamento da informao. As entradas e sadas seriais de um registrador podem ser conectadas juntas, de modo a formar um registrador de deslocamento circular. Poderiam tambm ser desenvolvidos registradores de deslocamento multidimensionais, os quais podem realizar processamentos mais complexos. Entrada serial, sada serial Leitura destrutiva Este o tipo mais simples de registrador de deslocamento. O conjunto de dados inserido em 'Data In', e deslocado para a direita em um estgio cada vez que o 'Data Advance' colocado em nvel alto. A cada avano, o bit da extrema esquerda, o 'Data In', deslocado para a sada do primeiro flip-flop. O bit na extrema direita, o 'Data Out', deslocado e ento perdido. Os dados so armazenados em cada flip-flop, na sada 'Q', de modo que existem quatro "espaos" para armazenamento disponveis nestas configurao, sendo desta forma um registrador de deslocamento de 4 bits. Para exemplificar o padro do deslocamento, consideremos que o registrador possua o dado 0000, de modo que todos os espaos para deslocamento estejam vazios. Conforme o 'Data In' insere os dados 1,1,0,1,0,0,0,0 (nesta ordem, fornecendo um pulso ao 'Data Advance' a cada dado, sendo isto chamado de cloking ou strobing) no registrador, obtemos o resultado mostrado na tabela ao lado. A coluna da esquerda corresponde ao pino de sada localizado na extrema esquerda da figura, e assim por diante. Leitura no-destrutiva A leitura no-destrutiva pode ser obtida utilizando-se a configurao mostrada abaixo. Outro pino de entrada adicionado, o controle de Leitura/Escrita. Quando este est em nvel alto (write) ento o registrador de deslocamento se comporta normalmente, avanando a entrada de dados em uma posio para cada ciclo de clock, e os dados podem ser perdidos no fim do resgistrador. Entretanto, quando o controle R/W colocado em nvel baixo (read), qualquer dado deslocado na extrema direita se torna a prxima entrada na esquerda, sendo assim mantido no sistema. Deste modo, enquanto o controle R/W estiver em nvel baixo, nenhum dado pode ser perdido do sistema.

Entrada serial, Sada paralela Esta configurao permite a converso do formato serial para o paralelo. Os dados entram de forma serial, conforme descrito na sesso acima. Uma vez que os dados entraram, eles podem ser lidos todos simultaneamente, ou deslocados para fora e substitudos. Pulsos na entrada 0 1 2 3 4 5 6 7 8 Q0 0 1 1 1 1 1 1 1 1 Q1 0 0 1 1 1 1 1 1 1 Q2 0 0 0 1 1 1 1 1 1 Q3 0 0 0 0 1 1 1 1 1 Q4 0 0 0 0 0 1 1 1 1

Entrada paralela, Sada serial Esta configurao recebe os dados atravs das entradas D1 a D4 no formato paralelo. Para escrever os dados no registrador, o controle de Escrita/Deslocamento deve estar em nvel baixo. Para deslocar os dados, o controle deve ser colocado em nvel alto e os registradores devem receber um pulso de clock, desta forma o circuito atua como um registrador de deslocamento SISO, com o terminal D1 atuando como entrada de dados. Entretanto, caso uma palavra de dados tenham sido escritos de forma paralela e em seguida deslocados, a sada de dados, Q, conter os bits desta palavra, lidos em ordem.

Conversor paralelo-serie

Introduo

Em eletrnica e circuitos digitais, o flip-flop ou multivibrador biestvel um circuito digital pulsado capaz de servir como uma memriade um bit. Um flip-flop tipicamente inclui zero, um ou dois sinais de entrada, um sinal de clock, e um sinal de sada, apesar de muitos flip-flops comerciais proverem adicionalmente o complemento do sinal de sada. Alguns flip-flops tambm incluem um sinal da entradaclear, que limpa a sada atual. Como os flip-flops so implementados na forma de circuitos integrados, eles tambm necessitam de conexes de alimentao. A pulsao ou mudana no sinal do clock faz com que o flip-flop mude ou retenha seu sinal de sada, baseado nos valores dos sinais de entrada e na equao carecterstica do flip-flop.

Concluso O flip-flop pode ser utilizado para armazenar um bit, ou um digito binrio de informao. A informao armazenada em um conjunto de flip-flops pode representar o estado de um seqenciador, o valor de um contador, um caractere ASCII em uma memria de um computador ou qualquer outra parte de uma informao.

Você também pode gostar

- Tipos de Flip FlopsDocumento12 páginasTipos de Flip FlopsAmerco TivaneAinda não há avaliações

- Flip FLOPDocumento8 páginasFlip FLOPRoseli DefassioAinda não há avaliações

- Flip-Flops, +registradores e ContadoresDocumento32 páginasFlip-Flops, +registradores e ContadoresRoberto MarçalAinda não há avaliações

- Flip - Flop1Documento43 páginasFlip - Flop1Cesar LoureiroAinda não há avaliações

- Aula 7 - Flip-Flop, Registradores e ContadoresDocumento72 páginasAula 7 - Flip-Flop, Registradores e Contadoreswagns10100% (1)

- Aula 2 FundamentosDocumento77 páginasAula 2 FundamentosLéo HilárioAinda não há avaliações

- Cap 10Documento45 páginasCap 10Bruno MigueresAinda não há avaliações

- Sistemas Sequecias Com Biestaveis - Atual1Documento14 páginasSistemas Sequecias Com Biestaveis - Atual1José Salumu FundiAinda não há avaliações

- Flip FlopDocumento13 páginasFlip FlopThaynson AlfredoAinda não há avaliações

- Sistema DigitalDocumento20 páginasSistema DigitalEmanuella Carvalho AlmeidaAinda não há avaliações

- Circuito Sequencial Trabalho de SDAQ... Milania Maria 1836Documento29 páginasCircuito Sequencial Trabalho de SDAQ... Milania Maria 1836Gabriel BeiresAinda não há avaliações

- Relatório 2 - Registrador de DeslocamentoDocumento16 páginasRelatório 2 - Registrador de DeslocamentoFelix GabrielAinda não há avaliações

- Circuitos SequenciaisDocumento36 páginasCircuitos SequenciaisEduardo PereiraAinda não há avaliações

- Teoria Sobre Flip FlopDocumento20 páginasTeoria Sobre Flip FlopursoooAinda não há avaliações

- RESUMO CIENTÍFICO (Versão Beta)Documento8 páginasRESUMO CIENTÍFICO (Versão Beta)João CarlosAinda não há avaliações

- Seminariodigital VFDocumento9 páginasSeminariodigital VFguilherme.laurindo.pintoAinda não há avaliações

- Circuitos Logicos Sequenciais 1Documento48 páginasCircuitos Logicos Sequenciais 1Luiz EduardoAinda não há avaliações

- APS Cronômetro DigitalDocumento19 páginasAPS Cronômetro DigitalLeonardo Corrêa PereiraAinda não há avaliações

- Flip-Flop (BIBLIOGRAFIA - APOSTILA DE ANÁLISE DE CIRCUITOS DIGITAIS DO CEFET-PR)Documento13 páginasFlip-Flop (BIBLIOGRAFIA - APOSTILA DE ANÁLISE DE CIRCUITOS DIGITAIS DO CEFET-PR)Roberto GadelhaAinda não há avaliações

- Apostila Eletronica Digital Aula 3Documento29 páginasApostila Eletronica Digital Aula 3FabricioBrantAinda não há avaliações

- Contador de Pulsos/ Divisor de ClockDocumento3 páginasContador de Pulsos/ Divisor de ClockJoão Antônio MonfortAinda não há avaliações

- Flip Flop RelatorioDocumento23 páginasFlip Flop RelatorioLiana RitterAinda não há avaliações

- Circuitos Sequenciais e FFDocumento71 páginasCircuitos Sequenciais e FFricardoAinda não há avaliações

- SAD Aula16 Logica SequencialDocumento36 páginasSAD Aula16 Logica SequencialJPRodriguesAinda não há avaliações

- Unidade 1 - Operação de ContadoresDocumento77 páginasUnidade 1 - Operação de ContadoresVitória SáAinda não há avaliações

- Introdução Ao Flip-FlopDocumento5 páginasIntrodução Ao Flip-Flopanaraissa908Ainda não há avaliações

- Circuitod SequenciaisDocumento52 páginasCircuitod SequenciaisCarol Camilo100% (1)

- Circuito SequencialDocumento6 páginasCircuito SequencialitrcssAinda não há avaliações

- Digital 2Documento19 páginasDigital 2wellingtonADAinda não há avaliações

- Relatório 6 - CircuitosDocumento15 páginasRelatório 6 - CircuitosKarla BeatrizAinda não há avaliações

- 8 Flip-Flops e Dispositivos CorrelatosDocumento38 páginas8 Flip-Flops e Dispositivos CorrelatosDiego ArimateiaAinda não há avaliações

- Lição 11 - Como Funcionam Os Registradores de Deslocamento (Shift-Registers)Documento10 páginasLição 11 - Como Funcionam Os Registradores de Deslocamento (Shift-Registers)JoseJunembergAinda não há avaliações

- Aula 09 Eletrônica DigitalDocumento38 páginasAula 09 Eletrônica DigitalAna Paula CardosoAinda não há avaliações

- Aula 5 - Circuitos SequenciaisDocumento11 páginasAula 5 - Circuitos SequenciaisGabriel GuilhermeAinda não há avaliações

- Aula 5 - Flip-FlopsDocumento24 páginasAula 5 - Flip-FlopsClaybiane CunhaAinda não há avaliações

- Flip-Flop Eletrônica DigitalDocumento18 páginasFlip-Flop Eletrônica DigitalalexandrefuruchoAinda não há avaliações

- Flip-Flop SR e JKDocumento6 páginasFlip-Flop SR e JKMateusAinda não há avaliações

- Aula 13Documento34 páginasAula 13Igor OliveiraAinda não há avaliações

- Circuitos Sequenciais Antonio Monteiro SDAQ Nº2078Documento11 páginasCircuitos Sequenciais Antonio Monteiro SDAQ Nº2078Gabriel BeiresAinda não há avaliações

- Capitulo 6 Circuitos SequenciaisDocumento83 páginasCapitulo 6 Circuitos SequenciaisnastaciabrAinda não há avaliações

- Eletrônica Digital II - FlipFlopDocumento35 páginasEletrônica Digital II - FlipFlopwandenAinda não há avaliações

- O JK Flip FlopDocumento4 páginasO JK Flip FlopTomás Gonga CalungaAinda não há avaliações

- Relatorio Flip-Flop JKDocumento6 páginasRelatorio Flip-Flop JKabreudededuAinda não há avaliações

- Flip Flop JKDocumento12 páginasFlip Flop JKJeova Jesus de SantanaAinda não há avaliações

- 6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024Documento11 páginas6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024matheus koniczAinda não há avaliações

- Slide 1. Osciladores e TemporizadoresDocumento26 páginasSlide 1. Osciladores e TemporizadoresInaldo FélixAinda não há avaliações

- (Sistemas Digitais 2022 2) Revisão Latches e Flip-FlopsDocumento7 páginas(Sistemas Digitais 2022 2) Revisão Latches e Flip-FlopsRafael PessanhaAinda não há avaliações

- LSD Acetatos 6 v2 PDFDocumento69 páginasLSD Acetatos 6 v2 PDFabednegoAinda não há avaliações

- Aula Teorica#7 ED 2023 FFDocumento32 páginasAula Teorica#7 ED 2023 FFWilsonAinda não há avaliações

- 11 Curso Básico de Eletrônica Digital Parte 11Documento6 páginas11 Curso Básico de Eletrônica Digital Parte 11SilvaSilvaAinda não há avaliações

- Trabalho Flip FlopDocumento9 páginasTrabalho Flip FlopYoung DreyfusAinda não há avaliações

- Registradores de DeslocamentoDocumento51 páginasRegistradores de Deslocamentopriscilla.rocha716Ainda não há avaliações

- Trabalho de Memórias Flip-Flop - CorrigidoDocumento14 páginasTrabalho de Memórias Flip-Flop - CorrigidoPaulo SilvaAinda não há avaliações

- ED2 - Contadores AssincronosDocumento8 páginasED2 - Contadores AssincronosNathan CamiloAinda não há avaliações

- Apostila Latches e FlipDocumento20 páginasApostila Latches e FlipLeonardo GomesAinda não há avaliações

- 2 Elementos de Logica Sequencial Rev2013Documento23 páginas2 Elementos de Logica Sequencial Rev2013Joao LuisAinda não há avaliações

- Introdução Aos Sistemas DigitaisDocumento2 páginasIntrodução Aos Sistemas DigitaisGustavo SábioAinda não há avaliações

- Comandos BasicosDocumento116 páginasComandos BasicosCarlos CordeiroAinda não há avaliações

- Lista de Exercicios de Eletricidade Basica e Eletronica-Tecnico de InstrumentacaoDocumento20 páginasLista de Exercicios de Eletricidade Basica e Eletronica-Tecnico de InstrumentacaoCarlos Alberto Damasceno100% (1)

- Manual LogixproDocumento20 páginasManual LogixproDaniel de la CruzAinda não há avaliações

- Pratica LaboratorialDocumento20 páginasPratica LaboratorialHudson GasparAinda não há avaliações

- Apostila - FlipFlop v3 PDFDocumento30 páginasApostila - FlipFlop v3 PDFAlberto LeoneAinda não há avaliações

- Capítulo II - MultivibradoresDocumento14 páginasCapítulo II - MultivibradoresBrenda EspostiAinda não há avaliações

- Atividade Pratica 8 Contador e FpgaDocumento9 páginasAtividade Pratica 8 Contador e FpgaAnderson MartinsAinda não há avaliações

- Apostila Eletronica Digital Aula 3Documento29 páginasApostila Eletronica Digital Aula 3FabricioBrantAinda não há avaliações

- Flip-Flops e Registradores de DeslocamentoDocumento28 páginasFlip-Flops e Registradores de DeslocamentoAugusto Rodrigues0% (1)

- Fechadura Combinacional..Documento19 páginasFechadura Combinacional..Chrystian BorgesAinda não há avaliações

- Simbologia IEEE PDFDocumento20 páginasSimbologia IEEE PDFjeovanevsAinda não há avaliações

- Aula01 1S19 Teoria Rev1Documento10 páginasAula01 1S19 Teoria Rev1gustavo luizAinda não há avaliações

- Aula 18 - Maquina de Estados - P2 PDFDocumento61 páginasAula 18 - Maquina de Estados - P2 PDFYoseph MichaelAinda não há avaliações

- Resumo MultivibradoresDocumento8 páginasResumo MultivibradoresCrislaine NogueiraAinda não há avaliações

- Portas Lógicas TTLDocumento29 páginasPortas Lógicas TTLkikos200Ainda não há avaliações

- Aula 09 - Contadores UP-DOWN e Carga ParalelaDocumento28 páginasAula 09 - Contadores UP-DOWN e Carga ParalelaAntónio CorreiaAinda não há avaliações

- Se 141Documento82 páginasSe 141Yuri WentzcovitchAinda não há avaliações

- Prova de Circuitos Digitais - EST SetubalDocumento44 páginasProva de Circuitos Digitais - EST SetubalNatan Hespanhol50% (2)

- FLIP-FLOPS e Dispositivos CorrelatosDocumento48 páginasFLIP-FLOPS e Dispositivos CorrelatosEduardo MendesAinda não há avaliações

- Cronometro DigitalDocumento5 páginasCronometro DigitalJosevaldo ArrudaAinda não há avaliações

- SE168Documento94 páginasSE168g30.miranda100% (1)

- Aula 09 Eletrônica DigitalDocumento38 páginasAula 09 Eletrônica DigitalAna Paula CardosoAinda não há avaliações

- Apostila MicroControladoresDocumento173 páginasApostila MicroControladoresPriscila Garcia MendesAinda não há avaliações

- Laboratorio de Sistemas DigitaisDocumento32 páginasLaboratorio de Sistemas DigitaisEduardo Sanches SalesAinda não há avaliações

- Lista de Exercícios - Máquinas de EstadoDocumento4 páginasLista de Exercícios - Máquinas de EstadoThiago AbrantesAinda não há avaliações

- Lista 1Documento4 páginasLista 1wfsouza2010Ainda não há avaliações

- Circuitos Sequenciais Flip-Flops e AplicaesDocumento18 páginasCircuitos Sequenciais Flip-Flops e AplicaesArthurAinda não há avaliações

- Ra115408 Ra109882 Ra107975Documento19 páginasRa115408 Ra109882 Ra107975Gabriel PavanAinda não há avaliações

- Poligrafo Completo Conceitos de Computação IIDocumento130 páginasPoligrafo Completo Conceitos de Computação IIKarol BeckmanAinda não há avaliações