Escolar Documentos

Profissional Documentos

Cultura Documentos

Um Retificador Monofásico Com Elevado Fator de Potência Baseado No Conversor Buck Multinível em Corrente

Enviado por

benitez leonel borinelliTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Um Retificador Monofásico Com Elevado Fator de Potência Baseado No Conversor Buck Multinível em Corrente

Enviado por

benitez leonel borinelliDireitos autorais:

Formatos disponíveis

UM RETIFICADOR MONOFÁSICO COM ELEVADO FATOR DE POTÊNCIA

BASEADO NO CONVERSOR BUCK MULTINÍVEL EM CORRENTE

Estêvão Coelho Teixeira e Henrique A. C. Braga

Núcleo de Automação e Eletrônica de Potência – NAEP

Universidade Federal de Juiz de Fora – UFJF

Caixa Postal 422 – CEP 36.001-970 – Juiz de Fora – MG – Brasil

estevaoc@jfnet.com.br - hbraga@engelet.ufjf.br

Resumo – Este artigo descreve um conversor estático ca- conduzida e irradiada. Tais benefícios são de grande

cc monofásico consistindo de uma ponte retificadora interesse em aplicações industriais.

convencional a diodos associada a um conversor cc-cc Uma revisão da teoria sobre conversores multiníveis em

buck multinível em corrente de duas células. Dependendo tensão e corrente foi apresentada em [4], onde são discutidas

da estratégia de comutação adotada, a estrutura pode estruturas baseadas tanto na associação de conversores como

apresentar uma corrente de entrada com até cinco níveis na associação de células de comutação [5]. A célula de

e fator de potência de deslocamento unitário, levando a comutação é uma estrutura de três terminais envolvendo dois

uma operação com elevado fator de potência, além de interruptores operando de forma complementar, estando

permitir a divisão equilibrada da corrente total de saída presente na maioria dos conversores estáticos.

através de duas células de comutação. Esta estrutura, que Os conversores multiníveis em corrente (MNC) consistem

opera com comutação em baixa freqüência, é adequada em uma alternativa para promover a associação de células de

para aplicações de cargas cc altamente indutivas. Uma comutação em paralelo, e foram descritos detalhadamente

breve revisão sobre estruturas anteriores que levaram ao em [6]. A nova técnica já foi aplicada a conversores cc-cc,

desenvolvimento da nova topologia é apresentada, bem inversores e até a retificadores trifásicos com elevado fator

como resultados de simulação e resultados experimentais de potência. Sua aplicação a retificadores monofásicos,

para um protótipo de 2 kW implementado em contudo, foi até agora objeto de especulação teórica.

laboratório. A melhoria do fator de potência (FP) em retificadores mo-

nofásicos está normalmente associada à utilização de um pré-

regulador boost, operando em alta freqüência, ligado à saída

Abstract - This paper introduces a single-phase ac-to-dc

de uma ponte retificadora a diodos [7]. Um retificador com

static converter, which consists of a conventional diode

correção do fator de potência e operação em alta freqüência

bridge cascaded by a two-cell current multilevel buck dc-

que emprega a modulação multinível em tensão foi

to-dc converter. Depending upon the switching strategy,

apresentado em [8]. Estas técnicas, no entanto, não são

the structure input current can present up to five levels

adequadas para aplicações em altas potências, devido às

and provide a unity displacement power factor, leading to

restrições tecnológicas dos interruptores estáticos. Assim,

a high power factor operation, and a balanced

técnicas de melhoria do fator de potência que empreguem

distribution of output current among two commutation

comutação em baixa freqüência são mais recomendáveis,

cells. This low-frequency switching circuit is proper to

sobretudo na presença de correntes mais elevadas. O

highly inductive dc loads. It is also presented a brief

retificador baseado no conversor boost também pode operar

review of structures that led to the development of the

em baixa freqüência, com o interruptor principal sendo

new topology. Simulation results for the proposed circuit

acionado durante um pequeno intervalo do período de

and experimental results for a 2-kW prototype,

comutação, normalmente uma ou duas vezes no período [9,

implemented in laboratory, are also presented.

10]. No entanto, seja em alta seja em baixa freqüência, o

conversor “ca-cc boost” aplica-se melhor a cargas com saída

em tensão (comumente uma carga resistiva em paralelo com

I. INTRODUÇÃO

um capacitor de filtragem). Por outro lado, boa parte das

cargas cc apresenta uma característica de saída

Os conversores multiníveis têm surgido como uma nova

preponderantemente indutiva.

classe de conversores estáticos de energia durante os últimos

Os retificadores controlados e semicontrolados a tiristor

anos [1, 2]. Diversas topologias e técnicas de modulação

tradicionais [11] podem ser aplicados a cargas cc fortemente

foram desenvolvidas para estes conversores, sobretudo em

indutivas. Embora de uso difundido na indústria, estes

aplicações de altas potências [3]. A principal motivação para

conversores operam com um baixo fator de potência. Além

o emprego de estruturas multiníveis é a capacidade de

disso, apresentam componentes harmônicas de baixa ordem

assegurar uma distribuição equilibrada da tensão (ou

que prejudicam a qualidade da energia da rede elétrica. Por

corrente) através de uma associação de interruptores

estes motivos, tais equipamentos não se ajustam facilmente

estáticos. Entretanto, é possível ainda otimizar o conteúdo

aos limites estabelecidos quanto ao fator de potência, bem

harmônico das tensões e/ou correntes nas estruturas e

como aos determinados pelas normas e recomendações

proporcionar menores níveis de interferência eletromagnética

internacionais sobre emissão de harmônicos [12].

62 Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002.

O controle simétrico do ângulo de disparo/extinção dos

interruptores [13] é uma técnica em baixa freqüência para se

obter uma melhoria do fator de potência em retificadores

alimentando cargas altamente indutivas, em alternativa aos

retificadores convencionais a tiristor. Isto pode ser

implementado através da utilização de GTOs no lugar de

tiristores, ou empregando para os tiristores alguma técnica de

comutação forçada, resultando nas formas de onda da tensão

e corrente de entrada ilustradas na Figura 1. Neste caso, o

retificador apresenta uma corrente de entrada 3 níveis com

sua componente fundamental em fase com a tensão de Figura 3 – Diagrama de blocos do conversor proposto.

entrada (ϕ1 = 0o), correspondendo a um fator de potência de

deslocamento unitário, o que melhora o FP da estrutura. Devido à presença do conversor buck na estrutura do

O conceito de conversores multiníveis em corrente pode retificador, a nova topologia recebe a denominação

ser empregado na implementação de retificadores com retificador buck MNC e será apresentado na próxima seção.

elevado fator de potência, sendo que a comutação ocorre em Um trabalho anterior sobre a estrutura proposta foi

baixa freqüência. A Figura 2 ilustra formas de onda de tensão apresentado pelos autores em [15].

e corrente de entrada idealizadas em um retificador

monofásico MNC 5 níveis. É possível minimizar a distorção

harmônica total (DHT) da corrente de entrada através do II. O RETIFICADOR MONOFÁSICO MNC 5 NÍVEIS

adequado ajuste dos ângulos α e φ. Um retificador trifásico

baseado na técnica MNC foi apresentado em [14]. A Figura 4 mostra a célula MNC genérica, baseada na

conexão em paralelo de células de comutação por meio de

O presente trabalho propõe um retificador monofásico

empregando comutação em baixa freqüência, apresentando indutores denominados indutores de equilíbrio. A estrutura

fator de deslocamento unitário, baseado no conversor buck foi originalmente proposta como uma técnica alternativa para

promover o paralelismo dos interruptores estáticos [16], e

multinível em corrente (MNC), conforme representado de

forma simplificada na Figura 3. A estrutura proposta é capaz corresponde ao dual de uma célula genérica multinível em

de promover a distribuição equilibrada da corrente total entre tensão, proposta em [17].

Empregando-se “atrasos” nos pulsos aplicados aos

dois ou mais interruptores, podendo ser comandada de forma

a apresentar uma corrente de entrada multinível. Assim, a interruptores, a estrutura pode apresentar múltiplos níveis

estrutura proposta pode apresentar fator de potência elevado, para a sua corrente de entrada ii, entre 0 e Io, sendo Io o valor

médio da corrente que sai do nó C, indicado na figura. A

especialmente para tensões de saída próximas da nominal,

sendo bastante adequada para cargas cc altamente indutivas, Figura 5 mostra o uso da célula MNC em um retificador

tais como acionamentos de máquinas cc, eletroímãs de MNC 5 níveis. A estrutura é derivada de um inversor com

levantamento e freios elétricos. É fácil concluir que o sistema entrada em corrente (CSI) 5 níveis [18,19], tendo sido

pode ser alimentado também a duas fases, o que representa abordada de forma teórica em [6].

um incremento significativo na capacidade de potência total

ii

do conversor.

T1

i Sn i S3 i S2 i S1

Sn S3 S2 S1

L n-1 L2 L1 C Io

vi

i n-1 i2 i1

S n' S 3' S 2' S 1'

T2

Figura 4 – A célula MNC genérica.

Figura 1 – Tensão e corrente de entrada em retificador

empregando controle simétrico do ângulo.

Figura 2 – Tensão de entrada senoidal e corrente de entrada com

cinco níveis em um retificador MNC. Figura 5 – Um retificador MNC cinco níveis

baseado em um inversor CSI.

Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002. 63

Dependendo da configuração para a qual for destinada a A

célula MNC, pode-se ter uma tensão de entrada vi contínua ii

ou alternada. Para conversores cc-cc, tem-se uma tensão Db1 Db3 iS2 iS1

S2 S1

contínua na entrada, sendo os interruptores inferiores da + L1 C

Lo

célula substituídos por interruptores passivos (diodos). Os vi

terminais T1, T2 e C são, neste caso, designados por A (ativo), - i1 io

D2 iD2 D1 iD1 vo Ro

P (passivo) e C (comum). A Figura 6 ilustra a aplicação da Db4 Db2

célula MNC em um conversor buck. Para este circuito, a

célula MNC consiste da associação de duas células de P P

comutação conectadas através do indutor de equilíbrio L1, Figura 7 – O retificador buck MNC 5 níveis.

sendo o circuito denominado, então, conversor buck MNC 2

7.5V

células.

A célula MNC pode, entretanto, ser formada por n células 5.0V

de comutação, sendo possível adaptá-la a todos os 2.5V

conversores cc-cc não-isolados (buck, boost, buck-boost, 0V

ćuk, sepic e zeta) [20]. V(Vg1) V(Vg2)*1.2

O retificador MNC 5 níveis proposto neste trabalho tem, 200V

como parte integrante de sua estrutura, o conversor buck

0V

MNC 2 células, com uma ponte retificadora convencional a

diodos substituindo a fonte cc. O circuito é mostrado na -200V

Figura 7. O ramo de saída é constituído por uma carga RL, V(Vi:+,Vi:-)

representando uma carga altamente indutiva. 20A

Uma vez que o circuito opera com baixa freqüência de

0A

comutação, o indutor de equilíbrio L1 deve ser confeccionado

em núcleo de ferro-silício. A principal vantagem oferecida -20A

pela nova topologia em relação ao retificador cinco níveis I(i)

MNC da Figura 5 é o número reduzido de interruptores 200V

ativos, além de uma estratégia de comutação

0V

significativamente mais simples.

A corrente total de saída io pode assim ser distribuída de -200V

forma segura através dos interruptores do retificador sem que V(Lo:1,Ro:2)

a estrutura incorra nas dificuldades oferecidas pelo 20A

paralelismo convencional de interruptores estáticos. 10A

0A

III. RESULTADOS DE SIMULAÇÃO I(S1)

20A

Considere, para o retificador buck MNC 5 níveis da

10A

Figura 7, os seguintes parâmetros de simulação: Vca = 127 V,

f = 60 Hz, Ro = 5 Ω, Lo = 100 mH, L1 = 60 mH e ron = 0A

0,01 Ω. Tais parâmetros representam, respectivamente, a I(S2)

tensão eficaz de entrada, a freqüência da rede, a resistência e 30A

indutância da carga, a indutância de equilíbrio e a resistência

de condução dos interruptores ativos e diodos. Os ângulos α

20A

e φ (ver Figura 2) são, respectivamente, 12,6o e 26,8o.

Para simulação do circuito no software PSpice®, foram Io

empregados interruptores comandados por sinal de tensão 10A

(Sbreak). Foi adotado o modelo Dbreak para os diodos. A

I1

simulação levou às formas de onda mostradas na Figura 8.

0A

4.00s 4.01s 4.02s 4.03s

ii Célula MNC

I(Lo) I(L1) AVG(I(Lo)) AVG(I(L1))

A

Time

iS2 iS1 Figura 8 – Formas de onda simuladas para o retificador. De cima

S2 S1 para baixo: pulsos de comando de S1 e S2; tensão e corrente de

+ i1

entrada; tensão na carga; corrente em S1 e S2; corrente de saída e

Vi C

corrente no indutor de equilíbrio L1.

- L1

iD2 iD1 Io vo

D2 D1

Do gráfico inferior da figura, observa-se que o valor

médio da corrente no indutor de equilíbrio L1, I1, é a metade

P P do valor de Io, o que indica o equilíbrio de corrente entre

Figura 6 – Um conversor buck MNC 2 células. interruptores ativos e diodos do retificador.

64 Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002.

O espectro harmônico da corrente de entrada é mostrado Assim, optou-se neste trabalho, por otimizar o retificador

na Figura 9. Para a corrente de entrada, a DHT obtida para de forma a obter a DHTi mínima o que resulta,

40 harmônicas foi de 15,6 %. conseqüentemente, em um máximo FP de acordo com a

Apesar de algumas componentes harmônicas possuírem equação (1).

amplitudes relativamente expressivas, o conversor pode Para a análise da DHTi mínima considerou-se a situação

apresentar um FP bastante elevado, cuja expressão geral é: ideal da Figura 2, ou seja Lo e L1 são tais que a ondulação

nos níveis da corrente de entrada é desprezível. Desta forma,

FPD

FP = . (1) a expressão para ii, em termos da série de Fourier, é dada

1 + DHTi 2 por:

Onde FPD é o fator de potência de deslocamento e DHTi é a ∞

2I o

distorção harmônica total da corrente de entrada. i (t ) = ∑

π ( 2 n − 1) n =1

{cos[( 2 n − 1)α ] +

(3)

O ângulo de deslocamento ϕ1 obtido foi de –2,38 o + cos[( 2 n − 1) ⋅ (α + φ )]}. sen[( 2 n − 1)ω t ]

(FPD ≅ 1). Substituindo os valores encontrados para DHTi e

FPD em (1), obtém-se um fator de potência igual a 0,987 para A amplitude da componente harmônica de ordem h, com

o circuito simulado. h = 1,3,5,..., designada por Ih, é dada por:

Para um retificador buck MNC ideal (ron = 0), o valor

2I o

médio da tensão de saída, Vo, é dado pela expressão:

Ih = {cos(hα ) + cos[h ⋅ (α + Φ)]}. (4)

πh

1 π − (α +φ )

π ∫α

Vo = ⋅ 2 .Vca . sen(θ ) dθ =

A DHTi é dada por:

(2)

⋅ [cos(α ) + cos(α + φ )] .

2 .Vca

2

π I ∞

DHTi (%) = 100 × ∑ h . (5)

h =2 I i 1

Para os ângulos α e φ empregados na simulação, a

expressão (2) resultaria em Vo = 100 V. Devido às quedas de

Onde Ii1 é a amplitude da componente fundamental de ii.

tensão nos interruptores e diodos, obteve-se, para o circuito

Através de (2), (4) e (5) é possível, por meio de um método

simulado, Vo = 98,3 V.

numérico, encontrar os ângulos α e φ que minimizam a DHTi

para um determinado valor de Vo, sendo assim denominados

ângulos ótimos.

IV. OTIMIZAÇÃO DA DISTORÇÃO HARMÔNICA

TOTAL DA CORRENTE DE ENTRADA As curvas mostrando a DHTi mínima e os ângulos ótimos,

ambas em função da tensão de saída que seria obtida em um

retificador buck MNC ideal (sem perdas nos interruptores),

De acordo com (2), a escolha adequada de um par de

são mostradas, respectivamente, nas Figuras 10 e 11.

ângulos α,φ permite o ajuste da tensão de saída Vo.

A tensão de saída é expressa na forma normalizada, Vo,n,

Entretanto, existem diversos pares de ângulos que

dada por:

produziriam um dado valor Vo. Para orientar a escolha, pode-

se optar por determinar pares de ângulos de forma que se

Vo

minimizem componentes harmônicas específicas, a fim de

Vo , n = . (6)

verificar a adequação do sistema a regulamentações Vo ,base

pertinentes, e.g. IEC 61000-3-4, Porém, de acordo com a

própria IEC, tal documento é considerado uma

“recomendação técnica”, não se enquadrando ainda na Onde:

categoria de norma internacional.

Vo,base = Vo (α = φ = 0°) . (7)

Foi adotado um limite para o ângulo φ de 30o. Ora,

maiores valores de φ implicam em ondulação acentuada da

corrente no indutor de equilíbrio, pois é neste intervalo que

tal elemento se submete à tensão de entrada. Isto, por

conseguinte, exige uma indutância mais elevada para garantir

a distribuição eqüitativa de corrente nas chaves e para

preservar a constituição multinível da corrente. Em

conseqüência, o volume e peso do conversor podem

aumentar desfavoravelmente. Foi adotado ainda:

Ordem das harmônicas, h

α + φ ≤ 80° . (8)

Figura 9 – Espectro harmônico da corrente de entrada.

Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002. 65

Esta restrição se dá em função de características próprias sobrecarregando uma das duas células de comutação

do circuito de comando desenvolvido para o protótipo, o qual constituintes da célula MNC do retificador.

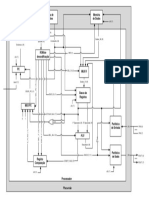

rejeita uma entrada de dados α,φ cuja soma exceda 80 graus. O circuito de sincronismo e geração de pulsos é descrito

O objetivo aqui é garantir um tempo mínimo para que o pelo diagrama de blocos da Figura 13. Um microcontrolador

sistema de geração de pulsos possa executar as rotinas de de 8 bits constitui sua unidade principal. O sistema, após

leitura de dados (vj. Seção V). Como os resultados transformar o sinal da tensão de entrada vi em uma onda

experimentais para a DHTi foram posteriormente quadrada TTL (vi’), aplica o sinal vi’ à entrada de um circuito

comparados com os valores teóricos, foi de interesse de malha amarrada por fase (PLL), responsável por

considerar a restrição expressa por (8) no algoritmo para promover o sincronismo dos pulsos vg1 e vg2 com a tensão vi,

obtenção da curva da Figura 10. sendo este o único sinal externo necessário para a operação

do sistema.

Os pulsos vvco, produzidos na saída do oscilador

controlado por tensão (VCO), interno ao circuito PLL, são

aplicados à entrada do contador integrante do

microcontrolador. O programa do microcontrolador

(firmware), por sua vez, realiza a contagem destes pulsos

(com freqüência 1800 vezes superior à de vi’) de forma a

produzir os pulsos de comando, de acordo com os ângulos α

e φ, cujos valores são fornecidos pelo usuário através de um

teclado numérico.

O sinal vvco’ é realimentado no comparador de fase do

PLL, tendo, para o sistema em equilíbrio, a mesma

freqüência de vi’. Os sinais vg1 e vg2 são aplicados a circuitos

de interfaceamento (drivers) adequados aos dispositivos

utilizados para implementar S1 e S2, gerando assim os sinais

vg1’ e vg2’.

Figura 10 – DHTi mínima, em função da tensão O microcontrolador de 8 bits adotado foi o AT89S8252

de saída normalizada. (Atmel), enquanto o circuito PLL empregado foi

o CD4046BC (Fairchild). O uso de um sistema

microcontrolado permite ao usuário não somente ajustar a

tensão de saída, mas também entrar com o valor numérico

dos ângulos α e φ. Adicionalmente, este sistema poderia ser

empregado para responder a uma estratégia especificada de

controle em malha fechada, o que se pretende desenvolver no

futuro.

VI. RESULTADOS EXPERIMENTAIS

Um protótipo de 2 kW para o retificador buck MNC foi

implementado em laboratório (Figura 14). Neste caso, Q1 e

Q2 são IGBTs IRG4PC30W (International Rectifier),

enquanto D1 e D2 são diodos MUR1540. Embora estes

componentes sejam de comutação rápida, o seu emprego se

deu em função da disponibilidade em laboratório e

Figura 11 – Ângulos ótimos do retificador adequação aos níveis de tensão e corrente exigidos. Em uma

(o valor máximo de φ foi restrito a 30o). aplicação prática do retificador, porém, componentes lentos

(e.g. IGBT’s de 1a geração) poderiam ser utilizados. Por

V. O CIRCUITO DE SINCRONISMO outro lado, a ponte retificadora utilizada (KBPC3504) é

E GERAÇÃO DE PULSOS própria para operação em baixa freqüência.

O circuito de sincronismo e geração de pulsos desempenha

um papel fundamental na operação da estrutura proposta.

Além de promover o sincronismo entre os pulsos de

comando e a tensão ca de entrada, o circuito deve ainda

garantir que os intervalos de tempo ∆tα(1) e ∆tα(2), bem como

∆tφ(1) e ∆tφ(2), sejam iguais, como ilustra a Figura 12,

representando a tensão de saída da ponte retificadora e os

pulsos de comando dos interruptores, vg1 e vg2. Pequenas

assimetrias entre estes intervalos poderiam causar um

desequilíbrio degenerativo de corrente nos interruptores, Figura 12 – Representação da tensão na saída da ponte retificadora e

descaracterizando a operação multinível do retificador e pulsos de comando vg1 e vg2.

66 Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002.

60Hz Para a corrente de entrada, a DHTi obtida para 40

harmônicas foi de 15,3%, com um ângulo de deslocamento

v i' +

FILTRO

PASSA- vi

de 0,28o (FPD ≅ 1). De acordo com (1), o fator de potência

-

BAIXA obtido foi de 0,989.

Pode-se observar na Figura 15 a presença de distúrbios na

PLL

tensão de entrada. Tais distorções provocaram uma DHT de

Entrada

do PLL

FILTRO

tensão de entrada de 4,48% (contra 3,32% para o sistema a

COMPARADO R

DE FASE

PASSA- VCO vazio). A utilização de um circuito de ajuda à comutação

BAIXA

Entrada do

com parador

(snubber) associado aos IGBT’s, como mostra a

de fase Figura 19, poderia reduzir consideravelmente tais distúrbios,

através da redução das taxas di/dt para a corrente de entrada

v vco '

nas transições. A Figura 20 mostra a tensão e corrente de

M IC R O C O N TR O LAD O R v vco entrada simuladas para o retificador buck MNC 5 níveis

α ,Φ

D E 8 B ITS Entrada do

Contador empregando o circuito de ajuda à comutação da Figura 19.

Foram mantidos os parâmetros de simulação da seção III,

v g1 v g1 ' tendo sido incluídos: Ls = 0,2 mH, Lsnb = 4 mH, Csnb = 33 µF

e Rsnb = 100 Ω. Neste caso, a DHT da tensão de entrada ficou

1 2 3 S1

4 5 6 DRIVERS em 1,24%, enquanto que para a corrente multinível obteve-se

7 8 9 v g2 v g2 ' 13,74%. A investigação de um snubber ótimo, bem como sua

CANCELA 0 S2

ENTRA

implementação prática são objetos de futuros trabalhos.

Figura 13 – O circuito de sincronismo e geração de pulsos.

KBPC3504

Filtro de

Rede ca entrada

Db1 Db3 Q2 Q1

Ls

Vs 10 Rc

Lo

L1 0,22

6,8 uF 100mH

60mH

Ro

D2 D1

Db4 Db2 4.1

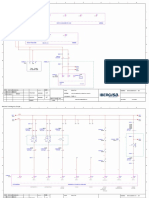

Figura 14 – Diagrama esquemático do protótipo

implementado em laboratório.

Um filtro de entrada RC foi inserido no circuito, com o

intuito de minimizar distúrbios na tensão de entrada causados Figura 15 – Tensão e corrente de entrada, para α = 12,6o e φ = 26,8o

pela transição rápida nos níveis de corrente de entrada (5 ms/div; 100 V/div; 20 A/div).

durante a entrada em condução/bloqueio dos IGBTs. Isto

ocorre devido às tensões induzidas L.di/dt nas indutâncias da

rede ca, representadas por Ls na Figura 14.

A resistência Rc de 0,22 Ω foi utilizada para compensar a

resistência interna do indutor de equilíbrio L1, de forma a

garantir a divisão adequada da corrente nos interruptores da

célula MNC. Embora a técnica de compensação resistiva

introduza algum acréscimo nas perdas totais do circuito, o

seu emprego no protótipo desenvolvido justificou-se pela

simplicidade de implementação. Em trabalhos futuros, no

entanto, poderão ser adotadas outras técnicas de

compensação que não utilizem Rc, como o controle dinâmico

na largura de pulso dos sinais de comando dos interruptores.

Nesse caso, há a necessidade de um sistema de controle em

malha fechada com sensores de corrente.

Em laboratório foram realizados ensaios exaustivos com o

protótipo, tendo sido adquiridas curvas típicas para o

retificador operando com α = 12,6o e φ = 26,8o que são aqui

incluídas. A Figura 15 mostra a tensão e a corrente de

entrada do retificador. As Figuras 16, 17 e 18 mostram outras Figura 16 – Correntes nos IGBTs (5 ms/div; 10 A/div).

formas de onda de interesse.

Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002. 67

200V

0V

SEL>>

-200V

V(input:+,0)

20A

0A

-20A

320ms 330ms 340ms 350ms 360ms

I(input)

Time

Figura 20 – Tensão e corrente de entrada simuladas para o

retificador buck MNC 5 níveis empregando o circuito de ajuda à

Figura 17 – Corrente de saída e corrente no indutor de equilíbrio comutação da Figura 19.

(5 ms/div; 5 A/div).

Figura 18 – Tensão de saída e tensão em Ro Figura 21 – Curva de rendimento do retificador buck MNC 5 níveis.

(5 ms/div; 50 V/div).

Lsnb

Dsnb Rsnb

Q1

Csnb

Figura 19 – Circuito de ajuda à comutação.

Variando-se a tensão de saída utilizando os ângulos ótimos

da Figura 11, foi obtida a curva de rendimento do retificador,

mostrada na Figura 21. Foram obtidas ainda as curvas

Figura 22 – Valores experimentais para a DHT da

experimentais da DHTi (Figura 22) e do fator de potência do corrente de entrada.

retificador (Figura 23).

68 Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002.

retificadores com comutação em baixa freqüência baseados

na técnica multinível em corrente.

Um estudo sobre condicionamento harmônico e adequação

a normas será implementado como continuidade deste

trabalho. Ressalta-se, porém, a possibilidade de operação

com um maior número de níveis intermediários (empregando

um conversor buck com mais de duas células MNC), o que

certamente flexibilizará a minimização de componentes

harmônicas específicas.

REFERÊNCIAS BIBLIOGRÁFICAS

[1] J. S. Lai, F. Z. Peng, “Multilevel Converters – A New

Breed of Power Converters”, IEEE Transactions on

Industry Applications, vol. 32, no. 3, pp. 509-517,

May/June 1996.

Figura 23 – Curva do fator de potência obtido para o retificador. [2] J. Rodrigues, J. S. Lai, F. Z. Peng, “Multilevel Inverters:

A Survey of Topologies, Controls, and Applications”,

Em virtude da queda de tensão nos componentes do IEEE Transactions on Industrial Electronics, vol. 49,

retificador, incluindo a resistência parasita do indutor de no. 4, pp. 724-738, August 2002.

equilíbrio foram registrados, para a tensão de saída, valores [3] F. Z. Peng, J. S. Lai, J. W. McKeever, J. VanCoevering,

menores do que os que seriam obtidos usando os pares α,φ “A Multilevel Voltage-Source Inverter with Separate

em (2). Para α = 12,6o e φ = 26,8o, a tensão de saída medida DC Sources for Static Var Generation”, IEEE

foi de aproximadamente 86 V (em lugar de 100 V, no caso Transactions on Industry Applications, vol. 32, no. 5,

teórico). Estuda-se obter uma equação mais rigorosa que a pp. 1130-1138, Sep/Oct 1996.

equação (2), a fim de refletir este efeito. Entretanto, para [4] H. A. C. Braga, I. Barbi, “Conversores Estáticos

cada par α,φ utilizado na obtenção da curva da Figura 22, os Multiníveis – Uma Revisão”, Revista da SBA - Controle

valores experimentais de DHTi mostraram-se muito & Automação, vol. 11, no. 01, pp. 20-28, janeiro a

próximos dos valores teóricos, mostrados na Figura 10 para abril.de 2000.

uma forma de onda 5 níveis ideal, sobretudo para os valores [5] V. Vorpérian, “Simplified Analysis of PWM Converters

maiores de tensão de saída. Using Model of PWM Switch; Part I: Continuous

Conduction Mode”, IEEE Transactions on Aerospace

VII. CONCLUSÕES and Electronics Systems, Vol.. 26, No. 3, pp. 490-496,

May 1990.

Este trabalho apresentou um novo retificador multinível [6] H. A. C. Braga, “Conversores Multiníveis em Corrente”,

em corrente baseado no conversor buck-2 células, capaz de Tese de doutorado, UFSC, Florianópolis, 1996.

estabelecer uma corrente de entrada com até cinco níveis. Se [7] J.-S. Lai, D. Hurst, T. Key, “6 Switch-Mode Supply

comparado com outras alternativas, a nova estrutura Power Factor Improvement Via Harmonic Elimination

apresenta a vantagem de promover a divisão da corrente de Methods”, in Applied Power Electronics Conference and

saída através de duas células de comutação, empregando um Exposition, 1991. APEC '91, Conference Proceedings,

número reduzido de interruptores ativos. pp. 415-422, Mar. 1991.

Através do comando dos interruptores ativos empregando [8] B. R. Lin, H. H. Lu, “A Novel PWM Scheme for Single-

pulsos de mesma largura, defasados de um ângulo φ, Phase Three-Level Power-Factor-Correction Circuit”,

mostrou-se possível ajustar a tensão de saída do retificador IEEE Transactions on Industrial Electronics, vol. 47,

drenando da fonte ca uma corrente de entrada com DHT no. 2, pp. 245-252, April 2000.

reduzida, levando a estrutura a operar com elevado fator de [9] M. S. Elmore, W. A. Peterson, D. Sherwood, “A Power

potência, empregando comutação em baixa freqüência. Isto Factor Enhancement Circuit”, in Applied Power

pode ser comprovado através da comparação entre os Electronics Conference and Exposition, 1991, APEC

resultados experimentais para a tensão e corrente de entrada '91. Conference Proceedings, pp. 407-414, Mar. 1991.

(Figura 15) com as formas de onda ideais da Figura 2. A [10] Suga, M. Kimata, Y. Ohnishi, R. Uchida, “New

estrutura monofásica é adequada, assim, a aplicações Switching Method for Single-Phase AC to DC

envolvendo cargas cc altamente indutivas. Converter”, Power Converters Conference, Yokohama,

A estratégia de sincronismo associada à geração dos 1993, pp. 93-98, Apr. 1993.

pulsos de comando dos interruptores, através de um circuito [11] N. Mohan, T. M. Undeland, W. P. Robbins, Power

digital apropriado, mostrou-se imprescindível para garantir o Electronics – Converters, Applications and Design. John

equilíbrio de corrente entre os interruptores da célula MNC, Willey & Sons, Inc., 1989.

intrínseca à estrutura do retificador buck MNC 5 níveis. [12] R. Redl, P. Tenti, J. Daan van Wyk, “Power Electronics’

O circuito descrito neste trabalho e os resultados Polluting Effects”, IEEE Spectrum, vol. 34, no. 5, pp.

experimentais obtidos constituem, assim, uma referência para 32-39, May 1997.

o desenvolvimento de retificadores buck MNC com mais de [13] M H. Rashid, Eletrônica de Potência – Circuitos,

cinco níveis, bem como para o estudo de outras topologias de Dispositivos e Aplicações; Makron Books, 1999.

Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002. 69

[14] Y. B. Blauth, I. Barbi, “A Phase-Controlled 12-Pulse DADOS BIOGRÁFICOS

with Unity Displacement Factor without Phase Shifting

Transformer”, Applied Power Electronics Conference Estêvão Coelho Teixeira nasceu em São Paulo (SP), em

and Exposition, 1998, APEC '98. Conference 28/06/1974. Graduou-se em Engenharia Elétrica em 1998

Proceedings, vol. 2, pp. 970-976, Feb. 1998. pela Universidade Federal de Juiz de Fora, onde concluiu

[15] E. C. Teixeira, H. Braga, “A High Power Factor Single- recentemente o curso de mestrado em Engenharia Elétrica.

Phase Rectifier Based on a Current Multilevel Buck Atuou como instrutor de formação profissional no SENAI de

Converter”, Anais do 6o Congresso Brasileiro de Juiz de Fora em 1999/2000, nas áreas de Eletricidade e

Eletrônica de Potência – COBEP, pp. 180-185, 2001. Eletrônica. Suas áreas de interesse são conversores estáticos

[16] H. A. C. Braga, I. Barbi, “A New Technique for Parallel de energia, automação, microprocessadores e aplicações

Connection of Commutation Cells: Analysis, Design, industriais.

and Experimentation”, IEEE Transactions on Power

Electronics, vol. 12, no. 2, pp. 387-395, Mar. 1997.

[17] T. A. Meynard, H. Foch, “Multi-level Conversion: High Henrique A. C. Braga nasceu em Aimorés, MG, em

Voltage Choppers and Voltage-Source Inverters”, Anais 01/08/1959. Graduou-se em Engenharia Elétrica pela

do Power Electronics Specialists Conference Universidade Federal de Juiz de Fora (UFJF) em 1982. É

(PESC’91), pp. 397-403, 1992. professor dessa mesma universidade desde 1985. Obteve o

[18] F. M. Antunes, H. A. C. Braga, I. Barbi, “Application of título de Mestre em Engenharia Elétrica, sub-área Eletrônica

a Generalized Current Multilevel Cell to a Current de Potência, na COPPE/UFRJ em 1988. Em 1996 concluiu o

Source Inverter”, IEEE IECON 21st International curso de doutoramento, na mesma área do mestrado, pela

Conference, vol. 1, pp. 278-283, Nov. 1995. Universidade Federal de Santa Catarina, INEP-UFSC. Atuou

[19] F. M. Antunes, H. A. C. Braga, I. Barbi, “Application of como membro do Conselho Executivo da SOBRAEP em

a Generalized Current Multilevel Cell to Current-Source 1994. Atualmente é professor nos cursos de Graduação e Pós

Inverters”, IEEE Transactions on Industrial Electronics, Graduação (mestrado) em Engenharia Elétrica da UFJF,

vol. 46, no.1, pp. 31-38, Feb. 1999. lecionando disciplinas na área de Eletrônica Básica e

[20]H. Braga, I. Barbi, “Current Multilevel DC-DC Eletrônica de Potência. É Senior Member do IEEE e foi

Converters”, Anais do 3o Congresso Brasileiro de Diretor da Seção MG do IEEE no biênio 2000/2001 e re-

Eletrônica de Potência – COBEP ’95, pp. 417-422, Dec. eleito para o biênio 2002/2003.

1995.

70 Eletrônica de Potência – Vol. 7, no 1, Novembro de 2002.

Você também pode gostar

- Projeto Fontes Chaveadas Apostila FLYBACKDocumento24 páginasProjeto Fontes Chaveadas Apostila FLYBACKrnjlmv83100% (2)

- Livro Digital de Introdução Aos Sistemas Solares Novo PDFDocumento114 páginasLivro Digital de Introdução Aos Sistemas Solares Novo PDFRonaldo Kawamura89% (9)

- Catálogo MXT 2022Documento82 páginasCatálogo MXT 2022Davi SiqueiraAinda não há avaliações

- Biblioteca PthreadDocumento6 páginasBiblioteca PthreadgirlmalukettAinda não há avaliações

- História Da ProgramaçãoDocumento17 páginasHistória Da ProgramaçãoBennie HullAinda não há avaliações

- Técnicas de Programação - Texto Estruturado - SENAIDocumento10 páginasTécnicas de Programação - Texto Estruturado - SENAIHicaro Souza IDAinda não há avaliações

- Catalogo Adelco Institucional 2011Documento24 páginasCatalogo Adelco Institucional 2011Rafael FreitasAinda não há avaliações

- Conversor Zeta Trifásico PDFDocumento12 páginasConversor Zeta Trifásico PDFFabio FerreiraAinda não há avaliações

- Conversor C.C. - C.C. Boost Quadrático para Aplicação em PDFDocumento9 páginasConversor C.C. - C.C. Boost Quadrático para Aplicação em PDFDaniel AguiarAinda não há avaliações

- Natural Capacitor Voltage Balancing For A Flying Capacitor Converter Induction Motor DriveDocumento8 páginasNatural Capacitor Voltage Balancing For A Flying Capacitor Converter Induction Motor DriveAna Paula Henn WaengaAinda não há avaliações

- Modeling and Control of A Single-Phase Grid-Connected Inverter With LCL FilterDocumento10 páginasModeling and Control of A Single-Phase Grid-Connected Inverter With LCL FilterMinh Tạ ĐứcAinda não há avaliações

- Análise Do Comportamento de Geradores Síncronos A ÍmãsDocumento32 páginasAnálise Do Comportamento de Geradores Síncronos A Ímãseng.walter.soaresAinda não há avaliações

- Modelagem Do Inversor para Estudos de CMC - Hélder (2010)Documento6 páginasModelagem Do Inversor para Estudos de CMC - Hélder (2010)AndréAinda não há avaliações

- Estudo de Transformadores de Alta Frequência para Aplicação em Conversores de Tensão Cc-Ca Utilizados em UpsDocumento1 páginaEstudo de Transformadores de Alta Frequência para Aplicação em Conversores de Tensão Cc-Ca Utilizados em UpsRamon Thales DomeniconiAinda não há avaliações

- Conversor Duplo Forward PWM A Duas Chaves Principais e Duas ChavesDocumento6 páginasConversor Duplo Forward PWM A Duas Chaves Principais e Duas ChavesbrunoAinda não há avaliações

- Exemplo Trab Final EletrônicaDocumento10 páginasExemplo Trab Final EletrônicaFernanda Cardoso SettiAinda não há avaliações

- Cose JOB EdilsonDocumento15 páginasCose JOB EdilsonJeftacio MateusAinda não há avaliações

- 073 - Inversor Multinível Assimétrico Bidirecional Com 15 Níveis Na Tensão de Saída Usando Um Estágio Cc-Ca-Ca e Poucas ChavesDocumento6 páginas073 - Inversor Multinível Assimétrico Bidirecional Com 15 Níveis Na Tensão de Saída Usando Um Estágio Cc-Ca-Ca e Poucas ChavesTaymeson ChavesAinda não há avaliações

- Transmissao Corrente AlternadaDocumento11 páginasTransmissao Corrente AlternadaEd TrawtmamAinda não há avaliações

- Exercícios Dirigidos - Camila Salvador LuzernaDocumento6 páginasExercícios Dirigidos - Camila Salvador LuzernaCleiton NegosekeAinda não há avaliações

- ARTIGO RODOLFO - RBS Magazine ED 46 - PAG. 52Documento6 páginasARTIGO RODOLFO - RBS Magazine ED 46 - PAG. 52Luis Felipe Diniz RibeiroAinda não há avaliações

- Projeto Inversor CC-CADocumento6 páginasProjeto Inversor CC-CAViniciusCamargoGomesAinda não há avaliações

- Introdução A InversoresDocumento6 páginasIntrodução A Inversoresnadnho foxAinda não há avaliações

- Norma de Reatores - Iec 61000-3-2Documento6 páginasNorma de Reatores - Iec 61000-3-2Rodrigo BonfanteAinda não há avaliações

- Vanderlei Amaral Vieira Junior VOLUME 2641Documento37 páginasVanderlei Amaral Vieira Junior VOLUME 2641augusto_mendes_Ainda não há avaliações

- NBR 06548 - 1981 - Transmissão de Energia Elétrica em Corrente Contínua de Alta TensãoDocumento31 páginasNBR 06548 - 1981 - Transmissão de Energia Elétrica em Corrente Contínua de Alta Tensãoisrael saronAinda não há avaliações

- Luis DarioDocumento20 páginasLuis DarionilsocristovaolAinda não há avaliações

- Artigo Cooperativo UfsmDocumento6 páginasArtigo Cooperativo Ufsmjames blayne oliveira reisAinda não há avaliações

- No Breaks PDFDocumento5 páginasNo Breaks PDFGustavoAinda não há avaliações

- Compensador EstaticoDocumento6 páginasCompensador EstaticoRui OliveiraAinda não há avaliações

- Artigo - Eletrônica de Potência - Versão Final CorrigidoDocumento6 páginasArtigo - Eletrônica de Potência - Versão Final CorrigidoNada AzulAinda não há avaliações

- Hagy Railenno - Religadores e Reguladores de Tensão de Sistemas de DistribuiçãoDocumento10 páginasHagy Railenno - Religadores e Reguladores de Tensão de Sistemas de DistribuiçãoHagy RailennoAinda não há avaliações

- Fontes Chaveadas-Uma Visão GeralDocumento196 páginasFontes Chaveadas-Uma Visão GeralDaniel Gonçalves Araujo100% (1)

- Multifuncionalidade de Conversores Eletrônicos de Potência Utilizados em Microrredes InteligentesDocumento11 páginasMultifuncionalidade de Conversores Eletrônicos de Potência Utilizados em Microrredes InteligentesValber SoaresAinda não há avaliações

- 6919 UsingHighResolution BH 20190516 Web PT-BRDocumento12 páginas6919 UsingHighResolution BH 20190516 Web PT-BRVirnaAinda não há avaliações

- Elpot Cap2Documento59 páginasElpot Cap2Vasco RodriguesAinda não há avaliações

- Rvol 15 No 2 P 12Documento10 páginasRvol 15 No 2 P 12NiltoncientistaAinda não há avaliações

- Trabalho Eletronica de Potencia - Ronaldo Torres Da SilveiraDocumento6 páginasTrabalho Eletronica de Potencia - Ronaldo Torres Da SilveiraRonaldoDaSilveiraAinda não há avaliações

- Apostila Fontes Chaveadas PomilioDocumento196 páginasApostila Fontes Chaveadas PomilioAndre Ricardo MedeirosAinda não há avaliações

- CursoDocumento3 páginasCursoMabely Soares OliveiraAinda não há avaliações

- Transformador de Potencial Capacitivo-Monitorização Remota-SubestaçãoDocumento6 páginasTransformador de Potencial Capacitivo-Monitorização Remota-SubestaçãoengrobmacAinda não há avaliações

- Rvol 13 No 4 P 8Documento9 páginasRvol 13 No 4 P 8JOERDSON TIAGO BATISTA DA SILVAAinda não há avaliações

- 065 - Conversor CC-CC Buck Híbrido Com Filtro de Impedância SérieDocumento6 páginas065 - Conversor CC-CC Buck Híbrido Com Filtro de Impedância SériePedro Henrique Pompermayer VettoraciAinda não há avaliações

- Desenvolvimento e Construção de Nobreak MonofasicoDocumento7 páginasDesenvolvimento e Construção de Nobreak MonofasicoLuan CrozattiAinda não há avaliações

- CEPEL-Evaluation of STATCOM Model For Electromagnetic and Electromechanical Transients (2018)Documento6 páginasCEPEL-Evaluation of STATCOM Model For Electromagnetic and Electromechanical Transients (2018)Gustavo AguayoAinda não há avaliações

- Hager Folheto Cont Energia ArDocumento64 páginasHager Folheto Cont Energia Arezequiel luzAinda não há avaliações

- NBR 6548 Transmissão de Energia Elétrica em Corrente ContínuDocumento31 páginasNBR 6548 Transmissão de Energia Elétrica em Corrente Contínujorge uiliam pereira da encarnaçãoAinda não há avaliações

- Transporte e Distribuicao de EEDocumento130 páginasTransporte e Distribuicao de EEANTONIO LUIZ100% (1)

- Ermos e Nomenclaturas de ElétricaDocumento30 páginasErmos e Nomenclaturas de ElétricaEng. Clínica Hosp. Reg. da TransAmazonicaAinda não há avaliações

- SISTEMAS DE TRANSMISSÃO DE ENERGIA ELÉTRICA Sistemas de Transmissão - ArtigoDocumento3 páginasSISTEMAS DE TRANSMISSÃO DE ENERGIA ELÉTRICA Sistemas de Transmissão - ArtigoJESSE SAMPAIIOAinda não há avaliações

- Gerao2ea1 1232056265256376 1Documento24 páginasGerao2ea1 1232056265256376 1Haislan AraujoAinda não há avaliações

- Substações MT - BT Teoria e Exemplos de Cálculo Das Correntes de Curto Circuito TrifásicasDocumento9 páginasSubstações MT - BT Teoria e Exemplos de Cálculo Das Correntes de Curto Circuito TrifásicasIgor PROJAinda não há avaliações

- Mapa - Conversão Eletromecânica de Energia - 54 2023Documento3 páginasMapa - Conversão Eletromecânica de Energia - 54 2023Fabio GuimaraesAinda não há avaliações

- 14.material Curso Instalacoes IDocumento140 páginas14.material Curso Instalacoes ICARLOS BARBOSAAinda não há avaliações

- Prática Lab 01 - Capacitores em Regime ACDocumento5 páginasPrática Lab 01 - Capacitores em Regime ACJoão Paulo Araujo SantosAinda não há avaliações

- PROVA de Engheiro Eletricista Conhecimentos Especificos CEBRASPE 2015Documento6 páginasPROVA de Engheiro Eletricista Conhecimentos Especificos CEBRASPE 2015enps455Ainda não há avaliações

- 2022 Modelo VSC MMC Estabilidade EletromecanicaDocumento9 páginas2022 Modelo VSC MMC Estabilidade Eletromecanicarcc_caetaAinda não há avaliações

- 2023 Angle Difference Control Elos HVDC InseridosDocumento9 páginas2023 Angle Difference Control Elos HVDC Inseridosrcc_caetaAinda não há avaliações

- TAT Resolucao de ExerciciosDocumento9 páginasTAT Resolucao de ExerciciosArlindo Francisco NoveleAinda não há avaliações

- HVDC - Transporte de Energia Elétrica em Corrente ContínuaDocumento11 páginasHVDC - Transporte de Energia Elétrica em Corrente ContínuaAnderson Bairros100% (1)

- NoBreak 1 PDFDocumento11 páginasNoBreak 1 PDFmaxxagainAinda não há avaliações

- Curso Completo Reparação de MotherboardsDocumento116 páginasCurso Completo Reparação de Motherboardsdesportista_luisAinda não há avaliações

- Instalação e Configuração de Sistemas Windows: Mario Gerson Miranda Magno JuniorDocumento90 páginasInstalação e Configuração de Sistemas Windows: Mario Gerson Miranda Magno Juniorbenitez leonel borinelliAinda não há avaliações

- Apostila Matematica para Vencer 10 PDFDocumento153 páginasApostila Matematica para Vencer 10 PDFNuno André Diogo100% (2)

- UntitledDocumento642 páginasUntitledbenitez leonel borinelli100% (1)

- 4 Windows 2003 Guia CompletoDocumento178 páginas4 Windows 2003 Guia CompletoPaulo Roberto Sotto MaiorAinda não há avaliações

- Manutencao e Configuracao de Computadores - SenacDocumento204 páginasManutencao e Configuracao de Computadores - SenacMarco Zezinha LarissaAinda não há avaliações

- Arquitetura de ComputadoresDocumento126 páginasArquitetura de ComputadoresAndre DosciatiAinda não há avaliações

- Curso Completo Reparação de MotherboardsDocumento116 páginasCurso Completo Reparação de Motherboardsdesportista_luisAinda não há avaliações

- Questões Comentadas PM-DF: Ebook GrátisDocumento113 páginasQuestões Comentadas PM-DF: Ebook Grátisbenitez leonel borinelliAinda não há avaliações

- Recibo Do PagadorDocumento1 páginaRecibo Do Pagadorbenitez leonel borinelliAinda não há avaliações

- Laércio Vasconcelos - Eletronica BasicaDocumento50 páginasLaércio Vasconcelos - Eletronica BasicaHarringson Borges de AlbuquerqueAinda não há avaliações

- Circuito - de - Controle - Com - DSC - para - Ups - de 1Documento153 páginasCircuito - de - Controle - Com - DSC - para - Ups - de 1dofigueiredoAinda não há avaliações

- Resolvendo Problemas No SEU: MicroDocumento8 páginasResolvendo Problemas No SEU: Microbenitez leonel borinelliAinda não há avaliações

- Informática: Hardware e SoftwareDocumento88 páginasInformática: Hardware e Softwarebenitez leonel borinelli100% (1)

- Montagem e ManutençãoDocumento87 páginasMontagem e ManutençãoRafaell MczAinda não há avaliações

- UntitledDocumento21 páginasUntitledbenitez leonel borinelliAinda não há avaliações

- Memória RAMDocumento10 páginasMemória RAMbenitez leonel borinelliAinda não há avaliações

- Curso Técnico de HardwareDocumento689 páginasCurso Técnico de Hardwarebenitez leonel borinelliAinda não há avaliações

- Apostila Fundamentos de Eletrônica-Senai - (Poluidor - Blogspot.com)Documento158 páginasApostila Fundamentos de Eletrônica-Senai - (Poluidor - Blogspot.com)diegoealexandraAinda não há avaliações

- Escola Naval: Departamento de Engenheiros Navais Ramo de Armas E ElectrónicaDocumento40 páginasEscola Naval: Departamento de Engenheiros Navais Ramo de Armas E Electrónicabenitez leonel borinelliAinda não há avaliações

- Fundamentos Da MOSFET e Circuitos Driver PDFDocumento48 páginasFundamentos Da MOSFET e Circuitos Driver PDFRafael HbsAinda não há avaliações

- Teoria 6 Dispositivos Semicondutores de Potência Tiristores SCR, GTO, MCT e IGCTDocumento22 páginasTeoria 6 Dispositivos Semicondutores de Potência Tiristores SCR, GTO, MCT e IGCTbenitez leonel borinelliAinda não há avaliações

- Curso Técnico de HardwareDocumento689 páginasCurso Técnico de Hardwarebenitez leonel borinelliAinda não há avaliações

- Memória Ram: EspecialDocumento109 páginasMemória Ram: Especialbenitez leonel borinelliAinda não há avaliações

- Dic Info MorimotoDocumento398 páginasDic Info MorimotoPatrícia Varaschini PoetiniAinda não há avaliações

- Memória Ram: EspecialDocumento109 páginasMemória Ram: Especialbenitez leonel borinelliAinda não há avaliações

- Memória Ram: EspecialDocumento109 páginasMemória Ram: Especialbenitez leonel borinelliAinda não há avaliações

- Arquitetura de ComputadoresDocumento126 páginasArquitetura de ComputadoresAndre DosciatiAinda não há avaliações

- UntitledDocumento70 páginasUntitledbenitez leonel borinelliAinda não há avaliações

- TC04Documento0 páginaTC04Nicollas FreitasAinda não há avaliações

- Fundamentos para ComputaçãoDocumento16 páginasFundamentos para ComputaçãoMarcela CardinalAinda não há avaliações

- Manual E3Documento342 páginasManual E3atlas_offzz100% (1)

- Aula3 O ComputadorDocumento78 páginasAula3 O ComputadorDgeison Alexander CarvalhoAinda não há avaliações

- Apostila Extensão COBOLDocumento12 páginasApostila Extensão COBOLLord_EnigmaAinda não há avaliações

- Artigo Sobre Escalonamento de ProcessosDocumento12 páginasArtigo Sobre Escalonamento de ProcessosRenan Felipe0% (1)

- Notas SSCPDocumento37 páginasNotas SSCPScribdTranslationsAinda não há avaliações

- Team Viewer Manual PTDocumento99 páginasTeam Viewer Manual PTCarlos Evandro PizzinatAinda não há avaliações

- Aula 1Documento14 páginasAula 1ClaudioTRodriguesAinda não há avaliações

- Como Formatar e Instalar o Windows 7 Passo A PassoDocumento10 páginasComo Formatar e Instalar o Windows 7 Passo A PassoLuciaMouraAinda não há avaliações

- ManualDocumento122 páginasManualAnonymous fIQtTSl8bAinda não há avaliações

- Apostila PHPDocumento54 páginasApostila PHPFábioHenriqueAinda não há avaliações

- A-Classificacao de SoftwaresDocumento9 páginasA-Classificacao de SoftwaresFrancisco Manuel JoaoAinda não há avaliações

- Catalogo Fibra Optica2019 (1.0)Documento75 páginasCatalogo Fibra Optica2019 (1.0)Luis SilvaAinda não há avaliações

- Sony - Actualizações Da KDL-32EX310Documento4 páginasSony - Actualizações Da KDL-32EX310antvilaAinda não há avaliações

- Aula 04 Fusíveis e Mplab Renata MercanteDocumento14 páginasAula 04 Fusíveis e Mplab Renata MercanteDouglas Silva Dos Santos SouzaAinda não há avaliações

- Curriculum Do Marco AntonioDocumento1 páginaCurriculum Do Marco Antonioinstrutor.marcoAinda não há avaliações

- AfroDev Segunda SemanaDocumento155 páginasAfroDev Segunda SemanaZ. O.Ainda não há avaliações

- Ibercusa Manu Completo 002 PDFDocumento91 páginasIbercusa Manu Completo 002 PDFTiago JesusAinda não há avaliações

- Livro Digital 248 CLP Tema 2Documento11 páginasLivro Digital 248 CLP Tema 2Brasilio Cortes GuimaraesAinda não há avaliações

- Threads - AtividadeDocumento2 páginasThreads - AtividadeKarolyne MunizAinda não há avaliações

- Manual - WEG HMI APSDocumento10 páginasManual - WEG HMI APSMarcelo LescanoAinda não há avaliações

- Esquema ProcessadorDocumento1 páginaEsquema ProcessadorJuan SilvaAinda não há avaliações

- Manual Atos Expert BFDocumento39 páginasManual Atos Expert BFOseias Codignola0% (1)

- Manual Geovision V8.3Documento486 páginasManual Geovision V8.3Sergio Junior100% (2)